Поиск

Показаны результаты для тегов 'axi xilinx'.

-

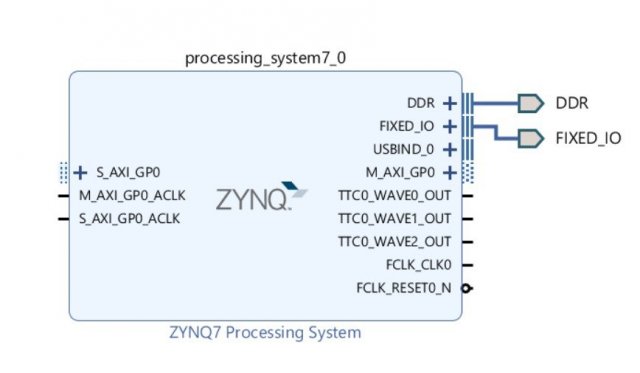

Я написал функцию "memcpy" для копирования блока данных с исходного адреса на адрес назначения. Хочу протестировать на плате (Zynq). Я новичок в MCU и изучаю эту тему самостоятельно, извините, если мой вопрос для вас глупый. Что я сделал: Я создал проект в vivado, начал block design с Zynq, изменил конфигурацию PS-PL (добавил GP Master и Slave AXI Interface) [Смотри приложение]. Я читал, что Zynq может быть Master, но Slave/ периферийнoe устройство я должен спроектировать как настраиваемое IP-ядро. Я уже нашел, как создать собственный AXI IP (slave или master). Vivado создает шаблон настраиваемого IP-ядра (slave). (1) Могу ли я использовать этот шаблон без каких-либо изменений? (2) Следует ли мне добавить дополнительную информацию (сигналы, которые я использую в функции memcpy: адреса и количество битов)? Я пропустил дизайн custom master . (3) Я сделал правильно или мастер должен быть частью настраиваемого IP ядра?

-

помогите разобраться с AXI lite

Drakonof опубликовал тема в Работаем с ПЛИС, области применения, выбор

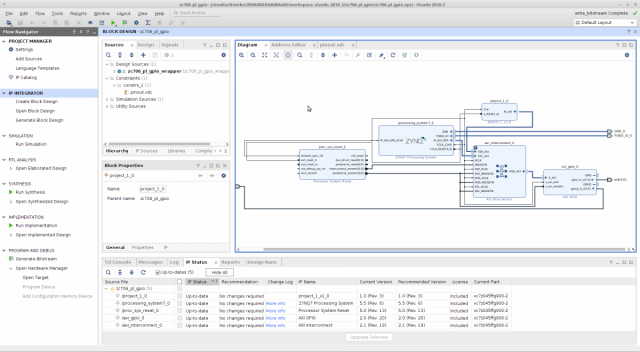

Всем привет, друзья помогите разобраться с AXI lite. Vivado 2018.3, linux mint Для начала, думаю можно просто зажечь диоды(их всего 4) на платке с помощью axi_gpio ip и моего контроллера, который пока не работает. Кто знает, может подскажет где ошибка. Диоды исправные, назначены верно, частота подается. Спасибо `timescale 1 ns / 1 ps module project_1 # ( parameter integer C_M_AXI_ADDR_WIDTH = 32, parameter integer C_M_AXI_DATA_WIDTH = 32 ) ( input wire CLK, input wire A_RESET_N, output wire [C_M_AXI_ADDR_WIDTH-1 : 0] M_AXI_AWADDR, output wire [2 : 0] M_AXI_AWPROT, output wire M_AXI_AWVALID, input wire M_AXI_AWREADY, output wire [C_M_AXI_DATA_WIDTH-1 : 0] M_AXI_WDATA, output wire [C_M_AXI_DATA_WIDTH/8-1 : 0] M_AXI_WSTRB, output wire M_AXI_WVALID, input wire M_AXI_WREADY, input wire [1 : 0] M_AXI_BRESP, input wire M_AXI_BVALID, output wire M_AXI_BREADY, output wire [C_M_AXI_ADDR_WIDTH-1 : 0] M_AXI_ARADDR, output wire [2 : 0] M_AXI_ARPROT, output wire M_AXI_ARVALID, input wire M_AXI_ARREADY, input wire [C_M_AXI_DATA_WIDTH-1 : 0] M_AXI_RDATA, input wire [1 : 0] M_AXI_RRESP, input wire M_AXI_RVALID, output wire M_AXI_RREADY ); reg axi_awvalid; reg axi_wvalid; reg [C_M_AXI_DATA_WIDTH-1 : 0] axi_ardata; reg start_single_read; reg start_resp_read; reg axi_arvalid; reg axi_rready; reg axi_bready; assign M_AXI_BREADY = axi_bready; assign M_AXI_RREADY = axi_rready; // адрес на axi, он же регистр данных порта 1 axi_gpio assign M_AXI_AWADDR = 32'h40000000; // записать в регистр данных порта gpio 1 данные, значение должно загореться на диодах assign M_AXI_WDATA = 32'h0000000A; assign M_AXI_AWPROT = 3'b000; assign M_AXI_AWVALID = axi_awvalid; assign M_AXI_WVALID = axi_wvalid; assign M_AXI_WSTRB = 4'b1111; always @(posedge CLK) begin if (A_RESET_N == 0) begin axi_awvalid <= 1'b0; axi_wvalid <= 1'b0; end else begin axi_awvalid <= 1'b1; axi_wvalid <= 1'b1; if (M_AXI_AWREADY && axi_awvalid) begin axi_awvalid <= 1'b0; start_single_read <= 1'b1; end if (M_AXI_WREADY && axi_wvalid) begin axi_wvalid <= 1'b0; end end end always @(posedge CLK) begin if (A_RESET_N == 0) begin axi_bready <= 1'b0; end else if (M_AXI_BVALID && ~axi_bready) begin axi_bready <= 1'b1; end else if (axi_bready) begin axi_bready <= 1'b0; end ; end assign M_AXI_ARADDR = 32'h40000008; assign M_AXI_ARPROT = 3'b001; assign M_AXI_ARVALID = axi_arvalid; always @(posedge CLK) begin if (A_RESET_N == 0) begin axi_arvalid <= 1'b0; end else if (start_single_read) begin axi_arvalid <= 1'b1; end else if (M_AXI_ARREADY && axi_arvalid) begin axi_arvalid <= 1'b0; end end always @(posedge CLK) begin if (M_AXI_RVALID && ~axi_arvalid) begin axi_ardata <= M_AXI_RDATA; end end always @(posedge CLK) begin if (A_RESET_N == 0 ) begin axi_rready <= 1'b0; end else if (M_AXI_RVALID && ~axi_rready) begin axi_rready <= 1'b0; end else if (axi_rready) begin axi_rready <= 1'b0; end end endmodule -

Начал новый проект, решил сразу разделить GPIO на внутренние и на внешние. Присоединил один модуль GPIO на шину и отвел по одному каналу на внутренние и внешние. При объявлении внешних выходов XPS предлагает входы(_I), выходы(_O), и двунаправленные (_IO). Я считал, что можно сделать 64 входа и 64 выхода на одном экземпляре IP Logic Core. С первым каналом вопросов пока нет. Со второго канала вывел две шины по 32 бита, назначил выводы на вход и выход. Собрал проект и зашил в ПЛИС. Управление светодиодами идет нормально, прием от кнопок не работает. Проверил прохождение тестером прохождение уровней сигналов до ПЛИС - уровни меняются. Перепроверил проект - ошибок не нашел. Решил перечитать документацию: https://www.xilinx.com/support/documentation/ip_documentation/axi_gpio/v1_01_b/ds744_axi_gpio.pdf "Figure 2: GPIO Core Dual-Channel Implementation" показывает, что на выход идет только I/O и его нужно программировать. Получается, что в каждом канале можно задействовать только 32 бита и конфигурировать их по желанию I/O/IO?