-

Постов

78 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о Kronac

-

Звание

Частый гость

Посетители профиля

974 просмотра профиля

-

Да "полностью одинаковая" - это такая же как на не рабочей паре. Вот я наложил Осциллограмму сигнала Клока с одной пары FMC на сигнал другой пары FMC. Сами сигналы SPI одни и те же. Но если убрать с этой пары сигнал SDI на какой либо другой контакт рядом, становится всё хорошо... Спасибо, попробую Ваше предложение.

-

Для теста сделал проект, где одни и те же сигналы SPI выведены на разные пары на разъёме FMC. Картинка полностью одинаковая. Но если я развязываю SCLK и SDI на разные пары (используя по одному сигналу из пары), то картинка прекрасная - Хороший клок, хорошие данные. На сколько я могу судить, замыкания нет, ПЛИС не повреждена.

-

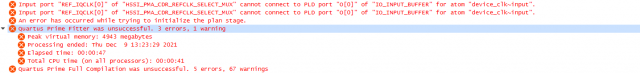

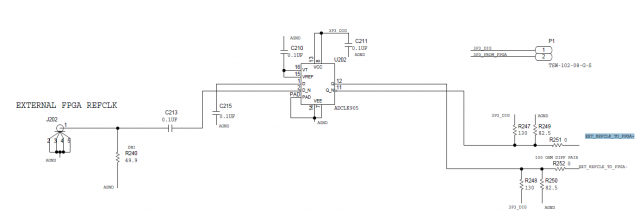

Захотелось поднять JESD на двух КИТах ZCU102 (Zynq Ultrascale+) и АЦП AD9695 1300EBZ Eval соединив их по FMC. С проектом никаких сложностей не возникло, ядра все быстро настроил, принялся работать, но микруха AD9695 молчит по SPI и никаких признаков жизни не подаёт. Стандарты протокола, сигналов и распиновку перепроверил много раз, проблем не увидел. На мезонине есть чудесная возможность отладки SPI через контрольные точки Осциллом, ей и воспользовался. Рис.1 - Часть схемы AD9695 Eval Ткнулся в контрольные точки и увидел странную картину. Сигналы "SDI_from_FPGA" и "SCLK_FROM FPGA" накладываются друг на друга и мешают корректно друг другу работать. Когда на шине SDI есть данные (уровень "1"), Клок на SCLK задирается и портится... Рис.2,3 - Осциллограммы на тестовых пинах (Сверху SCLK, снизу SDI); При этом сам клок фонит на данные превращая их в кашу. Рассмотрел более подробно схему и понял, что эти два пина являются ДИФФ парой на разъёме FMC (LA01_P_CC/LA01_N_CC) Рис.4 - Часть схемы AD9695 Eval (FMC) Думал в начале может проблема в настройках VIVADO и как то случайно поставил стандарт не тот на эти выводы, но нет. Стандарт явно обозначен "LVCMOS18" у всех пинов SPI. Залез на всякий случай в схематик в имплементации, там всё верно стоит на выходе "OBUF". О Дифференциальном выходе и речи нет... Кто знает, почему соседние сигналы могут портить друг друга? и что можно с этим сделать? Рис.5 - Мои настройки для пинов SPI в VIVADO Рис.6 - Схематик из VIVADO; PS: На всякий случай ещё уточню, что проблема точно не в мезонине или его разводке. Мезонин снимал и смотрел щупами прямо на FMC разъёме со стороны ZCU102. Картинка та-же. Такими сигналы идут из ПЛИС.

-

Спасибо, попробую Всё подошло, именно то, что нужно. Спасибо большое!

- 6 ответов

-

- 1

-

-

- ticspro-sw

- lmk04010

-

(и ещё 2 )

C тегом:

-

Собираю систему из нескольких АЦП на плате с интерфейсом передачи данных JESD204B. ПЛИС SoC Zynq UltraScale+. После тщательного анализа и подбора компонентов, было принято решение использовать клоковый дистрибьютор LMK04610 для формирования опорных частот и сигналов Sysref. Эта микросхема подходит по всем требуемым параметрам и она одна из немногих, которая свободно покупается сейчас в РФ. Когда я работал с похожими микрухами от Analog Devices, я всегда использовал их базовое ПО для оценочных плат, которое позволяет моментально разобраться в регистрах микросхемы, её режимах, в считанные минуты указать все необходимые для работы режимы и получить полную карту регистров, которые необходимо прописать в микросхему. У Texas Instruments есть точно такое же ПО (TICSPRO-SW), которое я очень хочу скачать для быстрого освоения микросхемы, но перепробовал уже все возможные способы и не выходит. Сайт "ti com" Просто не позволяет скачивать ПО без регистрации, но зарегистрироваться на почту созданную в России нельзя (даже на почту домена GOOGLE). При регистрации просто не приходит письмо подтверждения почты. Мой вопрос, может ли кто то помочь скачать на сайте "ti com" программу TICSPRO-SW"? Или может быть подскажете как это можно сделать. Пробовал уже и под VPN создавать почту.. не работает, просто не приходит письмо подтверждения.

- 6 ответов

-

- ticspro-sw

- lmk04010

-

(и ещё 2 )

C тегом:

-

Я в своей работе не моделирую ядра PLL, PCIe, JESD, DDR и прочие.. Ибо этот процесс моделирования будет занимать очень очень много времени.. Я проверяю свою логику, которую пишу лично я, эмулируя подачу сигналов и поведение ядер в идеальных условиях так сказать написанием простенькой симуляционной модели на базе спецификаций ядер. Но на практике часто выясняется, что какой либо сигнал становится на два такта раньше или на 10 тактов позже, чем я ожидал на модели. Я ввожу корректировки, перекомпиливаю и всё работает. В этом SIGNAL TAP очень сильно помогает и ускоряет в разы стадию отладки. Можно конечно заморочиться и отмоделировать поведение каждого ядра, каждого сигнала во всём проекте, но этот процесс заберёт очень много времени и не известно сколько ресурсов компьютера... Я понимаю, что сам SIGNAL TAP (и ILA) не залог достоверности захваченных данных. Ни раз сталкивался с тем, что сигнал просто не захватывался, инвертировался или вовсе вёл себя непредсказуемо. Это я понимаю. Я не понимаю как "эффект наблюдателя" ломает сам процесс работы. Пытаясь заглянуть во внутренние процессы через ILA, я нарушаю тем самым эти процессы и много что начинает отрабатываться неверно или вовсе зависает внутри ПЛИС...

-

Всем привет. Много работал ранее с проектами в среде QUARTUS, очень часто приходилось отлаживать проекты в железе при помощи встроенного логического анализатора Signal Tap II. Очень удобный инструмент, ни один раз помогал мне найти и выявить ошибки, пропущенные на стадии моделирования и некоторые моменты, которые моделирование в принципе не способно обнаружить. В данный момент создаю проект в Xilinx Vivado, где на ПЛИС принимаю по JESD отчёты из АЦП, провожу некоторую обработку данных и кладу в память. Столкнулся с ситуацией, что на модели всё идеально, никаких проблем нет, но в железе не работает должным образом моя внутренняя логика (при этом приём сигнала с АЦП по JESD в норме). Стал разбираться, с помощью ядер ILA выводить интересующие меня сигналы JESD, флаги и статусы для анализа. Первая проблема, с которой я столкнулся, не могу завести ядра на частоте, которой изначально нет в ПЛИС (в момент подачи питания). Частота появляется с программируемого генератора позже и САПР Vivado говорит мне, что не может запустить ядро ILA и показать результаты... Пришлось перебрасывать все нужные мне сигналы через три регистра на стабильный клок (от DDR у меня есть 300МГц, которые всегда поступают в ПЛИС). ILA запускается, но тут начинается танец с бубном. У меня либо совсем умрёт JESD, что перестают корректно приниматься данные, либо работает но данные бьются. Причём бьются не те данные, которые я вывел на ILA, а реальные отчёты АЦП, поступающие в память. Лечится эта штука путём полного сброса проекта (команда "reset_project" TCL) и 1-2 перекомпиляции, не меняя исходников или настроек. В итоге этот процесс очень сильно стопорит процесс отладки. После каждых изменений в проекте, приходится танцевать с бубном и надеяться, что после 2-3 перекомпиляций проект получится рабочий, JESD запустится и ILA ему мешать не будет. Прошу помощи у более опытных пользователей. Как вы работаете с ILA? Как тестируете работоспособность проекта в железе на xilinx?

-

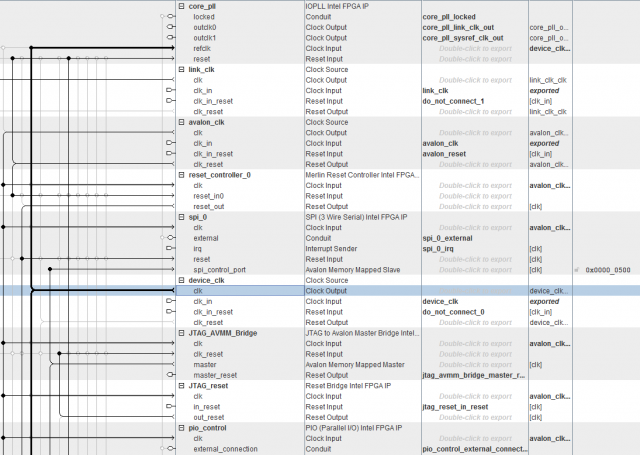

Спасибо большое. Прочитал мануал подробнее. Сначала получилось подать клок через каскадирование ПЛЛ-ек. Входной пин завёл на стандартную IOpll, её выход уже подал на fPLL. Подход интересный, но боюсь представить что станет с клоком, когда он пройдёт весь этот тракт.. Долго бился над тем, чтобы подать пин напрямую на вход fractional PLL. В мануале такая возможность действительно имеется, но Квартус отчаянно сопротивлялся =)... Потом уже в другом мануале (хэндбук на Аррию 10) нашёл, что мне нужно использовать между входным пином и fPLL "ALTCLKCTRL" и только после этого квартус съел это всё и компильнулся. Не знаю на сколько это работоспособно, но то, что это компилится уже радует. Теперь у меня есть запасной план, на случай если не будет трансиверного клока.

-

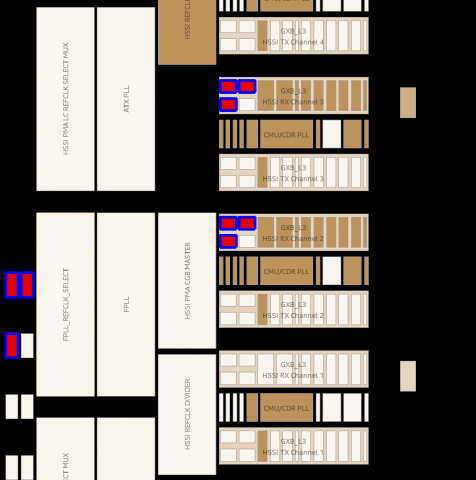

Посмотрел в Chip Planner Arria V и мою Arria 10. Действительно в старой арии не было высокоскоростных ATX PLL / fPLL. Были только обычные PLL которые были прям у трансиверов, что позволяло такой подход и можно было завести на клоки ПЛЛек и всё было хорошо. К сожалению у новых Arria 10 всё совсем иначе и работать с трансиверами или ATX PLL/fPLL можно исключительно используя высокоскоростные трансиверные клоки...

-

Интересно.. Ну я до этого пытался напрямую клок подать без ПЛЛ сразу в ядро с пина (пропустив через Clock_Source) . Сейчас попробовал этот вариант, пропустить клок через ПЛЛ и ничего не меняя с той же частотой подать на ядро JESD, но результат тот же, что и раньше.. (ядро JESD одно у меня) Возможно в Арии 10 что то поменялось в этом плане... =) А какой тип ПЛЛ при этом у Вас был? может я не ту ПЛЛ поставил или не так настроил её? Я ставил стандартную IOPLL.

-

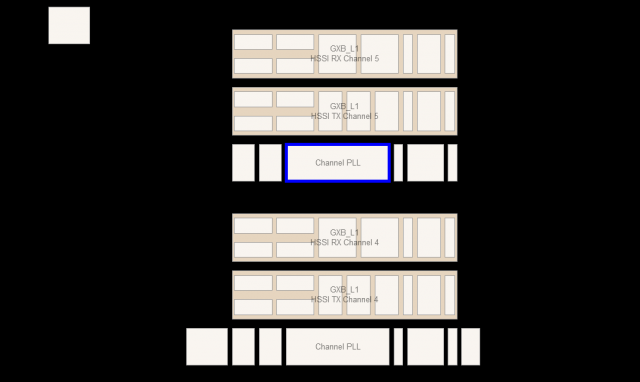

Можно спросить, как у Вас это вышло? Для интереса убрал из проекта ПЛЛ, клок с пина напрямую подаю в ядро JESD, попробовал все клоки, какие есть на моей ARRIA 10, если клок не является трансиверным выделенным клоком (на рисунке синим выделены), то какой бы клок или стандарт я не использовал, Quartus не разрешает такую разводку...

-

Ну при попытке в лоб подменить пин pll_ref_clk для JESD на старом проекте, квартус выдал сразу ошибку... Буду сейчас разбираться что не так.. В моём проекте входной пин "device_clk" с высокоскоростного входа шёл в ip ядро JESD и на PLLку где я формировал с него link_clk и sysref. С высокоскоростным пином такая штука работала, с обычным по ходу квартус так не может.. =)

-

Спасибо, попробую конечно, но раньше когда пробовал подобный трюк, компилятор (что Quartus, что vivado) меня сразу посылал. Передвинуть, перепаять, допаять конечно всегда можно, но это уже второй шаг, когда других вариантов уже не будет =) Пока хочется отделаться малой кровью.

-

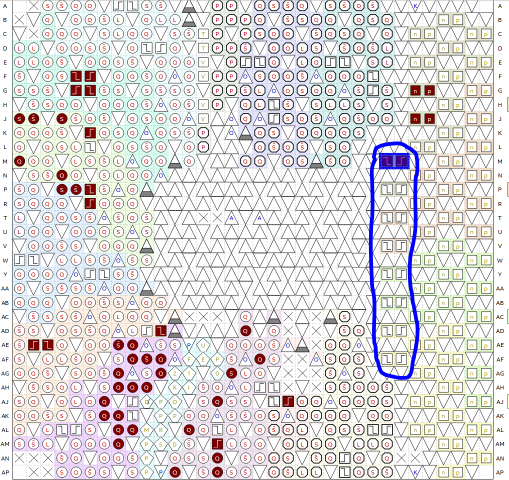

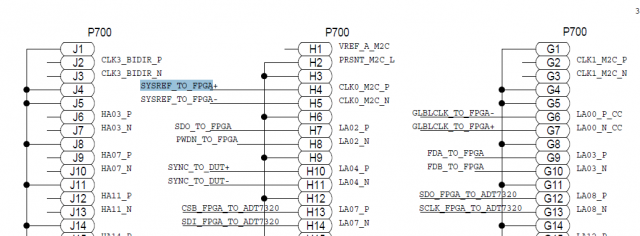

Прозвонить, к сожалению, пока не могу, так как кит ещё не куплен. Сейчас на стадии закупки и вот неожиданно возник вопрос, подойдёт ли данный кит? Или с ним не выйдет работать так, как задумывалось изначально... Обнаружил странный момент на схеме, по этому собственно и создал данную тему. По поводу использования SYSREF_TO_FPGA, он подключён на клоковый вход "CLK0_M2C" на FMC, но всё же это не высокоскоростной вход для трансиверных клоков. Компилятор такое не съест, на сколько я знаю... Уточню ещё. Сложность в том, что в системе, в которой собираюсь использовать AD9208 EVAL, на плате носителе с ПЛИС нет возможности подать хоть какие то сигналы из вне (штатными способами, без конструктивной переделки), имеются только FMC коннекторы, по этому сигналы SYSREF и PHY_CLK для JESD намеревался получать от мезонина через FMC...

-

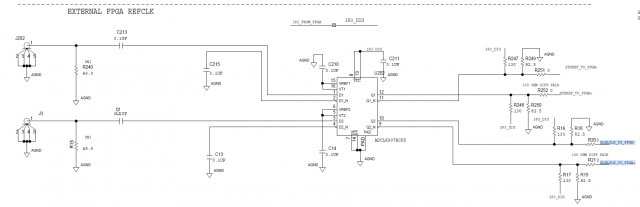

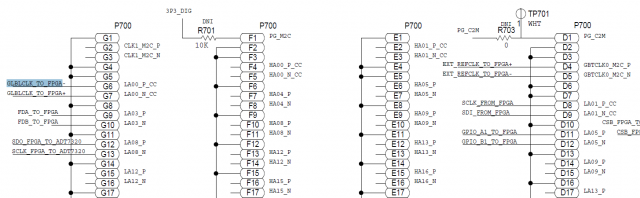

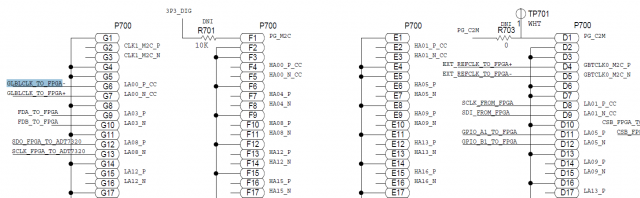

Всем привет. Успешно использовал для приёма в ПЛИС сигналов от мезонина AD9695 EVAL. Были свои минусы модели (не было возможности пропустить через FMC в ПЛИС сигнал sysref). Назрела необходимость использовать другой замечательный КИТ от Analog DEVICES - AD9208 3000EBZ EVAL. Посмотрел все необходимые характеристики, всё устраивает, даже появилась возможность сигнал sysref прогнать через мезонин и пустить в ПЛИС. Начал копаться более глубоко, нашёл схематик и там столкнулся с очень странным моментом. На моём старом ките, для работы трансиверов JESD можно было подать на входной коннектор SMA на мезонине сигнал "EXT_REFCLK_TO_FPGA" и пропустить его через FMC на ножку "GBTCLK0_M2C_P", после чего благополучно в ядре назначить его как PHY CLK для трансиверов (Рис.1). Рис.1 На новый КИТ AD9208 EVAl на сайте Analog DEVICES я скачал архив файлов, там был схематик для AD9689 EVAL, как я понял это совместимый пин в пин с моим АЦП и плата носитель у них одна. Так вот в скаченном схематике немного изменилась схема. Входной клок для ПЛИС с коннектора на мезонине теперь называется "GLBLCLK_TO_FPGA" (Рис.2) Рис.2 Подключается же данный сигнал на ножку "LA00_P_CC" на разъёме FMC (Рис.3), который не является высокоскоростным входом для тактирования трансиверов JESD ... Подключить его к JESD, я думаю, мне компилятор не позволит.. Интересно то, что старый сигнал "EXT_REFCLK_TO_FPGA" остался на старом "правильном" месте, но при этом он обрублен и больше никуда по схеме не идёт... Рис.3 Так вот мой вопрос. Это какая то опечатка, ошибка на схеме? Или реально так перелопатили КИТ, что теперь брать клок через мезонин невозможно? Приложу обе схемы: старого кита AD9695 и нового AD9208 (AD9689 так как это одно и тоже). SCH_9695ce01a.pdf SCH_9689ce02c.pdf