Поиск

Показаны результаты для тегов 'jesd'.

-

Всем привет. Много работал ранее с проектами в среде QUARTUS, очень часто приходилось отлаживать проекты в железе при помощи встроенного логического анализатора Signal Tap II. Очень удобный инструмент, ни один раз помогал мне найти и выявить ошибки, пропущенные на стадии моделирования и некоторые моменты, которые моделирование в принципе не способно обнаружить. В данный момент создаю проект в Xilinx Vivado, где на ПЛИС принимаю по JESD отчёты из АЦП, провожу некоторую обработку данных и кладу в память. Столкнулся с ситуацией, что на модели всё идеально, никаких проблем нет, но в железе не работает должным образом моя внутренняя логика (при этом приём сигнала с АЦП по JESD в норме). Стал разбираться, с помощью ядер ILA выводить интересующие меня сигналы JESD, флаги и статусы для анализа. Первая проблема, с которой я столкнулся, не могу завести ядра на частоте, которой изначально нет в ПЛИС (в момент подачи питания). Частота появляется с программируемого генератора позже и САПР Vivado говорит мне, что не может запустить ядро ILA и показать результаты... Пришлось перебрасывать все нужные мне сигналы через три регистра на стабильный клок (от DDR у меня есть 300МГц, которые всегда поступают в ПЛИС). ILA запускается, но тут начинается танец с бубном. У меня либо совсем умрёт JESD, что перестают корректно приниматься данные, либо работает но данные бьются. Причём бьются не те данные, которые я вывел на ILA, а реальные отчёты АЦП, поступающие в память. Лечится эта штука путём полного сброса проекта (команда "reset_project" TCL) и 1-2 перекомпиляции, не меняя исходников или настроек. В итоге этот процесс очень сильно стопорит процесс отладки. После каждых изменений в проекте, приходится танцевать с бубном и надеяться, что после 2-3 перекомпиляций проект получится рабочий, JESD запустится и ILA ему мешать не будет. Прошу помощи у более опытных пользователей. Как вы работаете с ILA? Как тестируете работоспособность проекта в железе на xilinx?

-

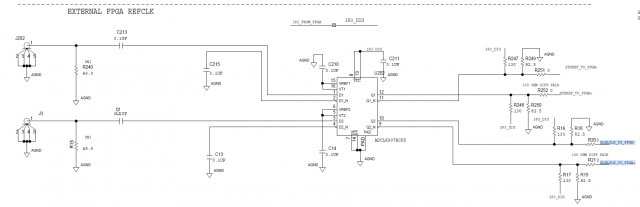

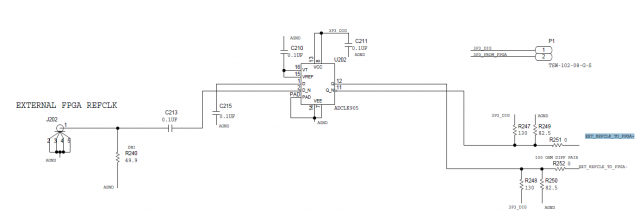

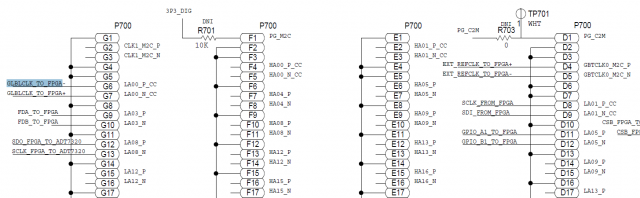

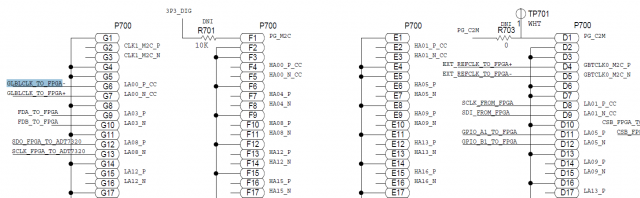

Всем привет. Успешно использовал для приёма в ПЛИС сигналов от мезонина AD9695 EVAL. Были свои минусы модели (не было возможности пропустить через FMC в ПЛИС сигнал sysref). Назрела необходимость использовать другой замечательный КИТ от Analog DEVICES - AD9208 3000EBZ EVAL. Посмотрел все необходимые характеристики, всё устраивает, даже появилась возможность сигнал sysref прогнать через мезонин и пустить в ПЛИС. Начал копаться более глубоко, нашёл схематик и там столкнулся с очень странным моментом. На моём старом ките, для работы трансиверов JESD можно было подать на входной коннектор SMA на мезонине сигнал "EXT_REFCLK_TO_FPGA" и пропустить его через FMC на ножку "GBTCLK0_M2C_P", после чего благополучно в ядре назначить его как PHY CLK для трансиверов (Рис.1). Рис.1 На новый КИТ AD9208 EVAl на сайте Analog DEVICES я скачал архив файлов, там был схематик для AD9689 EVAL, как я понял это совместимый пин в пин с моим АЦП и плата носитель у них одна. Так вот в скаченном схематике немного изменилась схема. Входной клок для ПЛИС с коннектора на мезонине теперь называется "GLBLCLK_TO_FPGA" (Рис.2) Рис.2 Подключается же данный сигнал на ножку "LA00_P_CC" на разъёме FMC (Рис.3), который не является высокоскоростным входом для тактирования трансиверов JESD ... Подключить его к JESD, я думаю, мне компилятор не позволит.. Интересно то, что старый сигнал "EXT_REFCLK_TO_FPGA" остался на старом "правильном" месте, но при этом он обрублен и больше никуда по схеме не идёт... Рис.3 Так вот мой вопрос. Это какая то опечатка, ошибка на схеме? Или реально так перелопатили КИТ, что теперь брать клок через мезонин невозможно? Приложу обе схемы: старого кита AD9695 и нового AD9208 (AD9689 так как это одно и тоже). SCH_9695ce01a.pdf SCH_9689ce02c.pdf