Поиск

Показаны результаты для тегов 'sdram'.

-

Компания Alliance Memory объявила о расширении своего портфолио CMOS DDR4 SDRAM новыми «A» версиями микросхем объёмом 4 Гбит в 96- и 78-шариковых корпусах FBGA соответственно – серии AS4C256M16D4 и AS4C512M8D4. Подробнее

-

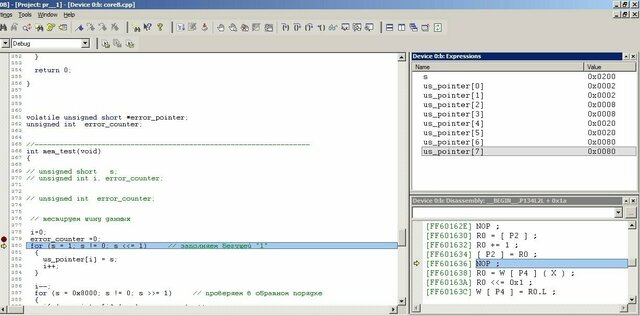

Использовали плату BF561 с одним модулем памяти на 64 мегабайта 16 бит. Для нее был написан простенький тест памяти. Сейчас плату переразвели на 2 микросхемы памяти. В результате получили те же 64 мегабайта, но шина данных 32 бита. Залил старую программу - ростейший тест с бекущей "1" по шине данных не идет. Заполняет память как на картинке. Взял документ EE-326 "Blackfin® Processor and SDRAM Technology" Перепроверил схему на соответствие рекомендациям - все соответствует. Поискал информацию, как переключить шину 16 на 32 - не нашел. Есть рекомендации по настройке линкера, при размещении данных в SDRAM. Но в тестирующей программе размещение данных/кода в SDRAM не используется. Вот функция инициализации SDRAM контроллера void sdram_config() { unsigned int mem_SDRRC; unsigned int mem_SDGCTL = SCTLE | CL_3 | TRAS_6 | TRP_3 | TRCD_3 | TWR_2 | PSS | FBBRW | 0x80000000; // calculating EBIU_SDRRC double t_ref = 64 * 1e-3; double sclk = ((double) get_sclk()); // Hz unsigned int row_number = 13; unsigned short t_ras = (mem_SDGCTL >> 6) & 0xF; unsigned short t_rp = (mem_SDGCTL >> 11) & 0x7; mem_SDRRC = (sclk * t_ref) / (1 << row_number) - (t_ras + t_rp); // disable SDRAM Bank0 *pEBIU_SDGCTL &= 0xFFFFFFFE; *pEBIU_SDRRC = mem_SDRRC; *pEBIU_SDBCTL = EB0_E | EB0_SZ_64 | EB0_CAW_10; *pEBIU_SDGCTL = mem_SDGCTL; } Ну и извечных два вопроса: Кто виноват, что делать?

-

LPDDR4X SDRAM на 8 Гб от Alliance Memory

МакроГрупп опубликовал тема в Объявления пользователей

Компания Alliance Memory выпустила микросхему памяти LPDDR4X со встроенным ECC, расширив ассортимент высокоскоростных мобильных CMOS с низким энергопотреблением. Являясь расширением SDRAM четвертого поколения LPDDR4, микросхема AS4C256M32MD4V-062BAN имеет на 50% меньшее энергопотребление по сравнению с предыдущим поколением. Подробнее -

Добрый день. Использую C674x в связке с внешней SDRAM: организация памяти 32M x 16 (64 МБ), 4 банка памяти, одна страница памяти 1024 байт (10 бит). Кеш L1D, L1P и L2 включены, регионы кеширования MAR для адресов 0xC0000000 ... 0xC3FFFFFF (все 64 МБ) включены в регистрах. Программа выполняется из этой SDRAM, много данных (на несколько МБ), кода - несколько сотен килобайт (от 500 кБ). Активно используется выделения памяти из кучи (через memalign(128,x) ) - указатели выровнены на длину строки кеша L2 (максимальная длина) - 128 байт. Вопрос собственно вот в чём: есть ли смысл привязываться к банкам SDRAM для ускорения доступа к данным? Например - стек - в одном банке, куча - в другом, Zero-Init, UnInit - в третьем, код (.text) - в четвёртом? Или это ничего не даст? Прилагаю файл для линковщика - с расписанными секциями и регионами памяти, который сейчас используется. Программа стартует с самого начала SDRAM 0xC0000000: #define SDRAM_BASE 0xC0000000 #define SDRAM_SIZE 0x04000000 // 64 MB #define RO_SIZE 0x00098000 // <512 kB -c -stack 0x01700000 -heap 0x02800000 MEMORY { RO o = SDRAM_BASE l = RO_SIZE RW o = SDRAM_BASE+RO_SIZE l = SDRAM_SIZE-RO_SIZE } SECTIONS { .text:_c_int00* > SDRAM_BASE .text > RO .const > RO .switch > RO .cinit > RO .rodata > RO .init_array > RO //C++ .sysmem > RW .far > RW .stack > RW .bss > RW .neardata > RW .fardata > RW }

-

Производитель Alliance Memory анонсировал выпуск микросхем на 8 Гбит, которые полностью pin-to-pin совместимы со снятыми с производства микросхемами single-die DDR3L SDRAM на 8 Гбит от Micron – Dual-Die DDR3L SDRAM. Ключевые характеристики AS4C1G8D3LA и AS4C512M16D3LA: • скорость передачи данных: 1866 Мбит/с • тактовая частота: 933 МГц • работа от одного источника питания 1,35 В с обратной совместимостью до 1,5 В • температурные диапазоны: коммерческий (от 0 до +95 °C), индустриальный (от -40 до +95 °C) и автомобильный (от -40 до + 105°C) • корпуса: 78-Ball и 96-Ball FBGA Благодаря Alliance Memory заказчикам не придется искать альтернативные решения и вкладываться в переразводку платы. Новые микросхемы Dual-Die DDR3L SDRAM на 8 Гбит находятся в серийном производстве и доступны в качестве образцов заказчикам в России. Компания Макро Групп является официальным дистрибьютором продукции Alliance Memory в России. Источник

-

Проблема подключения sdram к stm32

Nowsan опубликовал тема в Разрабатываем ПП в САПР - PCB development

Имеется плата с микроконтроллером STM32F769II и микросхемой sdram MT48LC4M16A2. Прошил мк тестовой программой. В ней на sdram записывается информация из одного буфера, а затем читается в другой. Проблема в том, что этого не происходит, второй буфер остаётся пустой. Сигналов WE и CS с помощью логического анализатора (макс. 24 МГц) не увидел. Простым "ногодрыгом" удостоверился, что ножки МК в принципе живые. Вопрос такой, может ли в данном случае неграмотная разводка платы (а в том, что она неграмотная сомневаться не приходиться) сделать устройство полностью неработоспособным. Устройство разведено на 4-х слойной печатной плате. В основном вся разводка выполнена на внутренних слоях, а значит почти у всех дорожек есть два переходных отверстия. Верхние два слоя залиты, насколько возможно, GND полигонами, два нижних слоя залиты VCC полигонами. Ещё есть такой момент, уже не касательно разводки ПП. Я заметил что всех отладочных платах от STM для тактирования МК используется кварц на 25 МГц, я же использую 10 МГц, при этом скорректировав все делители и умножители так, чтобы тактирование ядра и FMC совпадало с примерами, но вдруг всё же мистическим образом это не правильно и нужно использовать именно 25 МГц? -

SDRAM - задержка первого чтения.

vitaly_n опубликовал тема в Цифровые схемы, высокоскоростные ЦС

Имеется плата - FPGA Spartan 6 LX9, к ней присобачена SDRAM IS42S81600F-7TL. Частота CLK 128 МГц, CL=3, BL=1. Режим работы такой - прилетают данные, их записываем в SDRAM, вместо них вычитываем из SDRAM другие данные. Пока пакетов данных нет - крутим AUTOREFRESH с периодом примерно 90 нс. Столкнулся с вот какой неприятной проблемой - первое чтение после авторефреша почему-то задерживается - шина DQ из третьего состояния переходит в активное с опозданием, в результате я читаю не то, что должно быть прочитано, а то, что осталось висеть на шине после предыдущей записи. Потом идут ещё 300 с лишним циклов записи-чтения, они пишутся и читаются идеально, без вопросов. Проблема только с первым чтением после простоя, заполненного авторефрешами. Сдвигаю фазу клока стробирования чтения - становится заметно лучше, но не насовсем. Если при нулевой задержке все первые чтения неверные (но последующие чтения правильные!), то при задержке 1.9 нс неверных чтений остаётся где-то четверть, при задержке 2.9 нс неверных чтений процентов 10, задержка 3.9 нс - это уже перебор. Кто сталкивался с чем-то подобным? -

Проект на LPC1788 + SDRAM. Необходимо в ходе работы изменить тактовую частоту CPU. Так как SDRAM тактируется от клока CPU (с делителем /1 или /2), то и частота SDRAM поменяется. А значит - необходимо заново проинитить контроллер SDRAM (EMC). Но нужно это сделать не потеряв содержимого SDRAM. А в даташите указано, что значения регистров управления EMC можно изменять только если EMC disabled или находится в idle. Правильно ли я понимаю, что для этого достаточно обеспечить чтобы: 1) дождаться статуса "EMC is idle" в регистре EMC.STATUS; 2) установить бит "Low-power mode" в регистре EMC.CONTROL; 3) перестроить частоту CPU (PLL и т.п.) обспечив, чтобы в течение этого времени не было выборок кода или данных из SDRAM или прочих обращений к ней; 4) переинитить EMC для нового значения клока; 5) сбросить бит "Low-power mode" в регистре EMC.CONTROL. Будет-ли производиться refresh памяти в течение пунктов 1...5? Или может у кого-то есть правильная процедура переиницализации EMC для LPC17xx без потери данных в SDRAM?

- 13 ответов

.jpg.f84f482ed0f7fac9dae6e0d63a167b4c.jpg)