petrov

Свой-

Постов

2 760 -

Зарегистрирован

-

Победитель дней

3

Весь контент petrov

-

интуитивно подозреваю, что нужно чтобы 2 точки были правее и 2 точки левее Именно, для точек посередине линии задержки больше всего информации для интерполяции. Использовал только с оптимальным диапазоном 0..1. не могли бы Вы привести ссылку, на модель в которой нет ошибки? Таких нет, во всех какие-то ошибки. :) Посмотрите более поздние. https://electronix.ru/forum/index.php?app=forums&module=forums&controller=topic&id=23652&page=11&tab=comments#comment-1366022

-

Пробы HDL на Simulink

petrov ответил Мур тема в Вопросы системного уровня проектирования

Как по мне, так с ModelSim гораздо продуктивнее иметь дело, поскольку можно видеть всю реализацию во времени. Пока всё это довольно бестолково выглядит, до продуктивного использования надо добраться. -

Там ошибка, оптимальный диапазон mu 0..1 -> z^-2..z^-1. Еще вопрос, почему в некоторых схемах petrov'а в сумматоре кое где к timing_error прибавляется 1ца, а кое где из 1цы ошибка вычитается? Значит где-то в другом месте петли наоборот вычитается, а кое-где прибавляется, не принципиально это.

-

Пробы HDL на Simulink

petrov ответил Мур тема в Вопросы системного уровня проектирования

Не работает и в 2016b. Дело не в матлабе. Гораздо конструктивнее будет сказать описание какой элементарной цифровой схемы вызывает затруднение. -

Пробы HDL на Simulink

petrov ответил Мур тема в Вопросы системного уровня проектирования

Методичка эта не нужна, 2018b открыть не могу, 2016b только, то что на скрине, так не делается. Можно разобрать как описывать элементрные цифровые схемы, из которых делается всё, не обязательно для этого полноценный проект выдумывать. -

Пробы HDL на Simulink

petrov ответил Мур тема в Вопросы системного уровня проектирования

Можно здесь на примерах какие-то элементарные конструкции разобрать. -

RobFPGA Увы, пока еще основными языками разработки для FPGA есть Verilog, SV, VHDL, которые напрямую позволяют получить бинарник для FPGA в компилляторах вендеров. И эти языки не ассемблер (попробуете-ка на гейт-уровне FFT нарисовать ), а очень даже FPGA-шный аналог C и местами даже C++. Через С и HDL надо продираться, чтобы FFT и подобное сделать, там ничего нет для понимания и отладки задачи, китайский язык мешающий, никакого окружения, в котором алгоритм живёт. В симулинке модель плавно конкретизируется до RTL, отлаживается там же сравнением с несинтезируемым исходным алгоритмом, на выходе читаемый HDL, сразу готовый для заливки в FPGA, без ада HDL и HDL симуляторов.

-

Декодер Витерби

petrov ответил Michael358 тема в Алгоритмы ЦОС (DSP)

Michael358 Не разберусь, как правильно нормализовывать метрики. Допустим, всегда передаются нули. Тогда метрика нулевого состояния декодера всегда будет равна нулю, а остальные метрики будут постоянно увеличиваться. И если вычитать минимальную метрику (т.е. ноль) из всех, то переполнения метрик не избежать. Можно накапливать метрики путей с коэффициентом меньше, но близким к 1. Разница буквально такая же, как между интегратором и ФНЧ на постоянной составляющей, интегратор имеет бесконечный коэффициент передачи на нулевой частоте, ФНЧ конечный, и переполнений можно избежать. -

Вычисление несущей для APSK?

petrov ответил Leshii тема в Алгоритмы ЦОС (DSP)

Pavel Proskura Преамбула составляет всего 26 символов, этого явно недостаточно чтобы надежно корректировать частоту. Вот у меня и возник вопрос как при большой расстройке и при плохом SNR делают АПЧ. Думаю достаточно PLHEADER модулированного pi/2-BPSK для обнаружения и оценки частоты, а на данных синхронизация поддерживается ФАПЧ управляемой решениями. -

Вычисление несущей для APSK?

petrov ответил Leshii тема в Алгоритмы ЦОС (DSP)

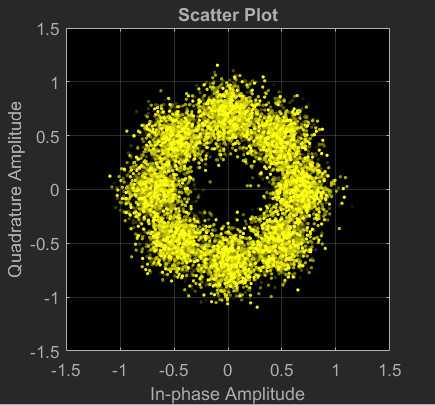

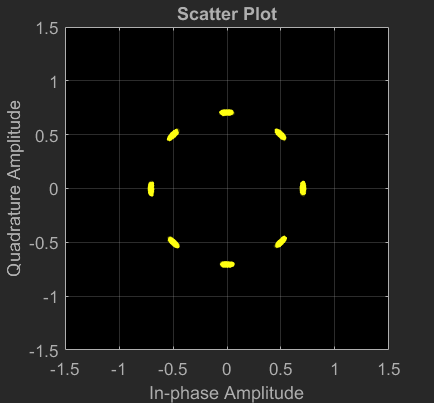

Pavel Proskura В сети в основном описываются алгоритмы использующие пилоты. Видимо не просто так разработчики себе жизнь упрощают преамбулами, пилот-тонами и т. п. Пробовал алгоритмы на основе БПФ и Luise & Reggiannini. Для 8-PSK при SNR=10 дБ, результат оценки смещения весьма плачевный. Полагаю связано это с возведение принимаемого сигнала в 8-ю степень. Если очень хочется, должно работать при большом усреднении. Eb/N0=6 dB. Остаточный фазовый шум при усреднении 1024 символов. -

https://ece.gmu.edu/coursewebpages/ECE/ECE448/S09/resources/vhdlsources.en.htm

-

wavelet IDWT/DWT Simulink

petrov ответил nice_vladi тема в Алгоритмы ЦОС (DSP)

nice_vladi Да, IFFT-FFT - без проблем. В конце-концов можно сделать на простых элементарных блоках, ведь DFT,DWT - всего лишь фильтры. -

wavelet IDWT/DWT Simulink

petrov ответил nice_vladi тема в Алгоритмы ЦОС (DSP)

nice_vladi Хочу сделать в симулинк вот так: А для обычной OFDM так в симулинке уже сделано? Считаю, раз люди публикуют статью - в ней более-менее достоверная информация Слишком оптимистично, данная статья довольно сомнительная. ИМХО -

Нужен передатчик посерьёзнее CC2510

petrov ответил Zoltrix тема в RF & Microwave Design

yurik82 по уровню хотя бы такого как в копеечном СС2510 или AT86RF233 Нет там никакого уровня. -

Нужен передатчик посерьёзнее CC2510

petrov ответил Zoltrix тема в RF & Microwave Design

Усилия по поднятию одни и те же, что простенькие, что не "простенькие", только простенькие и работают так себе, простенько, а к комбайну подключается FPGA и творится всё что угодно без ограничений. -

Нужен передатчик посерьёзнее CC2510

petrov ответил Zoltrix тема в RF & Microwave Design

https://limemicro.com/technology/lms7002m/ -

alexast К полосе лучше не привязываться, если вы посмотрите графики BER, там зависимость от Eb/N0, не зависит от формы сигнала(в частности полосы). N0 - спектральная плотность мощности шума, объективно существует без сигнала, например в каких-то случаях может рассчитываться из температуры и коэффициента шума МШУ. BER практически неудобно мерить, долго усреднять надо, и данные должны быть известны на приёме. Как здесь выше в статье приводили, на приёме Eb/N0 можно оценивать по уменьшению среднего расстояния между ближайшими точками созвездия модуляции.

-

AlexRayne а наверх страницы почему это не поместить, в шапку? https://electronix.ru/forum/index.php?app=forums&module=forums&controller=topic&id=149326&page=2&tab=comments#comment-1594102 IT достигли такого уровня, что живут своей жизнью, не IT для людей, а люди для IT. Не может процессор такую функцию обсчитать, чтобы переключатели в шапке на видном месте находились. Надо было так форум изуродовать... =(

-

ИМХО в основном профанация это всё, как не покажут результаты - всё размазня какая-то без объективной оценки качества.

-

Tpeck Если у Вас входной поток овер 200 МГц, а вы хотите промоделировать единицы КБод, а в петлях у вас Ку стремится к нулю, в результате переходной процесс занимает много сотен тысяч отсчетов. При этом Вы хотите посмотреть много точек сразу в симуляторе, то при таких исходных данных придется ждать много-много часов. В таком варианте проще развести в железе и отписать нужные Вам точки Проще задачу на независимые куски разбить и в симуляторе всё посмотреть. Нет никакой нужды даунконвертер с сотен мегагерц и модем на единицы килобод совместно целиком симулировать.

-

des00 Я не смог освоить это искусство. Не верю )), думаю, что вы более сложные методики освоили и примитивный симулинк ограничивать начинает.

-

Amurak Лучше выкинуть HDL и HDL симуляцию из разработки совсем. Только последний этап генерация HDL кода из полностью рабочей отлаженной simulink модели.

-

yes Да там много где не слишком удачная нотация, по крайней мере в контексте FPGA, видимо исторически у них сложилось, но жить можно.

-

MER на выходе усилителя мощности

petrov ответил alexPec тема в RF & Microwave Design

mux Речь о том, чтобы качественно посмотреть, как влияют нелинейности на модуляцию, чтобы не было сюрпризом в последний момент, что усилитель с отсечкой не подходит. -

MER на выходе усилителя мощности

petrov ответил alexPec тема в RF & Microwave Design

alexPec PS. Т.е. получается что у HMC MER уменьшается с ростом мощности больше не из-за IP3, а из-за отсечки отрицательной полуволны? И то и другое, такие вещи заранее элементарно на модели смотрятся, DVB-T не та модуляция, которую через какие угодно нелинейности можно пропускать без последствий.