-

Постов

2 233 -

Зарегистрирован

-

Посещение

-

Победитель дней

2

Весь контент Obam

-

IAR ARM работа с watch

Obam ответил Метценгерштейн тема в IAR

Drag-n-drop нет, но есть Copy-Paste. Опять же <click to edit> чем не подсказка? -

Прошу пощения, как (чем) при запрещённых прерываниях ядро будет выведено из (цитирую ARM DDI 0403E.B) "suspend execution and enter a low-power state. It can remain in that state until the processor detects one of the following WFI wakeup events: • A reset. • An asynchronous exception at a priority that, if PRIMASK was set to 0, would preempt any currently active exceptions. Note The processor ignores the value of PRIMASK in determining whether an asynchronous exception is a WFI wakeup event. • If debug is enabled, a debug event. • An IMPLEMENTATION DEFINED WFI wakeup event."? (конец цитаты) Какое событие из списка позволит исполнить _irq_enable()?

-

К плате нет никакой документации? Тип дисплея, цоколёвка известны? По собственному опыту я посоветовал бы обзавестись ДШ на дисплей и контроллер: хорошая точка старта.

-

Я посмотрел ARM DDI 0403E.b - Architecture Reference Manual - стр. B1-618: TS, эта команда разве в цикле должна вызываться? Опять же, прерывание для того и существует, чтобы событие его порождающее не ждать.

-

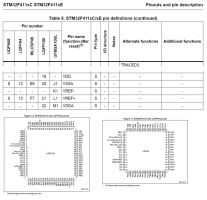

Подача Vdda у STM32F411

Obam ответил Dmitry Dubrovenko тема в ARM

Мил человек, где таблица выводов не соответствует корпусам? Уж на один лист все сведено. Ну ё-моё… -

Подача Vdda у STM32F411

Obam ответил Dmitry Dubrovenko тема в ARM

А то! При этом, ранее привёл выдержку из ДШ, что Vref+ есть только на 100-ногом корпусе, а в 48/64-ногом Vref+ соединено с Vdda. И? -

Подача Vdda у STM32F411

Obam ответил Dmitry Dubrovenko тема в ARM

Что написано в примечании? PS: в стародавние времена в FIDO зачитывание документации было делом платным ;) -

И перекоса быть не должно.

-

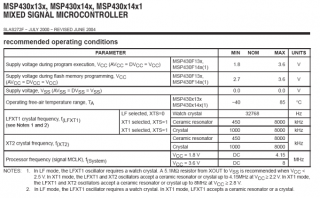

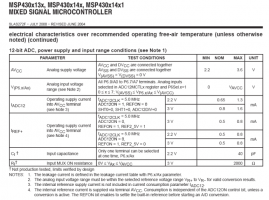

Реально, в последней ревизии datasheet-a (12 год, ау, TS ;) ) DVcc=AVcc=Vcc (стр.26 табл.Recommended Operating Conditions). Соединены или не соединены DVcc и AVcc - просто перекоса быть не должно (хотя мВ от 50-ти ничего страшного не будет, я так думаю). От того, что источник опорного напряжения питается от АVcc, не следует соединённность или не соединённость DVcc и AVcc.

-

СТРОКА в таблице. А прелесть 430-го семейства в их похожести как близнецов. И кстати, вы с начала не указали какой проц щупаете.

-

Первая строка в каждой таблице. Что вы там видите?

-

Datasheet отчего не почитать? К примеру: и Не той сложности процессор чтоб подобные "городушки" :) городить.

-

Подача Vdda у STM32F411

Obam ответил Dmitry Dubrovenko тема в ARM

DocID026289 Rev4 рис. 43 на стр. 115 и подпись к нему. -

В datashet-е и в RefMan-е вся расписана.

-

Вот ведь! "…так ходишь-ходишь, а потом бац! Вторая смена…" с v5.7 в IDA появилась поддержка MSP430 :)

-

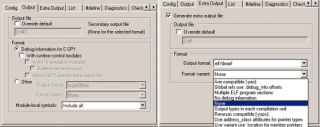

Так IAR может сгенерить и .elf (я для того скриншот и привёл). Опция какая подходит чтоб отладочная информация сохранилась (см. скриншот).

-

И что и символические имена будут?

-

?????????? Листинг - текстовый файл: текстовый редактор - на весь экран! В этом кроме пользы (во всех смыслах) - никакого вреда.

-

В IAR чем листинг (.lst) не устраивает?

-

Может надо не обобщённое ядро M3 выбирать, а конкретно контроллер STM32F…? Версия GUI последняя, свежая, стабильная?

-

Да какие косвенные измерения?! Осциллографом посмотреть-померять: опасаешься, что частота большая - задай другой коэффициент, проверь, потом верни какой надо.

-

Исходить надо из того, что Cortex-M не может иметь ни корректного ни "… некорректного перехода из режима Thumb в ARM… ". Нет у него режима ARM. Младший бит в R1 (BLX R1) - "0" наверное? Линкер неверно адрес назначает?