MementoMori

Свой-

Постов

1 340 -

Зарегистрирован

-

Посещение

Весь контент MementoMori

-

То есть стробы сделать заведомо длинее всех данных и адресов (самой длинной линии)?

-

Странно... я вроде бы подключал ibis модель с сайта stm. Настраивал в соответствии с аппноутом от st. Правда я скорость поставил там самую высокую (там варианты 00,01,10,11, я поставил 11). У меня есть плата 469 disco, там 60 трассы есть. И никаких резисторов. На практике на каких длинах появляется звон?

-

Господа, работаю над трассировкой SDRAM SDR (планируется частота 75 МГц) и STM32F746. Развел несколько линий адреса и данных. Исходя из габаритов STM, самой SDRAM, как их не располагай, как ни меняй линии данных (а адресные и вовсе нельзя менять), длина отдельных трасс достигает 55 мм. Моделирую в HyperLynx - неприемлемый звон появляется уже на длине 35 мм. В принципе, я готов к перспективе навешать на все линии резисторов (моделирование показало, что 70 Ом вполне достаточно). Но... Держу в руках планку SDRAM для компьютера. На ней резисторы в сборках только на линиях данных. Есть еще пару дискретных резисторов на всю планку, я так думаю, они предназначены для какой-то линии общей для всех микросхем, наверное для клока и еще чего-то. На адресных линиях резисторов нет. Хотя, представляя себе архитектуру и топологию матплаты, расстояние от процессора до адресных пинов во первых тоже приличное, во вторых, мало отличается от длины линий данных. Так почему же они не согласованы резисторами? Может к адресным линиями какие-то особые требования и им не нужны танцы с резисторами? Зависит ли от чего-нибудь еще амплитуда звона при переходном процессе? Нормально ли что у меня на 50 мм длины проводника есть звон, или я что-то не так настроил в HyperLynx?

-

Что-то я не понял, как открывать проекты в HyperLynx DRC 2.5? Я выбираю как и прежде пункт меню "открыть", но в списке возможных форматов нет файлов hyp или DSN. Я именно в эти форматы раньше, в версии 9.4.1 согласно туториалам, экспортировал проект из Альтиума. Или DRC в названии говорит о том, что это программа для других целей? Мне целостность сигналов проверять, если что.

-

Altium Designer 19 (365)

MementoMori ответил toshas тема в Altium Designer, DXP, Protel

Как быстро изменить зазор между множеством линий шины? Провел шину, предположим, у нее зазор 10 mils. Но вот я решил сделать 12 mils. Перенастроил в правилах, все стало зеленое. Очень не хочется двигать линии поштучно. -

Altium Designer 19 (365)

MementoMori ответил toshas тема в Altium Designer, DXP, Protel

Спасибо, нашел! -

Altium Designer 19 (365)

MementoMori ответил toshas тема в Altium Designer, DXP, Protel

Нашел. Нарисовалась проблема. Хочу настроить для одной из шин правило - ширина проводника 6 mils, а клиренс - 12 mils (правило 3W) Стало выдавать ошибку у футпринта - контактные площадки ведь тоже относятся к классу. Я настроил правило InNetClass('SDRAM') and NOT IsPad Но получилась такая картина Как сделать, чтобы альтиум не ругался на ошибку? -

Altium Designer 19 (365)

MementoMori ответил toshas тема в Altium Designer, DXP, Protel

.... -

Altium Designer 19 (365)

MementoMori ответил toshas тема в Altium Designer, DXP, Protel

А вы загляните в 19 версии в place->directives, там нет ничего про net classes -

Altium Designer 19 (365)

MementoMori ответил toshas тема в Altium Designer, DXP, Protel

Про шины я к слову спросил. А если я хочу выделить группу проводников и добавить в класс? Как добавить проводник в класс, я увидел, но у меня список классов пуст. Как создать класс? Гугление приводит к статьям, где описаны старые версии альтиума и того пункта в меню, который указан, в 19 версии нет -

Altium Designer 19 (365)

MementoMori ответил toshas тема в Altium Designer, DXP, Protel

Что-то я не нашел.... как классы цепей создавать? Галка - "автоматом создавать классы для шин" стоит, но список классов у меня пуст. -

Да знаю я, у меня так и есть. Пока у меня это сплошной 3v3 слой, дальше там будет трасса входного 12 вольтового питания. Небольшой участок с 5 вольтами (как раз для USB). Ну и...? у меня земля во втором слое GND и в свободных местах TOP и BOTTOM. Для чего в Power делать земли? Если над power сплошная земля?

-

Да, AD19. Интерфейс конечно оптимизирован и по мне так удобнее, но тормоза жуткие.... И глюки при прокладывании трасс....

-

Погодите... Вот слой TOP. В нем сигнальные линии. Дальше слой GND. Зачем в третьем слое еще тянуть участок земли?

-

Наверное плохо у меня с англицким.... Я правильно понял контекст, они упирают на то, что один слой должен быть сплошной землей, и под линиями обязательно должна быть земля? Кстати, насчет выравнивания - это конечно трынец... поскольку D7 длинее всего, то придется делать змейки на всех остальных линиях данных...

-

А говорят, куб - зло)) А вообще, вы слишком плохого обо мне мнения. Может я и сам в этом виноват. Но я именно кубом перебирал ноги. В кубе, я думаю, вы это знаете не хуже меня - можно нажать на ножку и куб покажет все альтернативы. Так вот для ULP_CK альтернативы нет. Еще раз глянул, там альтернативы только для STP,DIR и NXT. Эт как? Если я из TOP его сразу в BOTTOM брошу, под ним уже GND не будет. Может Вы имели в виду "над"? Так у меня сплошной GND. Чтоб мне проще было понять, Вы скажите, в чем беда перехода на другой слой при трассировке? Я до сегодняшнего дня думал, что только в том, что виа вносит дополнительную задержку прохождения сигнала. Оказывается нет? Если развести в разных слоях, но при этом уравнять задержки - это решит проблему?

-

Хм... насчет других чипов - первое же что попалось, от TI - TUSB120 - у него линии данных вообще в другую сторону, то есть по часовой стрелке идут. И клок с управляющими линиями тоже невпопад. Такое ощущение, что именно USB3300 под STM разрабатывался. Кстати, половина сигнальных линий на примере рекомендуемой производителем tusb1210 топологии все же идет через VIA http://www.ti.com/lit/ds/symlink/tusb1210.pdf См. стр.56, FIG 6-5.

-

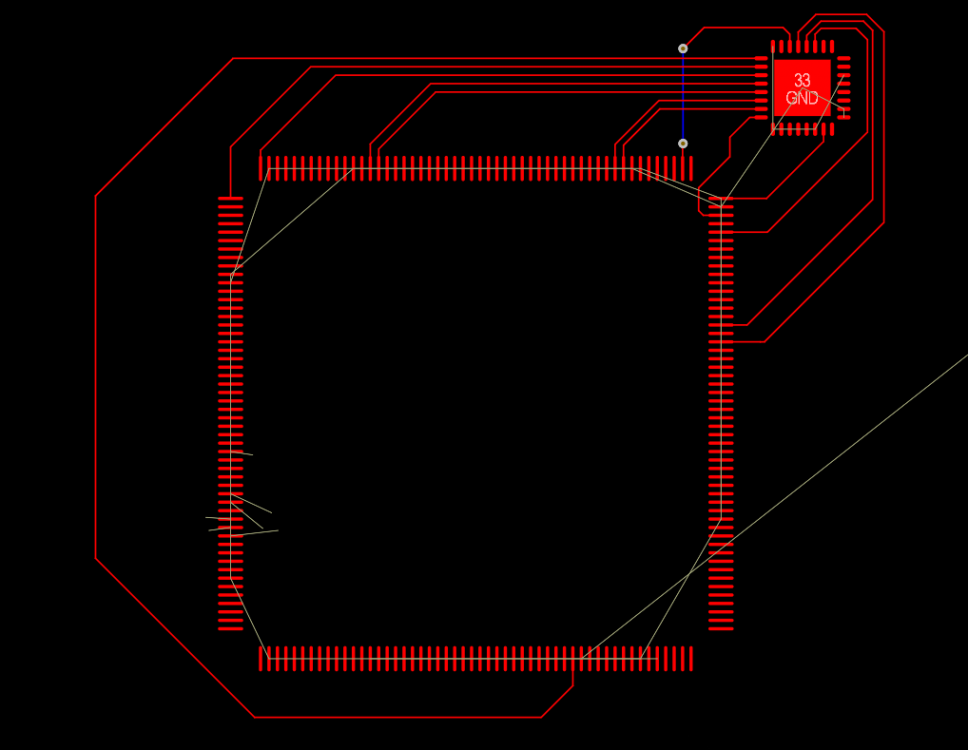

Ну я начну сначала с попытки перенести PHY чип, как с менее трудоемкого решения. Не получится, тогда буду разворачивать. Вот только на взаимоотношения со SDRAM это никак не повлияет. Вот уж никогда не подумал бы. Я думал, что SDRAM капризная штука. А все-таки, почему так? В SDRAM клок будет около 90 МГц, а в PHY всего 60. При этом к PHY требования выше... Вот посмотрите на аттаче. Как ни крути - клок пришлось переносить на другую линию. D7 вообще описывает петлю ( можно в принципе и справа обогнуть, будет короче, но не намного). Это я еще обвязку не цеплял. Тогда управляющие линии вообще будут подходить к чипу кругами, аки бомбардировщик заходит на посадку. Да я уж не помню, как поиски к нему привели. Информации много, распространенный чип. Недостатков на первый взгляд не увидел. Можете порекомендовать еще что-нибудь?

-

Ув. Aner - я перебрал все комбинации USB PHY - ULPI_CK не вписывается в идею трассировки всего на одном слое, его можно трассировать только через VIA. ПОследовательность у ног не та.

-

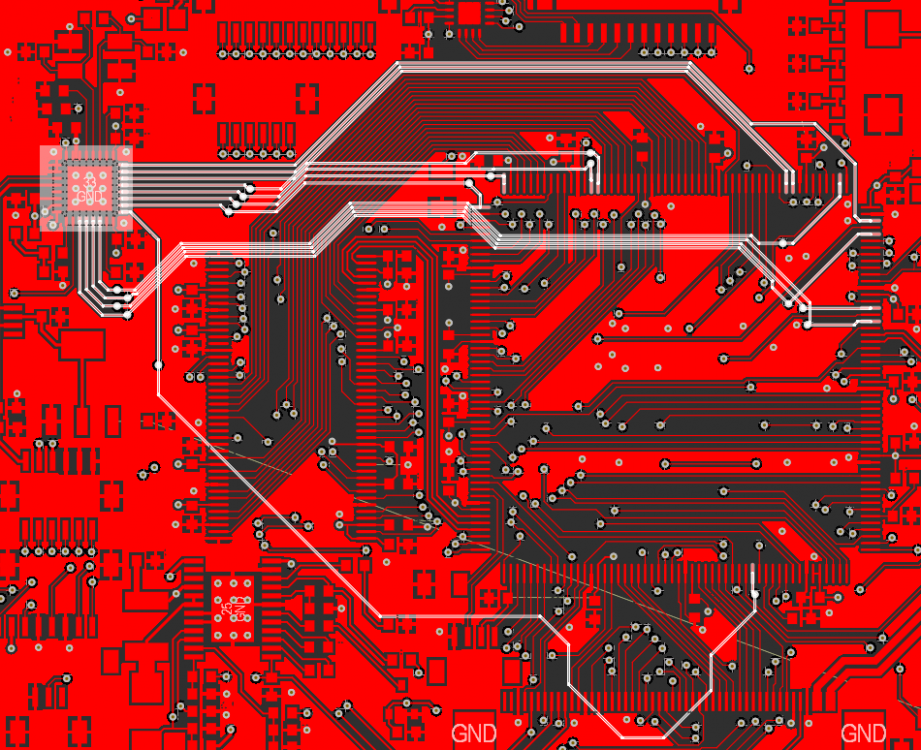

Безусловно. Я это правило, про стягивание полигонов переодными по краям знаю и всегда использую. По понятным причинам, это делается на завершающем этапе Просто я выкинул промежуточный вариант, я ведь не хотел оценки в целом, у меня были вопросы про usb. Так что очень надеюсь, что вывод "Землю разводить не умеете совем, " вы хоть немного, но пересмотрите))) Но все равно спасибо. Относительно Вашего совета разводить все сигнальные линии usb3300 в одном слое - посмотрите - выгоднее всего ставить микросхему у правого верхнего угла контроллера. но даже в этом случае у меня тогда придется все сигнальные линии sdram куда-то девать. Я конечно поиграюсь с ремаппингом... но если он не получится, есть ли тогда какой то компромиссный вариант?

-

Ок, уберу термопады, перемещу usb3300. Вы скажите все-таки, тот факт, что у меня есть сплошной земельный слой, он не спасает? Добавление рваной земли усугубляет проблему, если она имеет место быть в сигнальных слоях? Проблемные места, что вы обвели под чипом - я обычно, по завершению трассировки ставлю виа где можно либо сближаю проводники, убирая острова земли. Это спасет ситуацию?

-

на всякий случай спрошу, вы видели, что плата 4 слойная? В разделе ARM, наверное видели мои картинки? Земля у меня сплошная. А в top и bottom мне вообще предлагали земляной полигон удалить. Давайте так - сплошной (за исключением via) земельный слой у меня есть. От каждого потребителя максимально близко к нему к земальному слою у меня уходит via. Этого недостаточно? Земля в верхнем слое тоже должна соответствовать общим требованиям? Что, в частности, у меня не так с землей на верхнем слое (я так понял, замечание глобальное, безотносительно именно usb3300)? Хорошо помню, что в фразе о термопадах шла речь именно об импульсном преобразователе. О том, что термопады есть зло еще для чего-то, разговора не было. Спасибо за указание, учту. Пункты 3,4 — спасибо, принято

-

Плата 4 слойная, конечно. Вот тема, там на одной из последних страниц разводка

-

Длина трасс от USB3300

MementoMori опубликовал тема в RS232/LPT/USB/PCMCIA/FireWire

Господа, везде слышу рекомендации о том, что USB3300 нужно ставить как можно ближе к чипу (у меня в частности STM32F746) Вот что у меня получилось: D0 - 65.9 мм D1 - 57.2 mm D2 - 56,7 mm D3, D4 - 39.8 mm D5 - 31.2 mm D6 - 30.1 mm D7 - 81.2 mm CLK - 67.2 mm STP - 71 mm DIR - 71 mm NXT - 74.2 mm Вопросы: 1. Не длинновато ли, нужно ли укорачивать? 2. Нужно ли выравнивать? В аттаче картинка, которая позволит в общих чертах понять разводку. Первый вывод чипа вверху слева. Влево идут линии D0-D7, вниз управляющие линии. Все, что после via, идет в слое BOTTOM -

Погодите, где это он такое говорил.... в упор не вижу... Еще вопрос такой - если у меня линия CLK соседствует с линиями данных но собственных (SDRAM) - это страшно? Или нужно беспокоиться если клок рядом с линиями периферии, работающей от другого тактового источника?