-

Постов

121 -

Зарегистрирован

-

Посещение

-

Победитель дней

1

Весь контент dee2mon

-

При установке с диска нужно указывать КОРНЕВУЮ папку распакованного установщика, где файл Extrensions.ini, а не папку Extrensions.

-

Altium Designer для начинающих

dee2mon ответил ViKo тема в Altium Designer, DXP, Protel

Попробуйте поиграться с экспортом в pdf через Smart PDF снв галку Use Physical Structure. Ну или, еще можно в настройках Schematic - Compiler поснимать галки и посмотреть к чему это приведет. -

Altium 21.6 и выше

dee2mon ответил Uladzimir тема в Altium Designer, DXP, Protel

Стоп, стоп не надо ничего удалять и миллион раз писать. Если у всех линий выносок один текст, то полка объединяется. При установке схема здесь такая: 1. Ставится одиночная выноска, настраивается как надо. 2. Выбирается линия этой выноски и по пробелу добавляются еще линии, сколько надо. 3. Если то, к чему идет линия выноски, ей распознается и из-за этого автоматически выставляется текст на полке (как компонентам на Assembly View автоматически источником ставится BOM Item), то дополнительно зажимается CTRL. Тогда привязки не работают. Небольшой минус правда, при перемещении основной графики, выноски перестают с ней кататься. Все. -

Вопросы по Agilent ADS

dee2mon ответил Halo_Gen тема в RF & Microwave Design

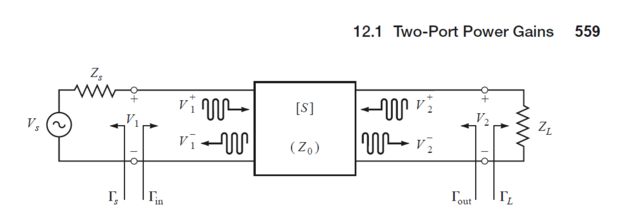

Всегда смотрите, то что рассчитывается (по формулам или из моделирования) куда смотрит. Всякие GA_MAX и пр. обычно возвращают импеданс со стороны транзистора. А терминаторы в ADS задаются со стороны нагрузки. И если что-то посчитано со стороны транзистора, то для моделирования нужно у терминаторов импеданс сопрягать. Вообще, вот вам священная картинка из Позара, с которой все начинается. P.S. А тем, кто дезайнил тулу SmithChart в ADS - лучи поноса. В ней по умолчанию со стороны генератора задается Zs* (т.е. импеданс транзистора по входу), а со стороны нагрузки - Zl (т.е. импеданс нагрузки с выходной стороны). Почему нельзя было сделать одинаково с обоих сторон, я не понимаю. Пока все-таки не сломался и залез в документацию, не понимал, почему у меня регулярно странные результаты получаются. -

Altium 21.6 и выше

dee2mon ответил Uladzimir тема в Altium Designer, DXP, Protel

По компоненту ПКМ - References -

Я начинаю подозревать, что вы не очень хотите разбираться. 1. Режим одного слоя по Shift+S называется Single Layer Mode чего-то там. 2. Идем на altium.com, там тыкаем на поиск, вбиваем single layer mode 3. В результатах ставим фильтр Documentation - Altium - 23 4. Первый же оставшийся результат Your View of the PCB in Altium Designer 5. Листаем до раздела Single-Layer Mode/Single-Layer 2D Display Mode и там прям картинка с настройками, с аж выделенным местом. Все. Ответ на вопрос ищется за 3 минуты..

-

Начать перетаскивать, по Ctrl+R переключать режимы (Stop, Avoid, Push и пр). Более точно настроить поведение - начать перетаскивать и нажать Tab. Откроется панель Interactive Sliding. Там все есть.

-

Это оооочень вредный совет, никогда не советую так делать. Зажмите Ctrl при перетаскивании. Временно отключает сетку.

-

Altium 21.6 и выше

dee2mon ответил Uladzimir тема в Altium Designer, DXP, Protel

Но если играть в ЕСКД, это все равно выглядит не очень весело, с длиииииинным рядком номеров падов. А прятать эти номера вроде как нежелательно. -

*В качестве дурной идеи. А вы попробуйте на нескольких номиналах резисторов из одной серии, там на единицах, сотнях и килоомах, например. Так чтоб у них совсем одинаковый корпус получался. А отличаться они должны только сопротивлением. И в САПРах потом на них вместе посмотреть.

-

Используйте SmartEdit и Paste Special - Paste Array, эта пара много чего может. В вашем случае я бы сделал так: 1. Левый верхний пад с номером "1" в нужную позицию. 2. Ctrl+C относительно его положения. 3. Paste Special - Paste Array, вниз с нужным шагом с инкрементом обозначения "1", вставить относительно левого верхнего пада. 4. ! Удалить задвоившийся первый пад 5. Ctrl+C весь первый столбик. 6. Вставить в нужные места второй и последующий столбики. 7. Выбирается первый столбик и поле Designator на три точки. 8. В окне SmartEdit выбрать режим Formula и ввести "a+!" 9. Повторить для остальных столбцов. Есть немного ручной работы. Но зато я понимаю, что делаю.

-

Говорили AD начал собирать инфу о своей пиратской установке где-то с 18 версии. И пока на будущее придерживает собранную статистику.

-

Около года-полутора назад, где-то в 20 и 21 версиях. А заметил недавно уже в 22 версии. Старая у меня нигде не стоит, так что не могу проверить, версия это виновата или еще что.

-

Как появилась возможность добавлять Солидворковские форматы, тоже вместо степок стал их использовать. А потом внезапно 3D-тела стали бессистемно исчезать из некоторых посадочных мест. Пришлось пройтись по библиотекам и перевставить именно в step-формате.

-

Altium и add shielding to net

dee2mon ответил Goldblin тема в Altium Designer, DXP, Protel

ХА. Буквально полгода назад. У коллеги была большая цифро-аналоговая плата с полигональной разводкой отдельных цепей. И одна не очень заметная заливка на внутреннем слое в топологии была залита (и в DRC не было ошибок), а вот в гербера не экспортировалась. Было на версии 21.4.1. Сменили версию на 22.4.чего-то там - в герберах все появилось. Если бы не проверка герберов (что естественно надо обязательно делать), могли такое пропустить.. -

Импорт GERBER в ЭМ симулятор

dee2mon ответил Evgeni тема в RF & Microwave Design

Из основного окна или из схемы File - Impot - Design, тип источника Netlist. Только возможно нужно будет поиграться еще с настройками импорта SPICE, т.к. их куча вариантов - повыбирать там диалект и пр. Вообще, ADS под это дело (быстрая подготовка к анализу и анализ разведенной топологии) плотно развивает несколько инструментов. Для ВЧ это RFPro, по нему и куча видющек на ютубе есть и пр.- 16 ответов

-

- свч

- целостность

-

(и ещё 1 )

C тегом:

-

Альтернативные виды символа (УГО)

dee2mon ответил S17 тема в Altium Designer, DXP, Protel

У меня другой прикол относительно недавно появился. Для разъемов завел два вида УГО, как стрелочки и в табличной форме. В компоненте есть набор параметров NetX, куда можно вбить название подключенной цепи для отображения в табличной форме. У этих параметров забиты положения чтобы были в нужных ячейках табличной формы. По умолчанию УГО в виде стрелочек и параметры с именами цепей скрыты. И теперь, если установить разъем, заполнить параметры с именами цепей и включить им отображение, положение этих параметров слетает куда-то кучей под УГО. Никакие игры с фиксированием положения параметров не работают :( При чем где-то до 20-версии все работало как я хотел, иначе б я не стал так делать библиотеку.. Мои старые записи говорят, что альтернативные УГО можно было задавать аналогично посадочникам, через Library Ref n/Library Path n. А сейчас в документации такого не нашел. Я что-то неправильно когда-то понял или эту возможность отрезали? -

Altium Designer для начинающих

dee2mon ответил ViKo тема в Altium Designer, DXP, Protel

Имеется ввиду расчет процента среза внешнего угла на повороте линии для исключения скачка волнового сопротивления? Тогда не, Altium такого не умеет. Он кладет линии траками, а у них концы скругленные. И поворот будет выглядеть как две линии подошли и с внешней стороны угла сглажены радиусом на полширины линии. Чтоб такое сделать нужно в чем-то внешнем эту геометрию посчитать и нарисовать регионом. Или использовать функцию Convert Selected Tracks to Chamfered Path (но я не помню, работает ли она кроме как для поворота на 90 градусов). -

Вопросы по CST

dee2mon ответил Pir0texnik тема в RF & Microwave Design

Она где-то с того времени было в составе CST в виде плагина 2D Filter Design. Прямая интеграция с CST и пр. Но, зараза, не входило в базовую поставку и версию для вузов, нужно было докупать отдельно. В прошлом году вроде как это подразделение ушло(?) в ANSYS, и теперь они делают видюшки про Automatic Filter Design Software. Но в CST этот плагин до сих пор есть. -

Вопросы по Agilent ADS

dee2mon ответил Halo_Gen тема в RF & Microwave Design

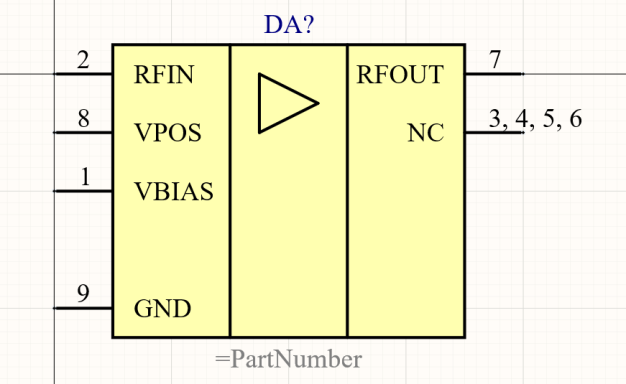

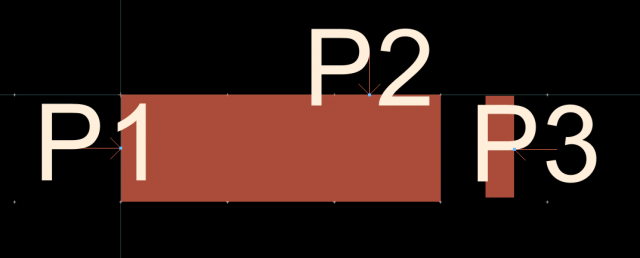

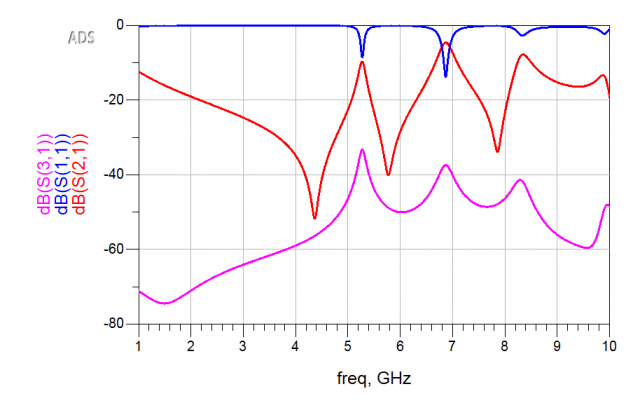

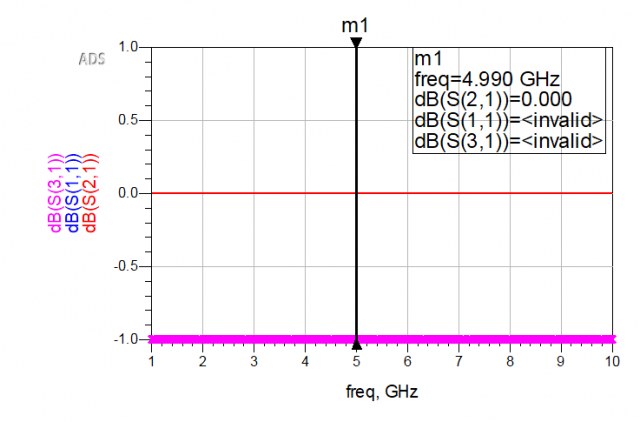

Как я знаю ADS, если ставить через Choose View for Simulation - Layout, то он не запускает EM-анализ. А просто закорачивает или разрывает соединенные (или не соединенные) пины из внутренней топологии. Эксперимент. Есть абсолютно дурная топология, где P1 и P2 на одном участке (закорочены по постоянке). P3 на оторваном. Результаты EM-анализа (Mom, на RO4350 толщиной 0,422мм). Если поставить Choose View for Simulation - Layout - то S21 = 0 dB, S31 = -Inf dB. Короч, похоже это имеет смысл только если делается большая схема, для нее делается нормальная большая топология. Между компонентами есть их соединяющие дорожки, но предполагается что влияние этих дорожек незначительно. И чтобы впустую не считать - они убираются из расчета. Как-то так. Может еще что есть, ADS большой и никто не знает его глубины. -

Вообще, нет. Обычно в предосмотре переходные отображаются. При схеме топологических слоев по умолчанию ads_standatd_layers в двуслойке отверстия рисуются в слое hole (5). И нужно еще, чтобы этот слой чтобы в определении подложки был назначен как слой отверстий (ПКМ - Map Conductor Via по диэлектрику). И сразу, может быть еще одна ошибка. По умолчанию подложка на основании шаблона 25milAlumina определяется как микрополосковая, т.е. двуслойная, cond - верхний слой, нижний слой бесконечная земля и то что нарисовано в cond2 - игнорируется. Нужно прямо указать, что графика на слое cond2 - это нижний слой.

-

Актуальный список мастеров посадочных мест и баз

dee2mon опубликовал тема в Библиотеки компонентов

Добрый день. Пытаюсь собрать актуальный список инструментов по созданию и добыче посадочных мест ЭКБ. Отдельных мастеров (не считая встроенных в САПР) я знаю два: - PCB Libraries Expert. Но он сначала подсадил всех на себя, а прошлым летом ввел расширенную подписку практически на все. - LP Wizard. Но он давно не обновлялся. Есть здесь что-то еще? Можно ли какой мастер поставить отдельно от САПР? Открытые базы (которые не просто хранилище на гитхабе, а актуальные и обновляемые): - SnapEDA - OctoPart - ComponentSearchEngine - UltraLibrarian Есть тут еще кто полезный? -

Altium Designer для начинающих

dee2mon ответил ViKo тема в Altium Designer, DXP, Protel

Ну, вообще-то имя цепи (отличное от автоматически сгенерированного вида NecC13_2) можно задать: - через метку цепи Net Label - через имя подключенного порта Port - через имя подключенной глобальной цепи Power Port - через OffSheet Connector Еще можно потом уже в топологии поменять имя цепи на желаемое. Но это такой себе выстрел себе в ногу, это изменение обратно в схематик не переносится. И схема с топологией будут различаться без острой на это необходимости. Может еще как есть, AD большой. Но вот только так, как хочет @Rodavion - нельзя. -

При печати через промежуточный SmartPDF нужно указать, чтобы выводилась физическая структура (а не логическая). Тогда в pdf-нике будет полная нумерация компонентов и именование цепей в соответствии с печатной платой.

-

СВЧ-материал с высокой диэл. прон.

dee2mon ответил Turgenev тема в RF & Microwave Design

А какие из них подходят для число ВЧ-многослоек или гибридных попарных стеков типа ВЧ-диэел/препрег/FR-4? По документации как-то слабо описано и примеров типовых стеков что-то я не нашел. Можно ли в них делать без проблем переходные отверстия или они как керамика?