-

Постов

1 610 -

Зарегистрирован

-

Посещение

-

Победитель дней

2

Весь контент juvf

-

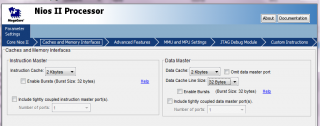

частота 50 МГц. констрейн настроил. Непомогло. с утра уже час как рыба на льду.

-

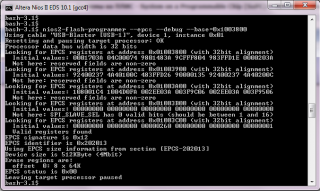

что-то подобное получилось, см рисунок. Но теперь ельф не грузится. Вообще я заметил, что загрузка кода для дебага в ниос зависит от расположения звезд. Похоже сейчас солнце в казероге, дебаг не грузится. Помогите разобраться. Собрал в квартусе схему с ниосом. Вектор ресета на epcs контроллер. Скомпелял. теперь в эклипсе есть рабочий проект. заного сгенерировал BSP. Собрал проект. Вызвал Quartus Programmer и залил *.sof через JTAG в ПЛИС. Аппаратная часть стартовала и заработала в соответствии с разработкой в квартусе. ПКМ по проекту... Debug AS...->Debug Configuration... На вкладке Project нужный проект и нужный elf. На вкладке Target Connection нужный USB-Blaster. Жму кнопку Debug ..... Побежали цыфры с %%..... ошибка!!! 'Launching nameProject NIOS II Hardware Configuration' has encounted problem. Downloading ELF Process Failed. смотрю лог Failed Executing: [nios2-download, '--cable=USB-Blaster on localhost [uSB-1]', --device=1, --instance=1, --sidp=0x1004158, --id=0x0, --timestamp=1297768557, /cygdrive/d/Work/Quartus/TestBench/software/frontEndOS/frontEndOS.elf] return code: 4, 'other error' An exception stack trace is not available. Что за ошибка? Иногда бывает бьюсь пол дня. на утро включаю - все работает. А иногда помогает пересборка без изменений ниоса, пересборка sof, пересборка BSP и программы для ниоса. Как это побороть?

-

тааак..... понятно.... спасибо ......

-

ну как-то не идет........ Ни один из 3-х способов. Решил хотябы один способ освоить. Пусть будет с контроллером epcs. Добавил в ниос контроллер. Как пины на контроллере назначать? Где в сетингах Device and Pin Options? так и не нашел. В переводе naliwator исправленно Assignments->Devices->Device and Pin Options. Сделал Use as regular I/O. Но как пины назначить? Я так понял в схеме верхнего уровня создать примитив Pin xxxx ....... хз какой.... С большей вероятностью data0_to_the_epcs_controller должен быть входом, остальные выходы. (хотя не факт, возможно и что-то 2направлено). посоеденил пины к ниосу. После анализа...... что дальше? можно (или нужно) ли их в пин планере добавлять? Или в пинпланере не надо, а только в assignments editor и причем Location не назначать, а только, например для data0_to_the_epcs_controller назначить assignment name -> Data[0], а Location автоматом на стандартные ноги назначится?

-

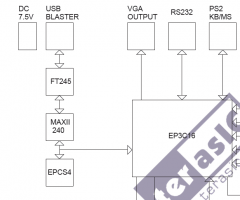

Не получается. Картинка 1.1 How the Nios II Flash Programmer Works из этого документа..... Комп заливает прошивку в плис, а плис в epcs. естественно ниже требование для NIOS - должен быть контроллер epcs. У меня боарт от terasic "Altera DE0 Board". В ниосе не было ни контроллера epcs, ни cfi, ни мостов. Апаратную часть удалось зашитить в ерсs. Но как програму ниоса зашить? В прикреплении функциональная схема. По документу Nios II FlashProgrammer User Guide требуется контроллер epcs. Добавил в ниос контроллер. Вывод контроллера clk стал выходом. Посмотрел принципиальную схему борды - генератор clk на epcs является не ПЛИС, а MAXII 240. И клок от епцс к DE0 подключен к ВХОДУ плис. Но в ниосе это выход. Как назначать пин у плис? Наверно такой способ прожига не подойдет. даже на картинке 1.1 показанно, что через плис прожигается епцс, а в DE0, судя по схеме, мимо епцс. Может нужно слить аппаратную прошивку с программой в один файл и прошить его? Но это как сделать? Тоже не понятно. Не понятно.... Должен ли быть в ниосе epcs контроллер? Если не должен быть, то картинки 2-2 из этого документа нету. Если он должен быть, то как назначить пины в DE0? Кто нибудь пробовал поднять ниос на подобных бордах? Как в них заливать программу для ниоса в epcs? p.s. в прикреплении принципиальная схема DE0. DE0_V12_RELEASE.pdf

-

А как залить прошивку в ниос? Собрал в sopc процессор, собрал в квартусе схему, скомпелировал. В эклипсе создал проект и написал прогу для своей борды. В режиме дебага программа работает. Даже получилось залить свою конфигурацию в epcs и при включении работает моя аппаратная часть. А как залить программу для ниоса во флешь?

-

Как в Altium сделать...

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

В P-CAD-e была возможность добавлять цепи на ПП. Как в альтиуме добавить цепь в редакторе РСВ? -

Как в Altium сделать...

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Дифпары автороутер трасирует как не дифпары. Как заставить автороутер трасировать дифпары как дифпары? -

-

Не знаю. в сопсб билдере специально не добавлял. мож где по умолчанию есть? а как посмотреть?

-

да, также Ну я тоже пришел к такому мнению. Почему сразу не сообразил :laughing:

-

да, но я выкидываю не в JTAG-UART. а добавил в ниос отдельный UART. через отдельный уарт printf наладил. я думал что в апаратном уарте есть апартный буфер размером в 1 байт. может есть программный буфер какой, так опять же прога однопоточная. для програмного буфера тоже поток нужен. как-то не понятно.

-

пишу однопоточное приложение. без всяких ос. в нужных местах в терминал бросаю отладочную инфу printf("Recived %u bytes, command %u, for device with address %u\n\r", count, com, adr); иногда после этого кода останавливаюсь в точке остановки, и вижу в терминале вывод Recived 13 bytes, command 1, for dev потом продолжаю выполнение программы, и вижу в терминале довыводит сообщение полностью Recived 13 bytes, command 1, for device with address 15 Иногда после printf("Recived.... делаю команду printf("Send..., остановливаюсь после неё, а в терминале часть сообщения предыдущего вызова, т.е. Recived.... Продолжаю, оба сообщения приходят в терминал. Почему так происходит? printf запускается в каком-то другом потоке чтоли?

-

Медное жало для паяльной станции

juvf ответил juvf тема в Пайка и монтаж

Бред, не бред - но я ещё не видел живого человека, кто бы захвалил долговечные жала. Через меня прошло с десяток современных станций и паяльников. Паять этим - полное Г. имхо. Припой не берётся. На работе все плюются от станций. Один, самый продвинутый на столе держыт станцию, а в тумбочке держит обычный медный. Всё сложное им паяет. Я решил домой купить современный хорошый паяльник. В магазине консультант сказал "А вы умеете паять долговечным жалом? Там особая техника нужна. Если не умеете, ни разу не паяли, то возьмите лучше обычный медный. Многие покупатели после покупки долговечных приходили потом за медью." Вот тут я понял, что существует какаято магическая технология пайки современным паяльником, которой я не владею, из-за чего я мучаюсь с совр. паяльниками. Купил обычный советский медный паяльник с сменным жалом. Штатным жалом тока ведра лудить. Пошел к электрикам, взял обрезки одножыльных медных проводом разного сечения, от 1 кв. до 12 кв. Нарезал их на жала. Милое дело. Паяю всё что мне нужно. микросхемы с ножками 0.2-0.3, с шагом 0,5. Дупло у паяльника под жало диаметром милиметров 6. Если в нем выгорит медное жало деаметром в 3 мм, то паяльник не выйдет строя. Конечно если впритирку туда медь засунуть - то кирдык паяльнику. Но на работе станция. как бы с ней подружится? Решил освоить технику пайки долговечным жалом. Нашел в инете несколько уроков. В двух словах: В одной руке держим припой, в другой паяльник .... А..... выводной резистор или проводок, который нужно припаять к ПП или к висячему проводку чем держать? Зубами? В тех уроках вообще не предусмотренно чтоб припой взять паяльником и припаять. Поэтому и созрела мысль одеть на керамику медь. Если такого нет, то попробую у слесарей заказать. можно сделать железный наконечник с зажимим для медного жала. на керамику одевать железо, а в железо зажимать короткие медные жала. Купить метр медного провода - для лабораторных целей - на всю жизнь хватит. ps У нас есть сборочный участок. Монтажники всё в ручную паяют. корпуса практически все паяют, кроме BGA. Мы им раз в год полностью меняем все медные паяльники и .... наверно почаще заказываем у токарей медные жала. Купили для них современную паяльную станцию. На пробу. Ну неделю она по по всем рукам походила. Вернули. Сказали - такое Г им больше не предлагать. Медь лучше. -

Медное жало для паяльной станции

juvf опубликовал тема в Пайка и монтаж

Не могу подружиться с долговесными жалами. Бывает медное жало для паяльных станций, а конкретно для саламона SL-30? -

Нашел багу в коде. В обработчик прерывания я всётаки попадаю, но в обработчике не сбрасываю флаг прерывания таймера. поэтому выйдя из обработчика, сразуже возвращаюсь в него. Добавил в обработчик сброс флага ТО и все заработало. Спасибо за наставление на путь истенный. Проблема решена.

-

а как узнать? этот таймер TIMERSEGLED_IRQ. в system.h TIMERSEGLED_IRQ = 8. какие ещё используются? 9, 10, .... ну так-то там много номеров прерываний, но пока в программе использую только 3 прерывания, 1 - уарт и 2 таймера. вот system.h на всякий случаю /* #ifndef __SYSTEM_H_ #define __SYSTEM_H_ /* Include definitions from linker script generator */ #include "linker.h" /* * CPU configuration * */ #define ALT_CPU_ARCHITECTURE "altera_nios2" #define ALT_CPU_BIG_ENDIAN 0 #define ALT_CPU_BREAK_ADDR 0x1010820 #define ALT_CPU_CPU_FREQ 50000000u #define ALT_CPU_CPU_ID_SIZE 1 #define ALT_CPU_CPU_ID_VALUE 0x0 #define ALT_CPU_CPU_IMPLEMENTATION "fast" #define ALT_CPU_DATA_ADDR_WIDTH 25 #define ALT_CPU_DCACHE_LINE_SIZE 32 #define ALT_CPU_DCACHE_LINE_SIZE_LOG2 5 #define ALT_CPU_DCACHE_SIZE 2048 #define ALT_CPU_EXCEPTION_ADDR 0x1008020 #define ALT_CPU_FLUSHDA_SUPPORTED #define ALT_CPU_FREQ 50000000 #define ALT_CPU_HARDWARE_DIVIDE_PRESENT 0 #define ALT_CPU_HARDWARE_MULTIPLY_PRESENT 1 #define ALT_CPU_HARDWARE_MULX_PRESENT 0 #define ALT_CPU_HAS_DEBUG_CORE 1 #define ALT_CPU_HAS_DEBUG_STUB #define ALT_CPU_HAS_JMPI_INSTRUCTION #define ALT_CPU_ICACHE_LINE_SIZE 32 #define ALT_CPU_ICACHE_LINE_SIZE_LOG2 5 #define ALT_CPU_ICACHE_SIZE 2048 #define ALT_CPU_INITDA_SUPPORTED #define ALT_CPU_INST_ADDR_WIDTH 25 #define ALT_CPU_NAME "cpu_0" #define ALT_CPU_NUM_OF_SHADOW_REG_SETS 0 #define ALT_CPU_RESET_ADDR 0x1008000 /* * CPU configuration (with legacy prefix - don't use these anymore) * */ #define NIOS2_BIG_ENDIAN 0 #define NIOS2_BREAK_ADDR 0x1010820 #define NIOS2_CPU_FREQ 50000000u #define NIOS2_CPU_ID_SIZE 1 #define NIOS2_CPU_ID_VALUE 0x0 #define NIOS2_CPU_IMPLEMENTATION "fast" #define NIOS2_DATA_ADDR_WIDTH 25 #define NIOS2_DCACHE_LINE_SIZE 32 #define NIOS2_DCACHE_LINE_SIZE_LOG2 5 #define NIOS2_DCACHE_SIZE 2048 #define NIOS2_EXCEPTION_ADDR 0x1008020 #define NIOS2_FLUSHDA_SUPPORTED #define NIOS2_HARDWARE_DIVIDE_PRESENT 0 #define NIOS2_HARDWARE_MULTIPLY_PRESENT 1 #define NIOS2_HARDWARE_MULX_PRESENT 0 #define NIOS2_HAS_DEBUG_CORE 1 #define NIOS2_HAS_DEBUG_STUB #define NIOS2_HAS_JMPI_INSTRUCTION #define NIOS2_ICACHE_LINE_SIZE 32 #define NIOS2_ICACHE_LINE_SIZE_LOG2 5 #define NIOS2_ICACHE_SIZE 2048 #define NIOS2_INITDA_SUPPORTED #define NIOS2_INST_ADDR_WIDTH 25 #define NIOS2_NUM_OF_SHADOW_REG_SETS 0 #define NIOS2_RESET_ADDR 0x1008000 /* * Custom instruction macros * */ #define ALT_CI_CONVERTER(A) __builtin_custom_ini(ALT_CI_CONVERTER_N,(A)) #define ALT_CI_CONVERTER_N 0x0 /* * Define for each module class mastered by the CPU * */ #define __ALTERA_AVALON_JTAG_UART #define __ALTERA_AVALON_NEW_SDRAM_CONTROLLER #define __ALTERA_AVALON_ONCHIP_MEMORY2 #define __ALTERA_AVALON_PIO #define __ALTERA_AVALON_SPI #define __ALTERA_AVALON_SYSID #define __ALTERA_AVALON_TIMER #define __ALTERA_AVALON_UART #define __ALTERA_NIOS2 #define __ALTERA_NIOS_CUSTOM_INSTR_ENDIAN_CONVERTER /* * GPIO configuration * */ #define ALT_MODULE_CLASS_GPIO altera_avalon_pio #define GPIO_BASE 0x1011180 #define GPIO_BIT_CLEARING_EDGE_REGISTER 0 #define GPIO_BIT_MODIFYING_OUTPUT_REGISTER 0 #define GPIO_CAPTURE 0 #define GPIO_DATA_WIDTH 8 #define GPIO_DO_TEST_BENCH_WIRING 0 #define GPIO_DRIVEN_SIM_VALUE 0x0 #define GPIO_EDGE_TYPE "NONE" #define GPIO_FREQ 50000000u #define GPIO_HAS_IN 0 #define GPIO_HAS_OUT 1 #define GPIO_HAS_TRI 0 #define GPIO_IRQ -1 #define GPIO_IRQ_INTERRUPT_CONTROLLER_ID -1 #define GPIO_IRQ_TYPE "NONE" #define GPIO_NAME "/dev/GPIO" #define GPIO_RESET_VALUE 0x0 #define GPIO_SPAN 16 #define GPIO_TYPE "altera_avalon_pio" /* * IOHex configuration * */ #define ALT_MODULE_CLASS_IOHex altera_avalon_pio #define IOHEX_BASE 0x10111a0 #define IOHEX_BIT_CLEARING_EDGE_REGISTER 0 #define IOHEX_BIT_MODIFYING_OUTPUT_REGISTER 0 #define IOHEX_CAPTURE 0 #define IOHEX_DATA_WIDTH 32 #define IOHEX_DO_TEST_BENCH_WIRING 0 #define IOHEX_DRIVEN_SIM_VALUE 0x0 #define IOHEX_EDGE_TYPE "NONE" #define IOHEX_FREQ 50000000u #define IOHEX_HAS_IN 0 #define IOHEX_HAS_OUT 1 #define IOHEX_HAS_TRI 0 #define IOHEX_IRQ -1 #define IOHEX_IRQ_INTERRUPT_CONTROLLER_ID -1 #define IOHEX_IRQ_TYPE "NONE" #define IOHEX_NAME "/dev/IOHex" #define IOHEX_RESET_VALUE 0xffffffff #define IOHEX_SPAN 16 #define IOHEX_TYPE "altera_avalon_pio" /* * IOLed configuration * */ #define ALT_MODULE_CLASS_IOLed altera_avalon_pio #define IOLED_BASE 0x1011190 #define IOLED_BIT_CLEARING_EDGE_REGISTER 0 #define IOLED_BIT_MODIFYING_OUTPUT_REGISTER 0 #define IOLED_CAPTURE 0 #define IOLED_DATA_WIDTH 10 #define IOLED_DO_TEST_BENCH_WIRING 0 #define IOLED_DRIVEN_SIM_VALUE 0x0 #define IOLED_EDGE_TYPE "NONE" #define IOLED_FREQ 50000000u #define IOLED_HAS_IN 0 #define IOLED_HAS_OUT 1 #define IOLED_HAS_TRI 0 #define IOLED_IRQ -1 #define IOLED_IRQ_INTERRUPT_CONTROLLER_ID -1 #define IOLED_IRQ_TYPE "NONE" #define IOLED_NAME "/dev/IOLed" #define IOLED_RESET_VALUE 0x0 #define IOLED_SPAN 16 #define IOLED_TYPE "altera_avalon_pio" /* * System configuration * */ #define ALT_DEVICE_FAMILY "CYCLONEIII" #define ALT_ENHANCED_INTERRUPT_API_PRESENT #define ALT_IRQ_BASE NULL #define ALT_LOG_PORT "/dev/null" #define ALT_LOG_PORT_BASE 0x0 #define ALT_LOG_PORT_DEV null #define ALT_LOG_PORT_TYPE "" #define ALT_NUM_EXTERNAL_INTERRUPT_CONTROLLERS 0 #define ALT_NUM_INTERNAL_INTERRUPT_CONTROLLERS 1 #define ALT_NUM_INTERRUPT_CONTROLLERS 1 #define ALT_STDERR "/dev/jtag_uart_0" #define ALT_STDERR_BASE 0x10111b0 #define ALT_STDERR_DEV jtag_uart_0 #define ALT_STDERR_PRESENT #define ALT_STDERR_TYPE "altera_avalon_jtag_uart" #define ALT_STDIN "/dev/terminal" #define ALT_STDIN_BASE 0x1011160 #define ALT_STDIN_DEV terminal #define ALT_STDIN_PRESENT #define ALT_STDIN_TYPE "altera_avalon_uart" #define ALT_STDOUT "/dev/terminal" #define ALT_STDOUT_BASE 0x1011160 #define ALT_STDOUT_DEV terminal #define ALT_STDOUT_PRESENT #define ALT_STDOUT_TYPE "altera_avalon_uart" #define ALT_SYSTEM_NAME "cpuNiosII" /* * hal configuration * */ #define ALT_MAX_FD 32 #define ALT_SYS_CLK none #define ALT_TIMESTAMP_CLK TIMER_SYS /* * jtag_uart_0 configuration * */ #define ALT_MODULE_CLASS_jtag_uart_0 altera_avalon_jtag_uart #define JTAG_UART_0_BASE 0x10111b0 #define JTAG_UART_0_IRQ 0 #define JTAG_UART_0_IRQ_INTERRUPT_CONTROLLER_ID 0 #define JTAG_UART_0_NAME "/dev/jtag_uart_0" #define JTAG_UART_0_READ_DEPTH 64 #define JTAG_UART_0_READ_THRESHOLD 8 #define JTAG_UART_0_SPAN 8 #define JTAG_UART_0_TYPE "altera_avalon_jtag_uart" #define JTAG_UART_0_WRITE_DEPTH 64 #define JTAG_UART_0_WRITE_THRESHOLD 8 /* * onchip_memory2_0 configuration * */ #define ALT_MODULE_CLASS_onchip_memory2_0 altera_avalon_onchip_memory2 #define ONCHIP_MEMORY2_0_ALLOW_IN_SYSTEM_MEMORY_CONTENT_EDITOR 0 #define ONCHIP_MEMORY2_0_ALLOW_MRAM_SIM_CONTENTS_ONLY_FILE 0 #define ONCHIP_MEMORY2_0_BASE 0x1008000 #define ONCHIP_MEMORY2_0_CONTENTS_INFO "" #define ONCHIP_MEMORY2_0_DUAL_PORT 0 #define ONCHIP_MEMORY2_0_GUI_RAM_BLOCK_TYPE "Automatic" #define ONCHIP_MEMORY2_0_INIT_CONTENTS_FILE "onchip_memory2_0" #define ONCHIP_MEMORY2_0_INIT_MEM_CONTENT 1 #define ONCHIP_MEMORY2_0_INSTANCE_ID "NONE" #define ONCHIP_MEMORY2_0_IRQ -1 #define ONCHIP_MEMORY2_0_IRQ_INTERRUPT_CONTROLLER_ID -1 #define ONCHIP_MEMORY2_0_NAME "/dev/onchip_memory2_0" #define ONCHIP_MEMORY2_0_NON_DEFAULT_INIT_FILE_ENABLED 0 #define ONCHIP_MEMORY2_0_RAM_BLOCK_TYPE "Auto" #define ONCHIP_MEMORY2_0_READ_DURING_WRITE_MODE "DONT_CARE" #define ONCHIP_MEMORY2_0_SIZE_MULTIPLE 1 #define ONCHIP_MEMORY2_0_SIZE_VALUE 30720u #define ONCHIP_MEMORY2_0_SPAN 30720 #define ONCHIP_MEMORY2_0_TYPE "altera_avalon_onchip_memory2" #define ONCHIP_MEMORY2_0_WRITABLE 1 /* * sdram_0 configuration * */ #define ALT_MODULE_CLASS_sdram_0 altera_avalon_new_sdram_controller #define SDRAM_0_BASE 0x800000 #define SDRAM_0_CAS_LATENCY 3 #define SDRAM_0_CONTENTS_INFO "" #define SDRAM_0_INIT_NOP_DELAY 0.0 #define SDRAM_0_INIT_REFRESH_COMMANDS 2 #define SDRAM_0_IRQ -1 #define SDRAM_0_IRQ_INTERRUPT_CONTROLLER_ID -1 #define SDRAM_0_IS_INITIALIZED 1 #define SDRAM_0_NAME "/dev/sdram_0" #define SDRAM_0_POWERUP_DELAY 100.0 #define SDRAM_0_REFRESH_PERIOD 15.625 #define SDRAM_0_REGISTER_DATA_IN 1 #define SDRAM_0_SDRAM_ADDR_WIDTH 22 #define SDRAM_0_SDRAM_BANK_WIDTH 2 #define SDRAM_0_SDRAM_COL_WIDTH 8 #define SDRAM_0_SDRAM_DATA_WIDTH 16 #define SDRAM_0_SDRAM_NUM_BANKS 4 #define SDRAM_0_SDRAM_NUM_CHIPSELECTS 1 #define SDRAM_0_SDRAM_ROW_WIDTH 12 #define SDRAM_0_SHARED_DATA 0 #define SDRAM_0_SIM_MODEL_BASE 1 #define SDRAM_0_SPAN 8388608 #define SDRAM_0_STARVATION_INDICATOR 0 #define SDRAM_0_TRISTATE_BRIDGE_SLAVE "" #define SDRAM_0_TYPE "altera_avalon_new_sdram_controller" #define SDRAM_0_T_AC 5.5 #define SDRAM_0_T_MRD 3 #define SDRAM_0_T_RCD 20.0 #define SDRAM_0_T_RFC 70.0 #define SDRAM_0_T_RP 20.0 #define SDRAM_0_T_WR 14.0 /* * spi_AD4360_9 configuration * */ #define ALT_MODULE_CLASS_spi_AD4360_9 altera_avalon_spi #define SPI_AD4360_9_BASE 0x1011080 #define SPI_AD4360_9_CLOCKMULT 1 #define SPI_AD4360_9_CLOCKPHASE 0 #define SPI_AD4360_9_CLOCKPOLARITY 0 #define SPI_AD4360_9_CLOCKUNITS "Hz" #define SPI_AD4360_9_DATABITS 24 #define SPI_AD4360_9_DATAWIDTH 32 #define SPI_AD4360_9_DELAYMULT "1.0E-9" #define SPI_AD4360_9_DELAYUNITS "ns" #define SPI_AD4360_9_EXTRADELAY 0 #define SPI_AD4360_9_INSERT_SYNC 0 #define SPI_AD4360_9_IRQ 3 #define SPI_AD4360_9_IRQ_INTERRUPT_CONTROLLER_ID 0 #define SPI_AD4360_9_ISMASTER 1 #define SPI_AD4360_9_LSBFIRST 0 #define SPI_AD4360_9_NAME "/dev/spi_AD4360_9" #define SPI_AD4360_9_NUMSLAVES 1 #define SPI_AD4360_9_PREFIX "spi_" #define SPI_AD4360_9_SPAN 32 #define SPI_AD4360_9_SYNC_REG_DEPTH 2 #define SPI_AD4360_9_TARGETCLOCK 128000u #define SPI_AD4360_9_TARGETSSDELAY "0.0" #define SPI_AD4360_9_TYPE "altera_avalon_spi" /* * spi_AD5623 configuration * */ #define ALT_MODULE_CLASS_spi_AD5623 altera_avalon_spi #define SPI_AD5623_BASE 0x10110e0 #define SPI_AD5623_CLOCKMULT 1 #define SPI_AD5623_CLOCKPHASE 0 #define SPI_AD5623_CLOCKPOLARITY 0 #define SPI_AD5623_CLOCKUNITS "Hz" #define SPI_AD5623_DATABITS 24 #define SPI_AD5623_DATAWIDTH 32 #define SPI_AD5623_DELAYMULT "1.0E-9" #define SPI_AD5623_DELAYUNITS "ns" #define SPI_AD5623_EXTRADELAY 0 #define SPI_AD5623_INSERT_SYNC 0 #define SPI_AD5623_IRQ 6 #define SPI_AD5623_IRQ_INTERRUPT_CONTROLLER_ID 0 #define SPI_AD5623_ISMASTER 1 #define SPI_AD5623_LSBFIRST 0 #define SPI_AD5623_NAME "/dev/spi_AD5623" #define SPI_AD5623_NUMSLAVES 3 #define SPI_AD5623_PREFIX "spi_" #define SPI_AD5623_SPAN 32 #define SPI_AD5623_SYNC_REG_DEPTH 2 #define SPI_AD5623_TARGETCLOCK 128000u #define SPI_AD5623_TARGETSSDELAY "0.0" #define SPI_AD5623_TYPE "altera_avalon_spi" /* * spi_ADF4350 configuration * */ #define ALT_MODULE_CLASS_spi_ADF4350 altera_avalon_spi #define SPI_ADF4350_BASE 0x1011060 #define SPI_ADF4350_CLOCKMULT 1 #define SPI_ADF4350_CLOCKPHASE 0 #define SPI_ADF4350_CLOCKPOLARITY 0 #define SPI_ADF4350_CLOCKUNITS "Hz" #define SPI_ADF4350_DATABITS 32 #define SPI_ADF4350_DATAWIDTH 32 #define SPI_ADF4350_DELAYMULT "1.0E-9" #define SPI_ADF4350_DELAYUNITS "ns" #define SPI_ADF4350_EXTRADELAY 0 #define SPI_ADF4350_INSERT_SYNC 0 #define SPI_ADF4350_IRQ 2 #define SPI_ADF4350_IRQ_INTERRUPT_CONTROLLER_ID 0 #define SPI_ADF4350_ISMASTER 1 #define SPI_ADF4350_LSBFIRST 0 #define SPI_ADF4350_NAME "/dev/spi_ADF4350" #define SPI_ADF4350_NUMSLAVES 2 #define SPI_ADF4350_PREFIX "spi_" #define SPI_ADF4350_SPAN 32 #define SPI_ADF4350_SYNC_REG_DEPTH 2 #define SPI_ADF4350_TARGETCLOCK 128000u #define SPI_ADF4350_TARGETSSDELAY "0.0" #define SPI_ADF4350_TYPE "altera_avalon_spi" /* * spi_DAT_31R5 configuration * */ #define ALT_MODULE_CLASS_spi_DAT_31R5 altera_avalon_spi #define SPI_DAT_31R5_BASE 0x1011100 #define SPI_DAT_31R5_CLOCKMULT 1 #define SPI_DAT_31R5_CLOCKPHASE 0 #define SPI_DAT_31R5_CLOCKPOLARITY 0 #define SPI_DAT_31R5_CLOCKUNITS "Hz" #define SPI_DAT_31R5_DATABITS 8 #define SPI_DAT_31R5_DATAWIDTH 16 #define SPI_DAT_31R5_DELAYMULT "1.0E-9" #define SPI_DAT_31R5_DELAYUNITS "ns" #define SPI_DAT_31R5_EXTRADELAY 0 #define SPI_DAT_31R5_INSERT_SYNC 0 #define SPI_DAT_31R5_IRQ 7 #define SPI_DAT_31R5_IRQ_INTERRUPT_CONTROLLER_ID 0 #define SPI_DAT_31R5_ISMASTER 1 #define SPI_DAT_31R5_LSBFIRST 0 #define SPI_DAT_31R5_NAME "/dev/spi_DAT_31R5" #define SPI_DAT_31R5_NUMSLAVES 4 #define SPI_DAT_31R5_PREFIX "spi_" #define SPI_DAT_31R5_SPAN 32 #define SPI_DAT_31R5_SYNC_REG_DEPTH 2 #define SPI_DAT_31R5_TARGETCLOCK 128000u #define SPI_DAT_31R5_TARGETSSDELAY "0.0" #define SPI_DAT_31R5_TYPE "altera_avalon_spi" /* * spi_FM25CL64 configuration * */ #define ALT_MODULE_CLASS_spi_FM25CL64 altera_avalon_spi #define SPI_FM25CL64_BASE 0x10110a0 #define SPI_FM25CL64_CLOCKMULT 1 #define SPI_FM25CL64_CLOCKPHASE 0 #define SPI_FM25CL64_CLOCKPOLARITY 0 #define SPI_FM25CL64_CLOCKUNITS "Hz" #define SPI_FM25CL64_DATABITS 8 #define SPI_FM25CL64_DATAWIDTH 16 #define SPI_FM25CL64_DELAYMULT "1.0E-9" #define SPI_FM25CL64_DELAYUNITS "ns" #define SPI_FM25CL64_EXTRADELAY 0 #define SPI_FM25CL64_INSERT_SYNC 0 #define SPI_FM25CL64_IRQ 4 #define SPI_FM25CL64_IRQ_INTERRUPT_CONTROLLER_ID 0 #define SPI_FM25CL64_ISMASTER 1 #define SPI_FM25CL64_LSBFIRST 0 #define SPI_FM25CL64_NAME "/dev/spi_FM25CL64" #define SPI_FM25CL64_NUMSLAVES 3 #define SPI_FM25CL64_PREFIX "spi_" #define SPI_FM25CL64_SPAN 32 #define SPI_FM25CL64_SYNC_REG_DEPTH 2 #define SPI_FM25CL64_TARGETCLOCK 128000u #define SPI_FM25CL64_TARGETSSDELAY "0.0" #define SPI_FM25CL64_TYPE "altera_avalon_spi" /* * spi_TMP_121 configuration * */ #define ALT_MODULE_CLASS_spi_TMP_121 altera_avalon_spi #define SPI_TMP_121_BASE 0x10110c0 #define SPI_TMP_121_CLOCKMULT 1 #define SPI_TMP_121_CLOCKPHASE 0 #define SPI_TMP_121_CLOCKPOLARITY 0 #define SPI_TMP_121_CLOCKUNITS "Hz" #define SPI_TMP_121_DATABITS 16 #define SPI_TMP_121_DATAWIDTH 16 #define SPI_TMP_121_DELAYMULT "1.0E-9" #define SPI_TMP_121_DELAYUNITS "ns" #define SPI_TMP_121_EXTRADELAY 0 #define SPI_TMP_121_INSERT_SYNC 0 #define SPI_TMP_121_IRQ 5 #define SPI_TMP_121_IRQ_INTERRUPT_CONTROLLER_ID 0 #define SPI_TMP_121_ISMASTER 1 #define SPI_TMP_121_LSBFIRST 0 #define SPI_TMP_121_NAME "/dev/spi_TMP_121" #define SPI_TMP_121_NUMSLAVES 2 #define SPI_TMP_121_PREFIX "spi_" #define SPI_TMP_121_SPAN 32 #define SPI_TMP_121_SYNC_REG_DEPTH 2 #define SPI_TMP_121_TARGETCLOCK 128000u #define SPI_TMP_121_TARGETSSDELAY "0.0" #define SPI_TMP_121_TYPE "altera_avalon_spi" /* * sysid configuration * */ #define ALT_MODULE_CLASS_sysid altera_avalon_sysid #define SYSID_BASE 0x10111b8 #define SYSID_ID 680655224u #define SYSID_IRQ -1 #define SYSID_IRQ_INTERRUPT_CONTROLLER_ID -1 #define SYSID_NAME "/dev/sysid" #define SYSID_SPAN 8 #define SYSID_TIMESTAMP 1295254251u #define SYSID_TYPE "altera_avalon_sysid" /* * terminal configuration * */ #define ALT_MODULE_CLASS_terminal altera_avalon_uart #define TERMINAL_BASE 0x1011160 #define TERMINAL_BAUD 115200 #define TERMINAL_DATA_BITS 8 #define TERMINAL_FIXED_BAUD 1 #define TERMINAL_FREQ 50000000u #define TERMINAL_IRQ 10 #define TERMINAL_IRQ_INTERRUPT_CONTROLLER_ID 0 #define TERMINAL_NAME "/dev/terminal" #define TERMINAL_PARITY 'N' #define TERMINAL_SIM_CHAR_STREAM "" #define TERMINAL_SIM_TRUE_BAUD 0 #define TERMINAL_SPAN 32 #define TERMINAL_STOP_BITS 1 #define TERMINAL_SYNC_REG_DEPTH 2 #define TERMINAL_TYPE "altera_avalon_uart" #define TERMINAL_USE_CTS_RTS 0 #define TERMINAL_USE_EOP_REGISTER 0 /* * timerSegLed configuration * */ #define ALT_MODULE_CLASS_timerSegLed altera_avalon_timer #define TIMERSEGLED_ALWAYS_RUN 0 #define TIMERSEGLED_BASE 0x1011140 #define TIMERSEGLED_COUNTER_SIZE 32 #define TIMERSEGLED_FIXED_PERIOD 0 #define TIMERSEGLED_FREQ 50000000u #define TIMERSEGLED_IRQ 9 #define TIMERSEGLED_IRQ_INTERRUPT_CONTROLLER_ID 0 #define TIMERSEGLED_LOAD_VALUE 4999999ULL #define TIMERSEGLED_MULT 0.0010 #define TIMERSEGLED_NAME "/dev/timerSegLed" #define TIMERSEGLED_PERIOD 100 #define TIMERSEGLED_PERIOD_UNITS "ms" #define TIMERSEGLED_RESET_OUTPUT 0 #define TIMERSEGLED_SNAPSHOT 1 #define TIMERSEGLED_SPAN 32 #define TIMERSEGLED_TICKS_PER_SEC 10u #define TIMERSEGLED_TIMEOUT_PULSE_OUTPUT 0 #define TIMERSEGLED_TYPE "altera_avalon_timer" /* * timer_0 configuration * */ #define ALT_MODULE_CLASS_timer_0 altera_avalon_timer #define TIMER_0_ALWAYS_RUN 0 #define TIMER_0_BASE 0x1011120 #define TIMER_0_COUNTER_SIZE 32 #define TIMER_0_FIXED_PERIOD 0 #define TIMER_0_FREQ 50000000u #define TIMER_0_IRQ 8 #define TIMER_0_IRQ_INTERRUPT_CONTROLLER_ID 0 #define TIMER_0_LOAD_VALUE 499999ULL #define TIMER_0_MULT 0.0010 #define TIMER_0_NAME "/dev/timer_0" #define TIMER_0_PERIOD 10 #define TIMER_0_PERIOD_UNITS "ms" #define TIMER_0_RESET_OUTPUT 0 #define TIMER_0_SNAPSHOT 1 #define TIMER_0_SPAN 32 #define TIMER_0_TICKS_PER_SEC 100u #define TIMER_0_TIMEOUT_PULSE_OUTPUT 0 #define TIMER_0_TYPE "altera_avalon_timer" /* * timer_sys configuration * */ #define ALT_MODULE_CLASS_timer_sys altera_avalon_timer #define TIMER_SYS_ALWAYS_RUN 0 #define TIMER_SYS_BASE 0x1011000 #define TIMER_SYS_COUNTER_SIZE 64 #define TIMER_SYS_FIXED_PERIOD 1 #define TIMER_SYS_FREQ 50000000u #define TIMER_SYS_IRQ 11 #define TIMER_SYS_IRQ_INTERRUPT_CONTROLLER_ID 0 #define TIMER_SYS_LOAD_VALUE 49ULL #define TIMER_SYS_MULT 1.0E-6 #define TIMER_SYS_NAME "/dev/timer_sys" #define TIMER_SYS_PERIOD 1 #define TIMER_SYS_PERIOD_UNITS "us" #define TIMER_SYS_RESET_OUTPUT 0 #define TIMER_SYS_SNAPSHOT 1 #define TIMER_SYS_SPAN 64 #define TIMER_SYS_TICKS_PER_SEC 1000000u #define TIMER_SYS_TIMEOUT_PULSE_OUTPUT 0 #define TIMER_SYS_TYPE "altera_avalon_timer" /* * uart_0 configuration * */ #define ALT_MODULE_CLASS_uart_0 altera_avalon_uart #define UART_0_BASE 0x1011040 #define UART_0_BAUD 115200 #define UART_0_DATA_BITS 8 #define UART_0_FIXED_BAUD 1 #define UART_0_FREQ 50000000u #define UART_0_IRQ 1 #define UART_0_IRQ_INTERRUPT_CONTROLLER_ID 0 #define UART_0_NAME "/dev/uart_0" #define UART_0_PARITY 'N' #define UART_0_SIM_CHAR_STREAM "" #define UART_0_SIM_TRUE_BAUD 0 #define UART_0_SPAN 32 #define UART_0_STOP_BITS 1 #define UART_0_SYNC_REG_DEPTH 2 #define UART_0_TYPE "altera_avalon_uart" #define UART_0_USE_CTS_RTS 0 #define UART_0_USE_EOP_REGISTER 0 #endif /* __SYSTEM_H_ */

-

Как запустить таймер?

juvf опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

в ниосе есть таймер и уарт. Написал обработчик уарт, в обработчике запускаю таймер. Таймер отрабатывает и вызывается обработчик таймера. Теперь понадобилось запустить таймер не из обработчика прерывания уарт, а из главного цыкла while(1) в main. Программа виснет. Посмотрел где стоим.... в функции void alt_irq_handler (void) на цикле do { i = 0; mask = 1; /* * Test each bit in turn looking for an active interrupt. Once one is * found, the interrupt handler asigned by a call to alt_irq_register() is * called to clear the interrupt condition. */ do { if (active & mask) { #ifdef ALT_ENHANCED_INTERRUPT_API_PRESENT alt_irq[i].handler(alt_irq[i].context); #else alt_irq[i].handler(alt_irq[i].context, i); #endif break; } mask <<= 1; i++; } while (1); active = alt_irq_pending (); } while (active); alt_irq_pending () всегда возвращает 0х100. Из do-while ни когда не выходит. Почему? иницыализацию таймера делаю так void init() { //настройка таймера для HEX монитора IOWR_ALTERA_AVALON_TIMER_CONTROL(TIMERSEGLED_BASE, 0); #ifdef ALT_ENHANCED_INTERRUPT_API_PRESENT alt_ic_isr_register(TIMERSEGLED_IRQ_INTERRUPT_CONTROLLER_ID, TIMERSEGLED_IRQ, timerHexInt, (void*)TIMERSEGLED_BASE, NULL); // обозначение прерывания /* Start timer */ IOWR_ALTERA_AVALON_TIMER_CONTROL(TIMERSEGLED_BASE, ALTERA_AVALON_TIMER_CONTROL_ITO_MSK | ALTERA_AVALON_TIMER_CONTROL_START_MSK); #else /* Register the interrupt */ alt_irq_register(TIMERSEGLED_IRQ, TIMERSEGLED_BASE, timerHexInt); /* Start timer */ IOWR_ALTERA_AVALON_TIMER_CONTROL(TIMERSEGLED_BASE, ALTERA_AVALON_TIMER_CONTROL_ITO_MSK | ALTERA_AVALON_TIMER_CONTROL_START_MSK); #endif } При инициализации ALT_ENHANCED_INTERRUPT_API_PRESENT определён. Что я делаю не так? Почему не попадаю в обработчик прерывания? Почему зависаю в alt_irq_handler (void)? -

Как в Altium сделать...

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

фенкс -

Как в Altium сделать...

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

У меня по F8 вообще ни чего не происходит -

Как в Altium сделать...

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Как задать шаг сетки в редакторе посадочного места 1.27 мм х 9.62 мм? -

вобщем проблема в том, скорее всего процессор игнорирует младший бит для указателя на слово. Поэтому если указатель на слово нечетный, например 0х0890015, то он воспринимается как 0х0890014. Однако указатель на char по нечетному адресу работает нормально. Особенности архитектуры. Отчасти есть тут вина компилятора. В стандарте с++ не оговариваются подобные нюансы. И если компилятором заявленно "с++", то компилятор должен придерживаться стандарта. Возможно где-то в доках на компилятор этот нюанс оговорен, но я не нашел. А возможно, что компилятор с каким нибудь ключем, правильно разименует нечетный указатель на слово, ведь возможно же обращение к нечётной ячейке памяти. Вобщем для себя проблему решиль примерно так, тока не макросы, а вместо char bufRecive[100]; написал класс с 2-мя шаблонными функциями write<class T>(const T& t, int adr) и T read<class T>(int adr), который хранит массив и записывает/читает байты в/из него любого типа, любой длинны и по любому адресу. Проблема решена. Всем спасибо.

-

ну короче прошагал по коду reinterpret_cast работает как надо. а вот разименование не работает как надо я вот по такой штуке прошагал alt_u16* p = reinterpret_cast<alt_u16*>(&bufRecive[0]); *p = 0x1234; p = reinterpret_cast<alt_u16*>(&bufRecive[1]); *p = 0x7890; p = reinterpret_cast<alt_u16*>(&bufRecive[2]); *p = 0x4321; p = reinterpret_cast<alt_u16*>(&bufRecive[3]); *p = 0x0987; p = reinterpret_cast<alt_u16*>(&bufRecive[4]); *p = 0x6571; p = reinterpret_cast<alt_u16*>(&bufRecive[5]); *p = 0x4294; p = reinterpret_cast<alt_u16*>(&bufRecive[6]); *p = 0x5302; p = reinterpret_cast<alt_u16*>(&bufRecive[7]); *p = 0x0192; если p указывает на четный адрес, то всё нормально, после*p = 0xХХХХ; меняется два байта по адресам р и р+1. если р указывает на нечётный адрес,то меняется два байта по адресу р-1 и по адресу р Есть у кого какие мысли?

-

странно, в другом месте обнаружил alt_u16 command = *reinterpret_cast<alt_u16*>(&bufRecive[4]); такой код ни разу не сбоил. ну в ниосе компилятор nios2-elf-gcc, линкер nios2-elf-g++. У алтеры про них скудно как-то написанно. Попробую покопаться в манах gnu gcc а вот это интересней, щя буду пробовать... Endian Converter Custom Instruction - не помогло ((

-

не помогло (( а в какой доке расписаны дерективы процессора, всякие __attribute__, прагмы и т.п.?