-

Постов

1 610 -

Зарегистрирован

-

Посещение

-

Победитель дней

2

Весь контент juvf

-

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Как в многолистовом проекте задавать параметры? На первом листе нарисовал штамп для первой страницы. В поле децимального номера вставил текст и вбил в него "=decNum". Потом ПКМ/Option/Document Parametrs.../Parametrs, добавляю параметр decNum со значением БЮИЛ.457157.017. В штампе появляется заветный номер. Но на другом листе из того же проекта почему то параметра decNum нет. Приходится на каждом листе проекта добавлять в опции параметр decNum. Как поля в АД делаются? Как сделать так, чтоб в одном месте прописать децимальный номер и потом он сам в нужных местах на всех листах проекта был? -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Ээээ,,,,, это как? Это значит добавили в схему новый конденсатор в начало списка, т.е. который должен стать в итоге C1. По умолчанию десигнатор у него С?. Устанавливаем ему любой свободны десигнатор, например С12345. Делаем экспорт в ПП. Потом делаем в схеме перенумерацию и еще раз экспорт. Завтра попробую эту шаманскую пляску. -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Ну я вот так раньше и делал. Просто решил с эти разобраться. У меня было не только в этом случае, и с 0402 на 0805 тоже было. Хотя надо понаблюдать. Но в данный момент у меня пады разные. Т.е. есть конденсаторы обычные, двух выводные, и есть проходные, у них 3 пада. Добавил в начало схемы конденсатор, вся нумерация сдвинулась. С54 был обычной керамикой 0402, а после перенумерации C54 стал проходным с 3-мя выводами. Всё! Футпринты, коменты, и еще всякие атрибуты не обнавляются. ((( Такая же картина была если нумерация микросхем сменится. А там вообще каждая мк/с имеет свой пад. Как то это можно поправить? -

во время выравнивания длинны змейкой клавишами 1,2,3,4,<,> изменяется форма змейки, в том числе и фаски. Не то?

-

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Почему не работает синхронизация ПП и схемы? Есть схема, её экспортировали в ПП. Часть ПП развели. Внесли изменеия в схему. В редакторе схемы жму update PCB, Validate, Execute. результат на скриншоте. Смотрю, корпуса у всех компонентов из перечисленных в скриншоте не изменились. жму в редакторе схемы update PCB - опять всё по новой. та же картина как и на скриншоте. теже элементы требуют модификации. Например С143 опять требует замены посадочного места. Может еще где что настроить нужно? -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Аааааа...... Семён Семёныч! вобщем нужно имя цепи задавать не "net123", а имя жгута + имя цепи в жгуте, т.е. "zgut1.net123" Спасибо! Спасибо, почитаю. -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Да вроде в обоих схемах одинаково имена задавал. ??? -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

В спешке забыл проект примера прикрепить sss.7z -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Как правильно соеденять части схем через жгуты? Сделал маленький пример в прекриплении. Сделал в одной схеме две комнаты и соеденил их жгутом. Запускаю компеляцию - получаю ворнинг [Warning] Sheet1.SchDoc Compiler Nets Wire NET123 has multiple names (Net Label NET123,Sheet Entry Designator-ZGUT1.NET123(Passive)) 17:53:35 20.10.2010 1 Почему ворнинг? Что я делаю не так? Как от этово ворнинга избавится? Ну и до кучи вопрос по ворнингам второй: есть УГО из 10 частей. Использую только паты В, С, F. Компиляция дает ворнинг, типа в компаненте D12 есть неиспользуемые парты. Как от этих ворнингов избавится? -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Заработало. Спасибо. Только как-то через бубен. Действительно последовательность вставки графики и дисигнатора важна. Десигнатор на месте стоит. Пришлось выделить весь парт, удалить, сохранить уго, потом обратно вставить парт туда, где он стоял. опять сохраняем уго - и с этим партом стало всё впорядке. Для старых элементом нужно так шаманить с каждым партом. (( -

FAQ по Altium Designer

juvf ответил masterofnature тема в Altium Designer, DXP, Protel

Вопрос: Как оперелить место Designator-a при создании УГО? Ответ: При создании УГО заходим в Tools->Document Options, ставим галку Always Show Comment/Designator. Обозначение компанента ставонится видимым при редатировании УГО. Заходим в свойства Designator-а и снимаем галку Autoposition. -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

А нет меню Design. Смог найти Tools->Document Options. Вот же засаде. Действительно такое неудобство доставляет многогейтовое УГО. С многогейтовым не работает. :( -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Как сделать чтоб обозначение элемента (XP1, XP2, C1, C2, C3, D1, ...) при апдейте было там, где нужно? В пикаде при создании УГО указывалось место куда ставить RefDes по умолчанию. В альтиуме такого не нашел. Но в альтиуме, после вставки компонента в схему руками перетаскиваю десигнатор в нужное место. Впринцепе устраивает. Но если подправить УГО компанента и сделать update from library, то RefDes (в AD это Designator) перемещяается в разные, не нужные места. Как это побороть? -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Не понял (( У меня не верхнем слое на весь слой лежит полигон. Паяльной маской залит весь слой кроме контактных площадок - и дорожки, и переходки, и полигон. на свободном месте сделал в полигоне логотип. Но он заливается маской. Как мне сделать, чтоб логотип не заливался паяльной маской? -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Нужно сделть облать на верхнем слое которая не будет залита паяльной (защитной) маской. Как такое в альтиуме делается? -

FAQ по Altium Designer

juvf ответил masterofnature тема в Altium Designer, DXP, Protel

PCB редактор Вопрос: Как сделать планое расширение дорожек (капли/слёзы) при подходе к via или pad? Ответ: Tools/Teardrops... ps А нельзя где-нибудь в одном месте выложить последнюю версию "ЧАсто задаваемые ВОпросы по Altium Designer.pdf". Например, как это делают на др форумах, в этой теме на каждой странице дублируется одно сообщение с ссылкой на последний пдф. А то не удобно ползать по всей ветке и искать последнюю версию. -

Плавное расширение проводника

juvf ответил juvf тема в Altium Designer, DXP, Protel

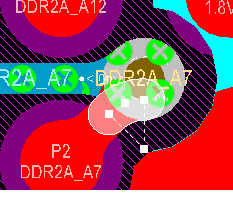

Вообщем оставил только одно правило для Clearance. Данная ошибка исчезла. Но вообще осталось тонна других, в том числе и с дугами. Есть элемент типа Tainet. Footprint для него - это 4 контактных площядри с отверстием в одной точке. Добавл Teadrops, сало по 80 ошибок на каждый тайнет. Удалил все Teadrops - осталось несколько ошибок. вообщем подходит к тайнету 2 дорожки по одному слою. каждая дорожка - это своя цепь, DDR2A_A7 и DDR2B_A7. в Тайнете эти цепи объеденяются в одну физичечкую цепь. DRC ругается. Говорит что растояние между дорожками цепей DDR2A_A7 и DDR2B_A7 слишком маленькое (возле тайнета). Как создать правильные правила чтоб DRC не ругался на Tainet? -

Плавное расширение проводника

juvf ответил juvf тема в Altium Designer, DXP, Protel

Спасибо, то что нужно. Но перестала выполнятся проверка DRC. Была цепь растащена по 2-м слоям. Пад1<->дорожкаПоСлою1<->via<->дорожкаПоСлою2<->Пад2 Добавил Teadrops. Цепь преобразовалась в Пад1<->дорожкаПоСлою1 + дуга1 + дуга2<->via<->дорожкаПоСлою2 + дуга3 + дуга4<->Пад2 Запускаю DRC. Получаю ошибку Clearance Constraint: Between Via (150.8mm,179.8mm) Top Layer to Bottom Layer And Arc (150.49822mm,179.49822mm) Т.е. слишком маленькое растояние между дуга1 и via. Все дуги и via принадлежат к одной цепи. Почему ошибка? Как от неё избавиться. -

Плавное расширение проводника

juvf опубликовал тема в Altium Designer, DXP, Protel

В АД можно сделать плавное расширение дорожек при подходе к переходному отверстию или к паду? Например как это делает Топор -

html в микроконтроллере

juvf ответил juvf тема в Все остальные микроконтроллеры

Ага, спасибо за курс,,,,,, почитал в вики. Устаревший протокол. Вместо него сейчас используют РРР. Т.е. если соеденяться по rs-232, то придется програмно реализовывать стек протокола TCP/IP (PPP или SLIP). Не очень радует (( Ну допустим реализую я РРР и будет страничка html в железке. Как комп подключится к ней? если я подключусь 232-ым к железке и напишу в браузере нужный ip-адрес - то как комп перенаправит запрос не в сетевую карту а в сом порт? Как это работает например в Windows? Нужно будет добавлять в "Деспетчере устройств" какой-нибудь нуль-модем и задавать ему ip-адрес? Или ещё как? А как это работает в *nix-ах? -

html в микроконтроллере

juvf опубликовал тема в Все остальные микроконтроллеры

Требуется конфигурировать разработанное устройство. Нужно писать для компьютера кокойто конфигуратор и по какому-то протоколу через UART (USB, RS-232, RS-485, CMOS) или SPI общаться с железкой. Есть мысль не писать ни какой конфигуратор и в железке, а написать html и по tcp/ip через последовательный интерфейс любым браузером конфигурировать железку. Вопрос: реально ли на UART-е реализовать в железке tcp/ip или придется использовать преобразователь Ethernet<->UART(SPI)? Какие ресурсы потребуются для html, т.е. сколько памяти нужно? -

Проблема решена. Всем спасибо

-

Дак как-то с редакторм символов не получается. Написал я свой модуль, сгенерировал bdf, вставил в схему верхнего уровня. Открыл свой модуль в редакторе символов - отредактировал - вот оно счастье! Далее, что нибудь в модуле поправил, в файле *.v, теперь чтоб эти изменения вступили в силу - нужно перегенерировать bdf файл. Все мои рисунки удаляются ((. Приходится заново в символьном редакторе перерисовывать. И так каждый раз после любого изменения модуля.

-

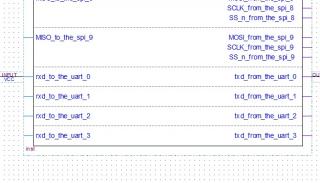

Написал свой модуль в отдельном файле на Verilig HDL. Генерирую из него файл *.bdf - получаю графический блок с входами и выходами. Но некоторые выходы лучше разделить на разные блоки. SOPC билдер генерирует nios и все компоненты процессора на bdf блоке отделены разделительными линиями. См картинку, несколько UART-ов разделены линиями. как такое можно сделать в смоем самописном модуле?

-

ссылка битая, на пустоя яндекс Не могу найти. Какимим ключевыми словами можно найти эту тему?