-

Постов

1 611 -

Зарегистрирован

-

Посещение

-

Победитель дней

2

Весь контент juvf

-

спасибо, кое что прояснилось в теории. Но теоретически лошадь, а практически упала. Как сделать параллельную шину. Как это делается практически? Открыл я твой компонент в Qsys. Что за сигналы lb и ub? Как изменить разрядность шины адреса? Как удалить не нужные сигналы? Так то у меня на этой шине ожидается 5..7 устройств. Я раньше брал и на старших адресах ставил дешифратор, на выходе которого получал чипселекты. Судя по альтеровской доке Avalon Tri-State Conduit Components User Guide можно сделать для каждого устройства свой тристэйт контроллер и через Tristate Conduit Pin Sharer посадить их все на одну шину с несколькими чипселектами. Такой вариант мне больше нравится. Но не получается. Как я делаю по "индусски": Требуется получить параллельную шину адресс, данные, и положительные сигналы чтения и записи. Добавил Generic Tristate Controller + Tristate Conduit Pin Sharer + Tristate Conduit Bridge. см рис. Скомпелял. Теперь пишу прогу. Как достучаться до памяти? пишу IOWR_16DIRECT(DAC1_BASE, 0, 0x100); - выполняю эту строчку и смотрю в сигналтабе сигналы своей параллельной шины. Сигналы не меняются. А на строке alt_u16 = IORD_16DIRECT(DAC1_BASE, 0); вообще прога виснет. Заходит в эту функцию и не выходит. Пробовал так alt_u16 = *(alt_u16*)(IORD_16DIRECT); Тоже на этом месте виснет. Как читать/писать в/из с параллельной шиной? Что я делаю не так?

-

Нужно из NIOS читать писать обычное статическое ОЗУ, по параллельной шине. Т.е. нужно в ниосе шина адреса, шина данных и управление - rd, wr и cs. Как собрать такой контроллер параллельной шины в Qsys? В SOPC-Builder собрал через Avalon Memory Mapped Tristate Slave и Avalon Tristate Bridge. Пытаюсь также в Qsys сделать - не получается. Почему-то в итоге сигнал wr из процессора выходит как inout, т.е. двунаправленный. Это я вообще не понял, что к чему. Как сделать простую, обычную, параллельную шину в NIOS с помощью Qsys?

-

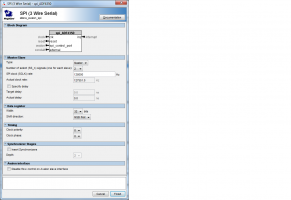

В Qsys добавил контроллер SPI мастер. Указал кол-во SS = 2. Генерирую процессор. На выходе получаю процессор у которого выводы описаны как input wire MISO_to_the_spi_ADF4350, // spi_ADF4350_external.MISO output wire MOSI_from_the_spi_ADF4350, // .MOSI output wire SCLK_from_the_spi_ADF4350, // .SCLK output wire SS_n_from_the_spi_ADF4350, // .SS_n вместо input wire MISO_to_the_spi_ADF4350, // spi_ADF4350_external.MISO output wire MOSI_from_the_spi_ADF4350, // .MOSI output wire SCLK_from_the_spi_ADF4350, // .SCLK output wire [1:0]SS_n_from_the_spi_ADF4350, // .SS_n Почему всего 1 чипселект? Бага в квартусе или в кусысе? Или у меня руки кривые?

-

Спасибо. Не сразу и поймёшь что это такая кнопка в Qsys-e. Действительно намутили.

-

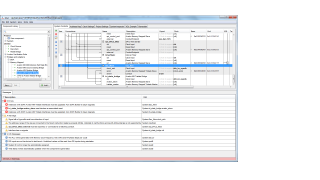

Не получается в Qsys добавить контроллер SRAM. А в SOPC всё получилось и работает. В Qsys делаю всё по аналогии. получаю ошибки, см рис. Это как? Запустил я SOPC Builder. Ни чего не обновилось. Может нужно в билдере открыть файл созданный в qsys-e? Но как? там разные расширения, я так понимаю что разные форматы. Потом должен быть в tri_state_bridge ещё какой-то ресет. А это что за ресет? А этот мост не сам создал, взял готовый из библиотек. Там нет ресета. Почему Qsys просит ресет?

-

А можно ваш проект как образчик посмотреть? У меня такая проблема.... Написал тест озу ддр2. Разместил всё в ончип. работает. и после вкл питания, и в дебаге. В дебаге наблюдаю в вкладке Memory свою ддр2. пишу в неё, читаю. Потом решил разместить код в ддр2..... пытаюсь дебажить..... при запуске дебага ошибка. elf загружается в ддр, но не проходит верефикацию...... иногда верификация проходит удачно, но дальше ошибка с сообщением assertion "m_state == STATE_DEBUG" failed: file "nios2oci.cpp", line 237 Using cable "USB-Blaster [USB-0]", device 1, instance 0x00 С тамбурином похожу вокруг платы.... ни чего не меняя с очередной попытки проскочит это место и вроде начнет выполняться программа, но не останавливается на main. где-то выполняется. остановлю руками, попробую прочитать/записать в ддр - работает. Не понятно где косяк. Думал что не так тайменги выставил в ддрКонтроллере, но когда всё в ончип - работает же. на ночь оставлял тест ддр - ни одного сбоя. А под дебагом грузится в ддр - не работает. Куда копать? Есть смысл ковырять тайменги в контроллере ддр? Или фазу ддр клоков подвигать? И что может быть за глюк?

-

А вы уверены что по умолчанию в мк зашит загрузчик? Я работал с этим мк, по мойму нет там ни чего в бутобласти. Есть в инете (возможно на алтере) готовый загрузчик. Запрограммировав его в бут область и прописав нужные фьюзы можно будет прожигать данный процессор через серийныё интерфейсы, по мойму с того же места качалась утилита для этого. Я писал свой загрузчик и свою утилиту. загрузчик через джитаг зажигал в мк. после этого я мог прожигать проц через уарт или через TCP/IP (с внешним контроллером тсп). Т.е. программа-загрузчик должна быть "залита" в МК заранее через какой-то программатор. ps более того, мы обычно авр-ки впаивали в плату и джитагом жгли. Но однажды попалась партия, где был снят фьюз разрешающий работу джитага. Пришлось со всей партии плат снимать мк и выставлять нужные фьюзы через программатор. А только потом запаивать в плату и прожигать ПО. Т.е. что там на заводе в проц по дефолту будет записано - это как звёзды лягут.

-

+1 Да ещё и инструкции нет. А в SOCP не работает одновременно epcs и ddr2, только порознь.

-

А есть инструкция у альтеры (или не у альтеры) как собирать процессор NIOS в Qsys? Например есть подробная инструкция как сделать процессор с DDRII контроллером в SOPC-Builder. А как тоже самое собрать в Qsys? Попробовал методом тыка - не работает. В sopc ddr добавляю - автоматом подцепляются s1. А в qsys кроме s1 ещё куча всяких сигналов. Куда их подводить? Сделал ход конём: создал процессор в sopc и конвертировал его в qsys-e - проц заработал. А если полностью создаю в qsys-e - не работает. Сравниваю с трансформированным - вроде всё одинаково, но проц не работает.

-

О!!! Спасибо за идею!

-

да я бы с удовольствием........... но указание сверху "Верхний уровень должен быть в схематике" ((

-

При генерации процессора в QSys графическое отображение всегда новое. Собираю процессор. Получаю графический блок который размещаю в графической схеме верхнего уровня. Делаю соединения с процессором. Потом что-нибудь в проц добавляю или меняю, проц пересобираю - получаю новое графическое отображение и которого все выводы перетасованы. Приходится по новой разбираться со всеми соединениями. Можно сделать так, чтоб например порядок выводов в epcs контроллере не менялся при перегенерации ниоса, как это было в SOPC-Builder?

-

Как в Altium сделать...

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Ага, спасибо. То что надо! Правда прозрачность не такая сильная как в алегро, но я думаю это дело привычки. -

Как в Altium сделать...

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

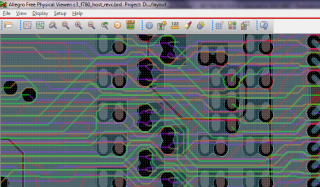

а это где? по L что-ли? так там hidden, т.е. скрыть. а мне нужно полупрозрачность. как например в алегро. Так-то можно цвет для каждого слоя настроить и указать бы там прозрачность, но в АД9 можно выбрать только RGB, регулировки альфа-канала нет (( -

Как в Altium сделать...

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

а не подскажете, как в редакторе пп сделать все/определённые слои полупрозрачными? -

Алтеровцы эклипс перепилили по своему. В NIOS IDE эти этапы добавляется в др месте. В редакторе BSP, вкладка main, ветка Settings->Addvanced->hal->make->.... под build_post_process: вбиваем то, что нужно сделать после сборки, под build_pre_process: вбиваем то, что нужно сделать перед сборкой.

-

Эта вкладка отсутствует в Eclipse под Nios. Алтеровцы эклипс перепилили по своему. В NIOS IDE эти этапы добавляется в др месте. В редакторе BSP, вкладка main, ветка Settings->Addvanced->hal->make->.... под build_post_process: вбиваем то, что нужно сделать после сборки, под build_pre_process: вбиваем то, что нужно сделать перед сборкой.

-

Подскажите преобразователь USB-RS232

juvf опубликовал тема в RS232/LPT/USB/PCMCIA/FireWire

Нужен готовый преобразователь USB-RS232, длинна кабеля не менее 1,5 метра, желательно 1,8. На чипе ftdi. Есть на эфо такие кабели, но короткие, 1м. Есть на просторах инета вроде кабели по 1,8 м, но на не известных чипах. Может кто знает, где можно приобрести сие чудо? -

:lol: Написал в службу поддержки в Atmel по этому вопросу. Ответ не долго заставил ждать.

-

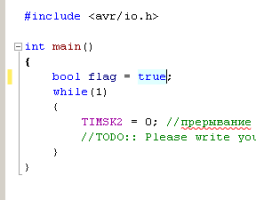

именно срр. Если сделать расширение с, то будет подсвечето то, то си знает, а bool и true подсвечены не будут. тока чтоб подсветка переключилась с си на с++ нужно после изменения расширения закрыть и открыть файл. Версия вот такая: Atmel AVR Studio 5 (Version: 5.0.1163). ставил из одного экзешника весом более 600 метров, в котором сразу ставился и визуал и .Net. вапрософ больше не имею. ((

-

эээээ....... подсветка синтекса чтоли? скрин из 5-ки. в четвёрке тоже есть. Скажите, а у вас проект срр собирается? Makefile сами писали или автоматический?

-

Не собирается проект на с++ в студии 5. Почему? Собрал новый С проект. Добавил в main пару строк #include <avr/io.h> ... TIMSK2 = 0; собралось. опции компилятора подставились как в настройках "C:/Program Files/Atmel/AVR Studio 5.0/AVR ToolChain/bin/avr-gcc.exe" -funsigned-char -funsigned-bitfields -O0 -fpack-struct -fshort-enums -g2 -Wall -c -std=gnu99 -mmcu=atmega169p -MD -MP -MF"eee.d" -MT"eee.d" -o"eee.o" ".././eee.c" меняю расширение файла на *.срр, запускаю компиляцию... не собирается, warning "device type not defined" и естественно ошибка, что неизвестно TIMSK2. Смотрю выхлоп сборки... "C:/Program Files/Atmel/AVR Studio 5.0/AVR ToolChain/bin/avr-g++.exe" -MD -MP -MF"eee.d" -MT"eee.d" -o"eee.o" ".././eee.cpp" В настройках проекта по прежнему выбран тот же процессор, но в avr-g++ почемуто не передается -mmcu=atmega169p. Почему? Как через гуй заставить студию собирать проекты на с++? ps в 4-ке все прекрасно работает на WINAVR. в 5-ке пробовал на WINAVR и на собственном студийном компиляторе (AVR Studio 5.0/AVR ToolChain) - результат один.

-

Как лучше записать дешифратор

juvf ответил juvf тема в Языки проектирования на ПЛИС (FPGA)

*WRITE* -

Как лучше записать дешифратор

juvf ответил juvf тема в Языки проектирования на ПЛИС (FPGA)

Большое спасибо за тест. я уже тоже после обеда хотел заняться этим. не успел. ps меня сомнения забрались. вроде реализации дешифратора асинхронные. почему вдруг там появилась синхронная схема? за обед ещё раз проштудировал что такое асинхронная и синхронная схема. Всем спасибо! pps Заглянул для интереса в RTL Viewer. У меня почему то вариант со сдвигом не так синтезировался -

Как лучше записать дешифратор

juvf ответил juvf тема в Языки проектирования на ПЛИС (FPGA)

Это понятно. В чем разница реализации сдвигового регистра и дешифратора? Время дешифрации? Кол-во вентелей? Кол-во памяти? Или просто время компиляции в квартусе?