-

Постов

1 610 -

Зарегистрирован

-

Посещение

-

Победитель дней

2

Весь контент juvf

-

Как правильно назначать диф.входы в Quartus-e?

juvf опубликовал тема в Среды разработки - обсуждаем САПРы

Добавил на схему пин clk. В пинпланере указал стандарт LVPECL. Автоматом создался clk(n). Назначил пин clk, автоматом назначился пин clk(n). При компеляции выскакивает ворнинг Warning: Pin "clk" is a differential I/O pin but does not have its complement pin. Hence, fitter automatically created the complement pin "clk(n)" Что я делаю не так? Как избавится от этого ворнинга? -

не понял, какой тестбенч "на первый и Ваш варианты"? У меня один тестбенч. test.v`timescale 1ps/1ps module test; reg FCLK; reg [3:0] rxIn; integer d; wire DCO; wire [13:0]Out1; wire [13:0]Out2; wire [27:0]Out3; lvds_Alt fpga( .FR(FCLK), .AdcData(rxIn), .DCO(DCO), .Out1(Out1), .Out2(Out2), .Out3(Out3) ); initial begin d = 27'h5555; rxIn = 0; end always begin #10000 FCLK = 1; #10000 FCLK = 0; end always @ (FCLK) begin rxIn[0] = d[13]; rxIn[1] = d[12]; rxIn[2] = d[13]; rxIn[3] = d[12]; #1428 rxIn[0] = d[11]; rxIn[1] = d[10]; rxIn[2] = d[11]; rxIn[3] = d[10]; #1429 rxIn[0] = d[9]; rxIn[1] = d[8]; rxIn[2] = d[9]; rxIn[3] = d[8]; #1428 rxIn[0] = d[7]; rxIn[1] = d[6]; rxIn[2] = d[7]; rxIn[3] = d[6]; #1429 rxIn[0] = d[5]; rxIn[1] = d[4]; rxIn[2] = d[5]; rxIn[3] = d[4]; #1428 rxIn[0] = d[3]; rxIn[1] = d[2]; rxIn[2] = d[3]; rxIn[3] = d[2]; #1429 rxIn[0] = d[1]; rxIn[1] = d[0]; rxIn[2] = d[1]; rxIn[3] = d[0]; #700 d = ~d; end endmodule а про *.sdc файл я пока низнаю, еще не выучил. :laughing: Что это такое и где его взять?

-

Ну вобщем победил я этот lvds. Без образцового проекта. Внешний PLL идёт лесом. вот как я его настроил (мож кому полезно будет, а может мне подсказка на будущее) Как подобное ацп подключить к ПЛИС СIII: Я делал в Quartus 10 SP1, на Win 7. Мож в ХР по другому нада 1)Визард мегафункция altlvds_rx просто так не вызвать. Идем в Пуск-Панель Управления-Языки и Региональные стандарты. Меняем Формат на Английские США. Некоторые рекомендуют дополнительно поменять разделитель с "," на ".", но у меня и с запятой вроде прокатило. После этого будет запускаться заветный визард. 2)для ацп ltc2267 я использовал тока FR и данные. Это двухканальное АЦП с двума линиями lvds для каждого канала. режим выбрал такой, как выше на рисунке. настройки для altlvds_rx смотри на рисунках. Некоторые вкладки в настройках lvds_rx были полностью заблокированны, поэтому этих рисунков нет. 3) ну собствено и всё. функциональное и временное моделирование в ModelSim прошли успешно. по переднему фронту rx_outclock данные на выходе валидны. Как в железке будет работать - пока не знаю. Данные замешанны так: rx_out[0...6] соответствует битам полученным по линии rx_in[0]. Первый старший. rx_out[7...13] соответствует битам полученным по линии rx_in[1] ну и т.д. Хороший документ, по ALTLVDS quartus_lvdswp.pdf

-

Ага, понял. Вобщем с PLL gate-моделирование проходит. Вытащил на графики входной клок и 3 выходных. По времени все так, как должно быть. Выставил я во внешнем pll теже задержки, что и в предыдущем проекте - на выходе altlvds_rx спрошные иксы. ((

-

ээээээ, я тока начал с квартусом работать,,,,,,,,, не понял что значит "только с мегафункцией pll". Я и так создаю с мегафункцией pll и altlvds_rx. Или вы предлагаете в 10-ке использовать только мегафункцию pll, а altlvds_rx не пользоваться и написать свою?

-

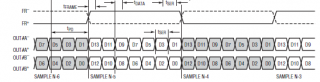

Задача - АЦП прикрутить к ПЛИС. ацп ltc2267 http://cds.linear.com/docs/Datasheet/22687614f%20.pdf Это двухканальное АЦП с двумя выходами lvds для каждого канала, плюс выход фреймов и data clock out, так же lvds. Входная частота ENC 100 МГц. Частота выборки 100 МГц, т.е. биты в lvds (dco) с частотой 700 МГц. Есть готовый проект для подобного АЦП но сделан в 9-ом квартусе. там мегафункции ldvs немного другие. Но на схеме верхнего уровня, в 9-ке приемный модуль выглядит также , как на моем рисунке в 10-ке. Да и настройки внутри altlvds_rx, старался сделать такие же. Поднять lvds тупо скопировав проект из 9-ки не получилось. решил разобраться. Почему внешний pll? - Те, кто уже поднял lvds, в 9-ке, сказали обязательно нужно пользовать внешний pll. Типа потом во внешнем pll легко двигать фазы и легко добиться всяких временных задержек. А с внутренней плл это гемору по горло и не пройдет временное моделирование. поверил на слово. ну и за основу взял их проект. Если я что не так делаю, подскажите что не так, плиз. ps И всё таки, где-то должно быть написано как на выходе модуля altlvds_rx данные выходят. Где какие биты. Я опытным путем уже это выяснил. Но как же документация? Не могу найти где конкретно это описано.

-

да я тоже сначало сделал без altlvds_rx. Функциональное моделирование прошло на ура. А временное почему-то не позволяет ни чего посмотреть. боссы говорят - попробуй поднять altlvds_rx. 96 МГц - а это какой клок? У меня есть клок FR (слова клокирует, ну есть еще DCO - клокирует данные, но я его не пользую. я его могу получить из PLL) По переднему и заднему фронту выравнивание слова (см картинку выше). Данные в линии lvds приходят с частотой 100 МГц, т.е. FR получается 50 МГц.

-

А что такое "тактируемая частота"? На входе altlvds_rx три частоты - rx_inclock, rx_readclock, rx_syncclock.Какую из них двигать? в какую сторону? в ModelSim. Функциональное моделирование прошло вроде успешно. Сейчас делаю временное. После компиляции в квартусе командой Tools->Run EDA Simulation Tool->EDA Gate Level Simulation... Там выбираю модель и Run - запускается в ModelSim симуляция. после остановки симуляции некоторые биты на выходе altlvds_rx почему-то x. Я его до дыр зачитал - не вижу я временных диаграмм с rx_inclock, rx_readclock, rx_syncclock и rx_in[]. Не понятно где и какие частоты должны быть, какие сдвиги?

-

Ну я подозреваю что где-то это всё разжёвано, и что где-то на это форуме наверно это уже обсуждалось. Но где? Не могу найти ни в хендбуке ни здесь (( ps Ну если бы ,,,, например посылаю на вход 0xcccc, в следующий кадр ~0xcccc, если бы данные на выходе были бы другие, но всегда одни и теже, например вместо 0xcccc всегда 0хаааа, то понятно, нада правильно выход распарсить, а у меня сейчас всегда данные разные. Не правильно както LVDS_RX рабортает, похоже я не правильно его клокирую

-

Как принять данные по LVDS в CIII?

juvf опубликовал тема в Среды разработки - обсуждаем САПРы

есть АЦП в выходом LVDS. Подключил к Cyclone III. Чтоб получить из этого LVDS пар. код в квартусе создал простой проект с altlvds_rx и pll (см рис). Написал тест имитирующий АЦП. Решил проверить в ModuleSim - принимается какойто мусор. Где можно почитать про altlvds_rx? Не понятно что за входы у altlvds_rx ? Какие клоки на них должны быть, какие фазовые сдвиги и относительно чего? Посмотреть бы временные диаграмы, как в даташите на АЦП. Что за выход в altlvds_rx ? Нужно два канала по 14 бит, у меня 1 канал 28 бит. Как его парсить? Как тока altlvds_rx получит кадр - через какое время этоти данные появятся на выходе? Когда данные на выходе валидны? Хендбук не помог :laughing: -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Ну при выравнивании там же. А без инструмента Tools/Interactive Lengh Tuning в верхнем левом углу при наведении курсора на проводник (Shift+H отключает и включает эту инфу) -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

1 это вопрос? если цепь от пада идёт прямой дорожкой, то длинна одна, если под кп или под via есть кусочки, или под кп дорожка ломанная, то длина дорожки другая. Наверно это недороботка АД, т.к. ад считает не физическую длинну дорожки, а ,,,,,,,, а векторную что ли, сумму длин всех кусочков. 2 ну про это я не знал. когда-нибудь попробую. Спасибо за совет :) Да с этим способом тоже не всё гладко. во первых нужно не забыть выключить остальные слои, чтоб случайно из др. соля нужное не удалить. Во вторых с "выделение рамкой" как-то не могу подружится. Если работаеш в room-e, то room кудато тащится. Удалил все комнаты, так если монтаж плотный, то при выделении рамкой, вместо выделения обязательно какой нибудь компанент или элемент схемы перетаскивается. Бывает эти ненужные кусочки под переходкой. Тогда выделение рамкой выделит и переходку. А её не нужно удалять. Сейчас аккуратней развожу, и часто могу предсказать когда и из-за чего появляются кусочки. Поэтому стараюсь избегать их появления. Но иногда они всёже появляются, реже чем раньше, но есть. ps еще чем мешают кусочки, тем что плата становится "тяжелой". Допустим плис, 484 ноги, под кажной по 4 не нужных кусочка - это около 2000 не нужных элементов на схеме. А эти 484 ноги кудато приходят, например на ОЗУ, там ещё столько же не нужных, в переходках ещё - вобщем схема становится очень "тяжелой". -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

1) Меня это беспокоило когда выравнивание делал. Эти ломанности добавляют погрешность в длинну цепи. 2) Бывает цепь развел, потом потребовалось в принципиальной схеме что-то изменить, одну связь ПЛИС добавить, приходится своповать, при чем иногда из-за одной цепи достаточно много переназначений делать. Ту часть дорожки, которая подходит к паду я удаляю, потом свапую и заного трассирую. Так вот когда остаются куча маленьких кусочков под падами, да которые на Тор не видно, т.к. они скрыты КП, переходками или дорожками, очень не удобно. Какие-то связи неразведённые показываются, почемуто цепь Net1 имеет связ с ногой 3, хотя по схеме связи нет. Оказывается под ногой 3 осталось с десяток маленьких кусочков дорожек, которые не видно, и эти дорожки подключены к цепи Net1. -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

AD Summer 09 Build 9.3.1.19182 У меня такие кусочки ставятся под падами, например ПЛИС и озу. Естественно даже мысли нет двигать плис по время трасиировки. Один раз устанвливаю плис, один раз устанавливаю озу согластно рекомендациям разработчиковю потом руками таскаю только дорожки. Via и элементы с разведёнными дорожками не таскаю. Печально что после того как развел, выравнил длинну проводников, обнаружил такие кусочки под падами и в переходках. При выравнивании длинна этих кусочков тоже учитывалась, хотя физически они длинны цепи не добавляют. -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

У меня Summer 09. Тоже есть такие кусочки, тоже доставляют неудобства. ПП не была импортирована. -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

ну понятно для чего он появляется. Для меня это очень не удобно. В схемном редакторе ни чего не появляется и очень удобно. Былобы не плохо чтоб подобные нестандартные "удобства" можно было бы отключить. -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Во всех редакторах, в том числе и в редакторе схем в АД по кнопкам Ctrl+C выделенный элемент копируется в буфер. В редакторе ПП в АД по кнопкам Ctrl+C что-то не понятное происходит - появляется курсор крест и нужно еще раз кликнуть, чтоб закончить копирование в буфер. Очень неудобно. Как от этого избавиться? Как сделать так, чтоб по кнопкам Ctrl+C происходило копирование в буфер также как это в схемном редакторе, без указания точки, относительно которой происходит копирование? -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Букав или цифры использовать для обозначения Part -- в Preference. Чтоб не менялся номер PART в свойствах компонента для этого PART сделайте LOCK Не понял? Это как? Вот в примере есть D1:10, D1:12, D1:1 - а должно быть сообветственно D1:1, D1:2, D1:3, т.е. part с ножками 36 и 37 должен быть пронумерован как D1:1.sss.7z -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Ну у нас схема на бумажный носитель врятли будет выводится. Так только если черновики. Умирают потихоньку бумажные носители. Может на какой-нибудь стадии производства и будет бумага. Но где? -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Ну замена шрифта - этот костыль точно мимо ((. Т.к. это придется на всех компах, где могут открыть проект, менять шрифт. Будем жить с двоеточием. (( -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Как настроить автонумерацию по ГОСТ? 1) Нумеруются компаненты D27:1, D27:2. А должны D27.1, D27.2 2)Нумерация должна быть сверху-вниз, слево-направо. УГО микросхемы, пусть D27, состоит из двух частей part A и part B. По свойствам ячейки А и В не одинаковы. Ячейка B на схеме левее ячейки А. После автонумерации самая левая ячейка(часть В) микросхемы пронумеровалать как D27:2, а правая часть как D27:1. Как сделать чтоб левая ячейка была D27:1 не зависимо от того какой part это из УГО - A, B, .... или G? В одной схеме есть мк/сх c уго из 7-ми ячеек - A,B,...G. Я использую только С и G. Они пронумеровались D5:3 и D5:7. Как такую схему читать? Где "не разработчик" будет искать D5:1? +1 -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

И всетаки, как пад делать многоугольный? Можно конечно поставить маленький пад, залить его многоугольным регионом. Потом такойже регион нужен в Top Paste и в Top Solder. Правда не понятно как потом правилами регулировать отступ маски от такого пада. А есть другой, более правильный способ? -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

А если Pad термопад должен быть не прямоугольный, а многоугольный? Например прямоугольник со скошеным углом - как тут быть? -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Ага, template человек делал, всё само проставилось. Спасибо. -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Спасибо. получилось. А как сделать автоматическую нумерацию листов? Как в поле "Лист" штампа автоматом ставить номер листа в проекте?