-

Постов

1 611 -

Зарегистрирован

-

Посещение

-

Победитель дней

2

Весь контент juvf

-

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

,,,,,, у упор не могу найти этой галки. В моей библиотеке всё нормально, а общую поделючил - в ней такая трабла -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Ну понятно. Новый фут принт будет с литерой. Ещё вопрос: Создаю уго. В свойствах пина есть Pin Name и Designator. Задал и то и другое. Галки Visible сняты. Но в редакторе УГО отображаются и имя и десигнатор. Хотя при вставке в схему эти обозначения пина не видны. Но в редакторе уго видны. Почему? Раньше такого не было. Причем такая багфича появилась у двух разработчиков. -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Но пока так и вышел из положения. Тут же, тоже самое сделал с кондёнсатором. всё заменилось. ??? Правда в предыдущем, был резистор, там птарен в новой, в CommonLib был едентичен старому, т.е. создан через копипаст. А конденсатор был сделан с нуля. нада понаблюдать, может в этом проблема. может с копипастом какиенибудь ID передаются и поэтому в ПП паттерн не меняется? -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

нирисовал компанент, уго + паттерн. поместил в библиотеки myLib.SchLib и myLib.PcbLib . Добавил его на схему. Нужно компанент заменить на другой, который в другой, подключённой к проекту библиотеке, в CommonLib. Удалил из схемы элемент из библиотеки myLib , вставил из точно такой же из CommonLib. В CommonLib есть и уго с паттерн. изменил схему. делаю update PCB. смотрю в ПП, смотрю свойства этого компанента: SCH Library CommonLib, а footprint почемуто из старой библиотеки, из myLib.PcbLib. Почему? Яже полностью заменил компанент. в уго ссылка совершенно на другой паттерн. почему паттерно не меняется в ПП? -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Это как? т.е. в базе тыщя - две элементов и сделать каждый компанент в отдельный файл. а что значит отдельный файл? отдельную базу элементов? т.е. будет либов столько - сколько компанентов + все паттерны? Как-то криво. -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Спасибо, то что нужно. А еще вопрос. Вот есть общая база уго и паттернов. эта база лежит в репазитории свн. пользуют её много народу и у каждого на компе рабочая копия. требуется чтоб все могли редактировать базу. Т.е. понятно что если два человека будут редактировать один и тот же компанент, то будет конфликт. Но если один редактирует одну микруху, другой другую - то по идеи конфликта нет должно быть. Но база, на сколько я понял - это бинарник, и на сколько мне известно subversion не может сливать бинарники, т.е. subvrsion выдаст конфликт. Есть какое нибудь решение данной проблемы? Нужно чтоб 2 пользователя одновременно редактировали разные компаненты в рабочих копиях, потом сливали в репазиторий и svn сливал это без конфликтов. -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

создал в редакторе PCB класс компанентов и правило для этого класса. поправил схему. обновил ПП. Класс компанентов удалился. Как мне быть? Как создаются классы в схеме? -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Задал правила для подтекания термопадов. Design->Rules->Plane->PologonConnect. В правиле указывается кол-во соединений пада с полигоном (2 или 4) и толщину соединяющей дорожки. Как изменить зазор между полигоном и падом? -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Не работает ввод символа F в поиске элемента в библиотеке (на рисунке строка, где введено '*HM'). Может быть за F зарезервированно что-то и это что-то не позволяет вводить f и F? -

FAQ по Altium Designer

juvf ответил masterofnature тема в Altium Designer, DXP, Protel

Схемный редактор PCB редактор Вопрос Как зеркально отобразить УГО или посадочное место? Ответ Взять мышкой объект и нажать X или Y, в зависимости от того, по какой оси нужно отзеркалить. -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

А где эта кнопка? ааааа,,,,, нашел Tools » Mode » Add. Ну так это не то. это ..... как написанно в доке "Creating an Alternate View Mode for a Part", и это мне не подходит, т.к. Each alternate view mode should always have the same set of pins as the Normal mode. Мне же нужно отобразить разъем по разному. в одной схеме нужно 40 пинов, в другой нужно 3 парта по 10 пинов, в третьей один парт 2 пина, второй 7 пинов, третий 4 пина, ,,,,, седьмой парт 5 пинов. Должно быть 3 разных уго, в каждом разное кол-во партов с разными пинами. таокое Возможно? -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Вобщем есть в библиотеке компанент. Например разъем на 40 ног. Это УГО из одного парта, все ноги попорядку. Для некоторых схем такое уго неудодбно. Нужно поменять порядок ног и нужно разбить этот разъем на 3 парта. Сделал дубликат компанента в библиотеке и в дубликате сделал праты так, как мне нужно. Вопрос, как можно сделать 1 компанент в библиотеке, но чтоб у него было несколько разных УГО? -

Помогите с ALTSQRT

juvf опубликовал тема в Среды разработки - обсуждаем САПРы

не могу собрать этоту мега фукцию. Добавил в схему, настроил. При анализе получаю ошибки Error: Illegal wire or bus name "radical[]" of type port Error: Illegal wire or bus name "q[]" of type port Что за ошибка? Почему порты называются radical[] а не radical[31..0]? -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Владимир, а перевести на русский можно? Я еще не силен в сленге по AD. Прочитал "все литы проект" как "все листы проекта", даже не заметил, что есть опечатка. :) Опять не оплучается. Открыл все схемы. выделил нужный объект - FSO, Type отметил Same. Нашел на 7-ми листах 30 кондёров. То что нужно. Что дальше? В инспекторе ресурсов меняю тип на нужный - в результате поменялся только тип кондёров на текущем листе. Приходится ползать по закладкам и во всех листах делать тоже самое. А как то по др. можно? -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

не получается. как там менять? А это как? У меня тип кондёров прописан в .... в свойствах компанента в поле Type, см рис. Лазию по всем компанентам, открываю у всех свойства и правлю. как можно это сделать проще? -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

Если задать сетку равную шагу переходок то руками достаточно быстро получается и каждая виашка под контролем. а вопрос, может в офтоп, но все же - на вашем рисунке полигон сеткой. Для чего сеткой? Сколько я не искал ответа на это вопрос нашел один вразумительный - раньше, при ссср, старый гетенакс (или текстолит) выделял газы. Если полигон залить сплошной, то эти газы вспучивали полигон и он отслаивался. Современные материалы не страдают газами, поэтому полигоны можно делать сплошные. К томуже при сплошном полигоне меньше меди нужно стравливать, меньше химикатов затратися, меньше загрязнений. Для чего у вас полигон сеткой? Мож там СВЧ какой нить? Или это разработка 80-х годов? -

Altium для новых начинающих

juvf ответил Uladzimir тема в Altium Designer, DXP, Protel

в третий раз меняют комплектацию, в 3-ий раз переделываю руками типы у компанентов. как в альтиуме автоматом поменять все поля Type во всех конденсаторах с GRM155R71C104KA88D на C0402C104K8PAC? -

ну не обращять внимания на предупреждения на момент создания проца, можно, но потом все равно буду избовляться от ворнингов. Тем более что процессор один раз в начале собирается, потом врятли будет пересобираться. Негоже проект компилять с несколькими сотнями ворнингов. За каждым ворненгом прячутся баги!

-

Спасибо. помогло. -30 ворнингов сразу.

-

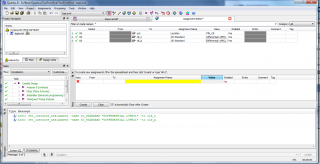

Собрал ниос с контроллером sdram и с джитагом. Добавил в Sdc файл свой клок create_clock -name {clock} -period 20.000 -waveform { 0.000 10.000 } [get_ports {clock}] получил критичиские предупреждения Critical Warning: From altera_reserved_tck (Rise) to altera_reserved_tck (Rise) (setup and hold) Critical Warning: From altera_reserved_tck (Rise) to altera_reserved_tck (Fall) (setup and hold) Critical Warning: From altera_reserved_tck (Fall) to altera_reserved_tck (Fall) (setup and hold) Critical Warning: From clock (Rise) to clock (Rise) (hold) Critical Warning: From clock (Fall) to clock (Rise) (hold) Critical Warning: From clock (Rise) to clock (Fall) (hold) от этого есть лекарство - нужно прописать времена задержек set_clock_uncertainty. Но какие они должны быть? Не понятно. Какие они должны быть для altera_reserved_tck и для clock?

-

Собрал ниос с помощью SOPC-Builder. Компилирую. Получил кучу варнингов Warning (10037): Verilog HDL or VHDL warning at sdram_0.v(313): conditional expression evaluates to a constant смотрю sdram_0.v // Delay za_valid to match registered data. always @(posedge clk or negedge reset_n) begin if (reset_n == 0) za_valid <= 0; else if (1) za_valid <= rd_valid[2]; end индуский код. Что за if(1)? Это теперь вручную ползать по коду и исправлять за квартусом или мож где в сопс-билдере галочку поставить "Без индуского кода"?

-

Да кого просмотрел то? Непойму. Клокдистребъютер дает клоки Differential LVPECL. При чем тут вообще ацп и лвдс? Наконец-то подключил дифпару через примитив без предупреждений. Назначения делал вручную в *.qsf, но через руки допёрло как можно через редактор ассигнований тоже самое делать. Всем спасибо.

-

В этой теме я про АЦП ни слова не сказал. В схеме с ацп - там да, там клоки с FR-а беру, lvds-ные. Тут другая задача. Но lvds или lvpecl - проблема одинаковая: подключить диф. пару без предупреждения.

-

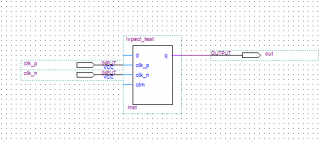

собрал я ваш пример. Собираться - собирается, а как назначить пины - не пойму. Подключил я ваш *.v к проекту, сгенерировал из него символьный файл. Добавил в проект верхнего уровня. Захожу в пинпланер - он показывает стандарт у clk_n и clk_p как 2,5 (Default). Меняю стандарт на lvpecl - получаю четыре пина clk_p, clk_p(n), clk_n, clk_n(n). что за файл *.qsf? Так как всё таки пины назначить?

-

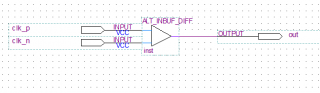

За f1 спасибо. Не знал про такую фичу. А почему не lvds - потому что не lvds. У меня приходит дифпара от др. схемы стандартом LVPECL :laughing: Ни как не могу понять, как назначать пины примитиву ALT_INBUF_DIFF? Добавил на схему примитив, назначил входы. а где указать что clk_p - это пин G21?