-

Постов

554 -

Зарегистрирован

-

Посещение

Весь контент Jurenja

-

Ток утечки затвора транзистора PSMN2R4-30YLD

Jurenja ответил haker_fox тема в Схемотехника

Затвор изолирован от стока/истока и канала диэлектриком, диода там нет. Утечка от затвора м.б. и к стоку, и к истоку, и к области канала. Моделирование будет правильным только если модель полностью адекватна насчёт утечки затвора, но это вряд ли. Самое надёжное - измерять, причем в используемых режимах и в диапазоне температур. -

Ток утечки затвора транзистора PSMN2R4-30YLD

Jurenja ответил haker_fox тема в Схемотехника

Но есть смещение затвора относительно стока. -

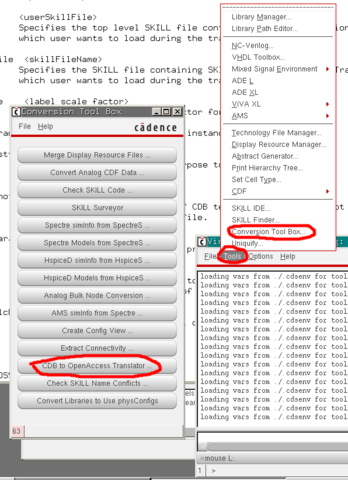

Список слоёв сконвертится при конвертировании так называемой технологической библиотеки. Нужно будет только вручную скопировать файл палитры display.drf. Серьезных ошибок не было. Самое распространённое это временные ошибки когда в сконвертированной библиотеке есть ссылки на ещё несконвертированные библиотеки (или их старые версии, в которых чего-то не хватает).

-

Если запустить утилиту без параметров, то она выдаст достаточно полный help про свои возможности. Обычно использую утилиту с такими параметрами (пример трансляции библиотеки с названием PRIMLIB. cdb2oa -cdslibpath cadence5_lib_location/cds.lib -lib PRIMLIB -oalibpath cadence6_lib_location/PRIMLIB -log run_cdb2oa.PRIMLIB.gui.log -ignorelocks -report -mapundefinedpingroups strong Предварительно нужно распаковать cdb библиотеки в каком-то месте и сделать там актуальный для них файл cds.lib, утилита его использует. cadence5_lib_location и cadence6_lib_location - пути для библиотек кэденса 5 и 6 соответственно. PS. Еще в кэденсе 6 есть gui для этого же, но этим не пользовался и ничего про это не знаю:

-

Ручной выбор VCO в MAX2871

Jurenja ответил ppram5 тема в RF & Microwave Design

Пытаетесь использовать VCO без PLL? У VCO всегда будет какой-то разброс частоты. -

Сверхлинейный умзч на мосфетах

Jurenja ответил decoder2 тема в Вопросы аналоговой техники

Это примерно -122.7 дБ. Расскажите как измеряете такие искажения на изготовленной аппаратуре? Вопрос не про моделирование. -

Сверхлинейный умзч на мосфетах

Jurenja ответил decoder2 тема в Вопросы аналоговой техники

По R3 входной ток ОУ не протекает - изолирован разделительным конденсатором. Поэтому учитываем только R10. -

Сверхлинейный умзч на мосфетах

Jurenja ответил decoder2 тема в Вопросы аналоговой техники

Наверняка для компенсации входного тока ОУ. -

В кэденсе 6 есть транслятор датабаз (библиотек) из кэденса 5, утилита называется cdb2oa.

-

Обычно что-то такое (туториалы итд) есть внутри дизайн китов от западных фабрик, причем это скорее перечень особенностей для правильного использования этих дизайн китов. Но дизайн микросхем это намного сложнее чем просто умение пользоваться кэденсом (редакторы схем, топологии итд; симуляторы...). Поэтому польза от туториалов в обучении дизайну микросхем очень сомнительная. А для изучения именно кэденса внутри его есть очень обширная документация. Если интересен именно дизайн микросхем, то нужно начинать с профильных книжек. имхо.

-

Вопросы по Cadence Virtuoso

Jurenja ответил APEHDATOP тема в RF & Microwave Design

А какое значение параметра C? Если нужна максимально возможная частота, то эти конденсаторы нужно убрать: емкости затворов достаточно более чем. -

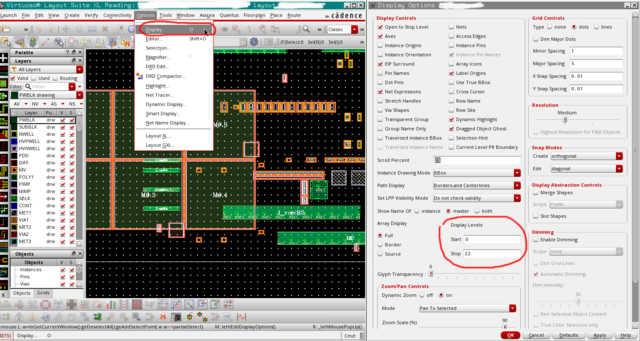

Вопросы по Cadence Virtuoso

Jurenja ответил APEHDATOP тема в RF & Microwave Design

Вам нужно отрегулировать глубину отображения топологии, т.е. на сколько уровней вниз по иерархии нужно видеть топологию. На картинке показано где это в настройках. А "descend read" это совсем про другое. -

Есть варианты, в которых проволоку не используют. Вот тут показано несколько вариантов, в качестве иллюстрации.

-

Минимум, с которым можно сделать обработку сигнала - это 2.

-

CMOS SPICE MODEL OPEN SOURSE

Jurenja ответил Credo213 тема в В помощь начинающему

Названия не знаю. -

CMOS SPICE MODEL OPEN SOURSE

Jurenja ответил Credo213 тема в В помощь начинающему

Есть масса технологий, для какой-то из них такая модель будет правильной. Если вы будете проектировать что-то для какой-то определённой фабрики, то логично взять у неё эти модели. Ниже добавил модель, использованную в одном реальном проекте, который делали для одной китайской (континентальной) фабрики. * .MODEL tn_bc NMOS LEVEL=3 +UO=546.1 +VTO=-5.0 +NFS=6e10 +TOX=130.0e-10 +NSUB=9.717e16 +VMAX=95.39e3 +RSH=1000 +XJ=0.25e-6 +LD=0.08e-6 +DELTA=15.59e-3 +THETA=54.48e-3 +ETA=25e-3 +KAPPA=177e-3 +JS=20e-9 +WD=-0.2e-6 +CJ=499.5e-6 +CJSW=2.336e-9 +CGBO=7.76e-10 +CGDO=4.32e-10 +CGSO=4.32e-10 +MJ=0.491 +MJSW=0.059 +PB=0.794 +PBSW=0.755 +FC=0.5 -

CMOS SPICE MODEL OPEN SOURSE

Jurenja ответил Credo213 тема в В помощь начинающему

Поправьте значение параметра VTH0 на отрицательное, будет встроенный канал. -

Тогда топологию рисовали на аппаратах с названием "Кулон-1". Смотрели в монохромный запоминающий ЭЛТ с размером экрана 10х10 см. Информацию на изготовление шаблонов отдавали на магнитной ленте. ps. Фото "Кулон-1" есть на стр.12 (их там 2 шт.): https://www.computer-museum.ru/histussr/История развития и внедрения САПР ИЭТ в МЭП2.pdf

-

Это были примерно 80-ые, поэтому никак не 1 мкм. 2.5...3 мкм более реалистично, но и 5 мкм вполне возможно.

-

Вполне возможно, что исчезнут заказчики (а точнее - у них исчезнут деньги) по причине полного коллапса экономики. И проблема нехватки микросхем итд решится сама собой.

-

Что такое LF и HF ?

Jurenja ответил Damyen тема в В помощь начинающему

высокие частоты и низкие частоты (High Frequency и Low Frequency) имхо -

Так и есть, микросхема на выходе производства проверяется. Но на этапе производства каждый элемент внутри кристалла и каждая связь между этими элементами - не проверяется.

-

В современных процессорах, изготовленных по КМОП технологии, бит - это напряжение.

-

Перед сборкой суперкомпьютера каждый процессор (и любой другой блок) проверяется на работоспособность, неработающие отбраковываются.

-

Теоретически, при идеальном качестве изготовления, такого ограничения нет. Но т.к. качество связей между элементами и качество самих этих элементов не идеально, то есть некоторая малая вероятность того, что связь будет работать неправильно, т.е. будет или разрыв связи, или закоротка на другие связи, или неработающий эленмент, или любые другие произвольные комбинации таких событий. В таком случае (применение резервирования не рассматриваем) вся система окажется неработоспособной. Вероятность отказа системы очень быстро растет с ростом количества элементов и связей между ними. Поэтому если захотеть изготавливать что-то суперсложное, то процент выхода быстро будет приближаться к нулю. Это приведет к резкому удорожанию изделий и уменьшению надежности тех образцов, которые случайно оказались исправными.