dmitry-tomsk

Свой-

Постов

846 -

Зарегистрирован

-

Посещение

Весь контент dmitry-tomsk

-

Vitis 2023.2

dmitry-tomsk ответил Alex77 тема в Среды разработки - обсуждаем САПРы

Как-то рано ставить 2023.2, весит вдвое больше, а vscode совсем сырой, в старых проектах hls много красных подчёркиваний в исходниках, хоть и синтезирует верно, ap_uint<1> в bool даже не признаёт конвертацию. Перенос старых hls ip у меня так и не заработал. -

Мне понравилось vhdl + hls, hls время экономит кучу, симуляция и упаковка ядер на автомате, ну и cpp все знают, учить не надо. Немного привыкнуть нужно, что выполнение кода посдедовательное, так что кое-где нужно временные переменные вводить, чтобы на комбинаторику на нарваться, а так всё супер.

-

UVM vs OSVMM

dmitry-tomsk ответил OparinVD тема в Методы и средства верификации ПЛИС/ASIC

hls генерирует тестбенчи с использованием uvm , так что вивадо должен поддерживать -

Подскажите, пожалуйста, как считать адрес для записи в UFM1 matchxo3 через MicoEFB_UFMSetAddr?

-

Спасибо, оказалось нужен был sp1 для диамонта

-

Кто работал с lattice mico8, почему кнопка generate в lms не активна?

-

Спасибо. А что за плата? Чей дма контроллер? Мы планировали свою рисовать без теста на макете, скорость нужна хотя бы 40.

-

Подскажите, пожалуйста, кто работал с аппаратным блоком pcie artix ultrascale+ pcie4 какую скорость удалось полчить в режиме pcie4 x4 линии?

-

под windows windriver выдаёт склеенные страницы, когда делаешь lock памяти уровня пользователя. Склеивает до 144 страниц, в результате число дескрипторов меньше числа страниц в среднем в 10 раз. Блочной памяти 4kx64бит хватает для описания 160 МБайт памяти.

-

пауза for (int i = 0; i < 10000; i++). Менял на 100000 без разницы. Сейчас другой работой занят, на следующей неделе буду дальше копать.

-

Спасибо, попробую.

-

Прерывания не используются пока, через pio идёт опрос регистра состояния, dma от этого не зависит, кроме случая, когда буфер в пк полный. Увеличение размера буфера не влияет. Подозрение на функцию WDC_DMASyncIo, может она как-то влияет на root complex. С драйверами не разбирался, не знаю, что она делает.

-

Платформа intel i7 8700, чипсет не помню, jungo windows 10 драйвер. Кэширования не включал, после получения адреса очередного пакета в кольцевом буфере через pio делаю WDC_DMASyncIo(pDma).

-

Благодраю откликнувшихся. TLP - 128, корка своя, пакеты по два мегабайта, поток напрямую, кольцевой буфер в ПК - 16 МБайт. Думал, что влияет опрос готовности, но не похоже. Что-то нужно придумать, чтобы отловить большие простои на s_axis аппаратного блока pcie, чтобы узкое место найти

-

dma, pcie 2.0 x8

-

Ошибку нашёл, только скорость ввода в пк получилась не больше чем 3020 МБ/s. Хотелось бы узнать, у кого какая получилась?

-

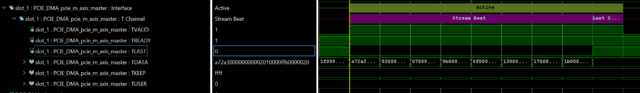

Коллеги, у меня проблема попроще. Дошли руки до своего контроллера для kintex-7 325t. Пишу пакет mwr64 в корку - а ответ тишина. Драйвер под win10 - jungo 12 с ftp. Лочу память через dwStatus = WDC_DMASGBufLock(hDev, pBuf, DMA_FROM_DEVICE | DMA_ALLOW_64BIT_ADDRESS, size, &pDma). С начала страницы передаю один пакет 128 байт, а в памяти нули. Пакет на картинке, bus master enable в 1. Порядок байт в данных переставляю, а в адресе нет. Может в этом проблема?

-

у pcie в pl нет ни адреса, ни ресуров. К нему мост или xdma нужно сначала прикрутить

-

pcie блок там вроде же в pl. При чём тут dev tree?

-

Для всех семейств, с гарантией всех бит handshake или асинхронное fifo на srl. В вивадо такая гарантия редко нужна, s_axi_lite может на любой частоте работать, вивадо автоматом синзронизацию добавляет.

-

Казахстанская?

-

Подскажите, у кого работает перевод долларов из-за рубежа? Казахстанские карты работают на приём?

-

В вивиадо эти уже давно никто не пользуется. Там для этого теперь xpm макросы, зайдите в language templates, cdc ищите, там разны есть, на все случаи жизни xpm_cdc_single #( .DEST_SYNC_FF(8), // DECIMAL; range: 2-10 .INIT_SYNC_FF(0), // DECIMAL; 0=disable simulation init values, 1=enable simulation init values .SIM_ASSERT_CHK(0), // DECIMAL; 0=disable simulation messages, 1=enable simulation messages .SRC_INPUT_REG(1) // DECIMAL; 0=do not register input, 1=register input ) xpm_cdc_single_inst ( .dest_out(dest_out), // 1-bit output: src_in synchronized to the destination clock domain. This output is // registered. .dest_clk(dest_clk), // 1-bit input: Clock signal for the destination clock domain. .src_clk(src_clk), // 1-bit input: optional; required when SRC_INPUT_REG = 1 .src_in(src_in) // 1-bit input: Input signal to be synchronized to dest_clk domain. );

-

В pcie есть flow control, можно в теории к нему подключитсья и посмотреть число свободнах буферов для разных типов tlp. Не в курсе, можно ли это сделать для xdma. Если буферы свободные есть, значит виною кривая архитектура драйвера-xdma. Под windows он на приём вообще скорость на порядок губит. Я в своё время пробовал его ставить, плюнул, отложил до лучших времён. alinx с kintex только приехала, как дойдут руки сделаю свою корку и отпишусь. У меня задача выжать максимум на приём, так как нужно 16 плат ацп на 400 мбайт в секунду подключить к пк.

-

Куплю АЦП LTC2195CUKG или LTC2195IUKG

dmitry-tomsk ответил SDM_Electronix тема в Куплю

320