-

Постов

2 052 -

Зарегистрирован

-

Посещение

Весь контент Krys

-

сигналы входные или выходные обнуляются? Чтобы входные не обнулялись, нужно нажать на названии сигнала, правой кнопкой, выбрать stimulus, задать нужный вид стимулятора. Если Вы хотите сигналы нарисованные собственной рукой, то нужно поставить стимулятор под названием custom. Иначе - выберите нужный тип стимулятора. Если стоит стимулятор не Custom, то этот стимулятор перетирает при каждой новой симуляции нарисованные Вами вручную сигналы.

-

библиотека simprim использует примитивы для временной симуляции. Они называются с префиксом х_. Библиотека unisim содержит примитивы для функциональной (поведенческой) симуляции. При временной симуляции имплементатор перелопачивает ваш допустим верилог-файл исходника в другой верилог-файл симуляции, в котором перечислены исключительно примитивы с префиксом х_. Также имплементатор подготавливает некий файл, в котором для каждого конкретного экземпляра примитива заданы задержки, которые он вносит. Для временной симуляции не требуется сам исходник, но требуется верилог-файл с примитивами х_ и с задержками. А также библиотека simprim. Для функциональной симуляции требуется только исходник и библиотека unisim (и то - если в исходнике используются из неё примитивы. Если не используются - то библиотека не нужна). Надеюсь, немножко внёс ясность в Ваши вопросы. Если что - спрашивайте. Я недавно с этим разобрался.

-

правильно то правильно. Но как это решать? Это действительно проблема...

-

Altium Designer для деревянных:)

Krys ответил Буратино тема в Altium Designer, DXP, Protel

Нашли? Обычно обновление и вызывает пересчитывание. Да... похоже нет... значит где-то ещё обсуждалось здесь же... Сейчас нет под рукой АД. Но помню где-то здесь надо искать: DXP -> Preferences -> System -> Найдёте - отпишитесь в ФАК, чтобы таки этот ответ там появился наконец-то. -

Ошибки работы Altium Designer

Krys ответил inter_pro тема в Altium Designer, DXP, Protel

Вот уж точно бага: для галочки "Force Complete Tenting on Bottom" не работает отражение свойств при переходе на противоположный слой. Когда я компонент перенёс на Bottom эта галочка должна позволять заливку маской на Top. А она продолжает действовать для Bottom. Галочку я поставил для пада в составе компонента. А уже компонент переворачивал. Пад имеет хитрую форму (см. здесь). -

Как в Altium сделать...

Krys ответил Uladzimir тема в Altium Designer, DXP, Protel

Небольшое введение: мне нужно было сделать компонент в виде контактной площадки для припайки провода. Компонент с отверстием. Верхняя сторона (куда будет припаиваться провод) является прямоугольной, вдоль провода. Для рационального использования длины контактной площадки отверстие сместил к краю площадки. Отверстие на всякий случай металлизированное, поэтому с ответной стороны решил тоже сделать "кольцо" из меди. Но поскольку отверстие смещено, то кольцо пришлось мимо отверстия. Поэтому я кольцо нарисовал в виде PolyRegion, а размер пада на нижнем слое установил нулевым. Всё замечательно, только на плате правила ругаются на малые зазоры между падом и этим PolyRegion. Суть вопроса: как создать поисковый запрос, чтобы он выдавал все примитивы в компонентах, у которых свойство Footprint имеет определённое одинаковое значение? Я сначала втупую попытался указать в правилах только строку запроса Footprint = blablabla, но потом понял, что сами примитивы, на которые мне нужно создать правило для зазора, не имеют свойства Footprint. Это свойство имеет только их Owner. Но я не знаю, как в поисковом запросе "достучаться" до Owner'а этого компонента. Пока решил вопрос добавлением вручную всех нужных мне компонентов в определённый компонент класс. А в правилах указал InComponentClass (blablabla). Но мне это решение не нравится тем, что компоненты нужно добавлять вручную. Хоть это и нетрудно, но хочется докопаться до истины... или вот ещё: подвёл к такому компоненту дорожку, не спасло правило выше. Ошибка короткого замыкания между дорожкой и тем PolyRegion, который в составе компонента контактной площадки. Нужно сказать, что если этот PolyRegion пересекается с дорожкой, имя цепи которой совпадает с именем цепи пада того же компонента, которому принадлежит и данный PolyRegion, то для таких объектов допускается короткое замыкание. Пока решил эту проблему через Design - Netlist - Update Free Primitives From Component Pads. Но вдруг бы у меня этот PolyRegion не касался пада этого компонента?... Тогда бы ничего не получилось. -

synplify

Krys ответил DevL тема в Среды разработки - обсуждаем САПРы

Не понял вопрос. Спасибо. Вижу, что разница в этом: Physical Design Design Plan File Logic Assignment to Regions Area Estimation and Region Capacity Pin Assignment Physical Synthesis Optimizations Только не понимаю всё равно. Что мне это даёт? Точнее, я не очень понимаю в деталях, что это за операции. Какой у них аналог, скажем, в ISE? Какие действия ISE я могу заменить этими фичами Синплифая? И главный вопрос: как научиться этим пользоваться? Если кому нетрудно, выложите, пожалуйста, пошаговую инструкцию, что куда нажимать. Пока тыкаюсь в Синплифай, как слепой котёнок. Создал новый Job типа Implement, попробовал запустить. Синплифай вызвал из скрипта некий exe-шник от ISE, который и произвёл операцию Implement. Вот я и не понимаю: все эти функции, перечисленные выше: Physical Design Design Plan File Logic Assignment to Regions Area Estimation and Region Capacity Pin Assignment Physical Synthesis Optimizations Они реализованы просто как скрипты, всё равно вызывающие exe-шники от ISE или это самостоятельные и самодостаточные инструменты Синплифая? Другими словами: если для выполнения этих функций всё равно требуется наличие ISE на диске, то зачем мне нужно пользоваться этими фичами из Синплифая. Я могу тогда их прямо из ISE и вызвать... Короче одни вопросы... -

Объединение шин

Krys ответил skyvmicro тема в Работаем с ПЛИС, области применения, выбор

-

synplify

Krys ответил DevL тема в Среды разработки - обсуждаем САПРы

Я бы сказал так... временная симуляция после этапа RTL-синтеза хоть как-то физически отражает поведение по сравнению с функциональной симуляцией. Но результаты этой симуляции не стОит считать хоть как-то достоверными. Наибольшую достоверность даёт Post-PAR симуляция. Следовательно, симуляция после этапа RTL-синтеза получается и не нужна. Хотим быстро - пользуемся функциональной симуляцией. Хотим точно - пользуемся Post-PAR симуляцией. Хотим неопределённо - пользуемся симуляцией после этапа RTL-синтеза :))) А я всё равно не понял :) Разжуйте, пожалуйста. -

-

FAQ по Altium Designer

Krys ответил masterofnature тема в Altium Designer, DXP, Protel

Я тоже так думаю. Но указать на фак мы должны. Иначе нас же завалят вопросами. А то, что ссылка на фак указана в первом сообщении темы "как сделать..." - дак кто ж его читает - первое сообщение... если там десятки страниц... никто ж не знает, что в первом будет что-то важное. -

Как в Altium сделать...

Krys ответил Uladzimir тема в Altium Designer, DXP, Protel

думаю, это стОит добавить в фак (про BOM) -

Да хорош мазаться. Так все говорят. Там делать нечего - 2 пальца об асфальт. Вопрос - ответ. Кратко. А Вы, как маленький, ломаетесь :) Нужно браться и делать. Никто же за это не наругает, что костноязычно написано.

-

Я только увидел. А что, обязательно нужны комментарии? :) Похвалите сам себя (сам себя не похвалишь - никто не похвалит) :))) Мне понравилось. Всё, что требуется, ничего лишнего. Кратко и с картинками. Сохранил себе в свою "библиотечку" документации по АД. Дополню: это вот тут: http://electronix.ru/forum/index.php?showt...mp;#entry864743

-

Разъем USB-MINI в Altium

Krys ответил zheka тема в Altium Designer, DXP, Protel

Да, Вы правы. Непрофессионально было брать распиновку где попало :) Спасибо за ссылочки. Зачастую мы пугаемся, что стандарты "под замком" (типа IEEE), а они на самом деле в свободном доступе. А мы лезем на википедии и просто куда попало :) -

Объединение шин

Krys ответил skyvmicro тема в Работаем с ПЛИС, области применения, выбор

Аналогичный вопрос: как это же сделать в Active-HDL? :) Я в квартусе активно в графике рисовал. Там был примитив назывался, кажется, wire2wire (если ничего не путаю). Слева - цепь с одним именем, справа - цепь уже с другим именем. И ещё был примитив bus2bus - аналогичное действие для шин. -

Ошибки работы Altium Designer

Krys ответил inter_pro тема в Altium Designer, DXP, Protel

Извиняюсь, если не очень въехал в проблему. Но у меня была похожая проблема, когда трассы каким-то волшебным образом залочились после применения инструмента интерактивной разводки шин (больше им не пользуюсь от греха подальше). Попробуйте посмотреть на галочку, залочены ли трассы (в панели PCB, если не путаю). -

FAQ по Altium Designer

Krys ответил masterofnature тема в Altium Designer, DXP, Protel

Владимир, предлагаю внести эту тему обратно в "неспускаемый заголовок" списка тем по АД. А то люди похоже её не видят и начинают задавать вопросы, создавая отдельную тему. А ещё, я так понял, что в самом первом сообщении ссылка не на самый свежий фак. А найти самый свежий среди сообщений не так-то просто.... Предлагаю что-то с этим предпринять. Потому что если не будет простого и быстрого доступа к ответу на вопрос - новичок его задаст где-то повторно. Да ещё и с нарушением наших "негласных" правил (сначала поискать ответ самостоятельно). -

для вас есть тема: http://electronix.ru/forum/index.php?showtopic=84650 Ответ по существу: этот шрифт поменять можно, когда компонент уже будет на схеме. В библиотеке может быть другой шрифт. Шрифт на схеме определяется настройками документа: Design - Document Options - System Font (пишу по памяти). ЗЫ: не забудьте оформить этот вопрос и ответ в фак: http://electronix.ru/forum/index.php?showtopic=79105

-

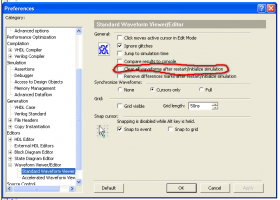

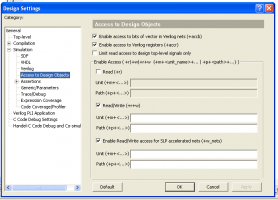

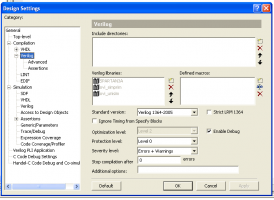

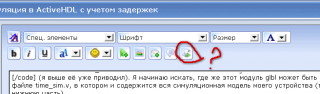

Здравствуйте. Помогите, пожалуйста. Уже 2 дня бьюсь - не запускается временная симуляция. Имеется проект: Топ-модуль wrapper `timescale 1 ns / 1 ps module wrapper ( input L_clk_in_ds_p, input L_clk_in_ds_n, input L_data_in_ds_p, input L_data_in_ds_n, output L_clk_out_ds_p, output L_clk_out_ds_n, output L_data_out_ds_p, output L_data_out_ds_n, ); wire [9:0] par_data; wire par_sync, ddr_clk_in; SerDes_LR #( .DDR_CLK_DES_GBUF(1), .PAR_CLK_DES_GBUF(1) ) serdes_uut( .par_data_ser(par_data), .ddr_clk_ser(ddr_clk_in), .par_sync_ser(par_sync), .clk_in_ds_p(L_clk_in_ds_p), .clk_in_ds_n(L_clk_in_ds_n), .data_in_ds_p(L_data_in_ds_p), .data_in_ds_n(L_data_in_ds_n), .clk_out_ds_p(L_clk_out_ds_p), .clk_out_ds_n(L_clk_out_ds_n), .data_out_ds_p(L_data_out_ds_p), .data_out_ds_n(L_data_out_ds_n), .sync_en(1'b1), .par_data_des(par_data), .par_clk_en(), .par_clk_des(par_sync), .ddr_clk_des(ddr_clk_in), .carrier_lost() ); /* synthesis translate_off */ glbl glbl (); /* synthesis translate_on */ endmodule - это обёртка другого модуля serdes_lr, который я хочу проверить: `timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date: 14:53:38 07/05/2010 // Design Name: // Module Name: SerDes_LR // Project Name: // Target Devices: // Tool versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// `ifndef SERDES_V `define SERDES_V `include "Serialiser.v" `include "Deserialiser.v" module SerDes_LR // !!! Внимание!!! в данном коде везде имеет место путаница: сигналы с суффиксом _o (odd, т.е. нечётный) // по порядку на самом деле чётные. Но отсчёт начинается с нуля. Аналогично сигналы с суффиксом _e // (even, т.е. чётный) по порядку на самом деле нечётные, но если считать с нуля, то это 0, 2, 4, ... // Кроме того, в одном блоке защёлкивание происходит по одному фронту, а в смежном блоке (смежные блоки - // это сериализатор и десериализатор) - по другому фронту (по положительному и отрицательному) #( parameter sync_frm_p = 10'b0011111010, parameter sync_frm_n = 10'b1100000101, parameter resync_period = 40, parameter PAR_CLK_DES_GBUF = 0, // разрешено ли подключить сигнал к глобальным линиям: parameter DDR_CLK_DES_GBUF = 0, // 0 - запрещено, 1 - подключить принудительно parameter DDR_IN_DATA_DELAY = "AUTO", // задержка последовательного сигнала данных на IOB parameter DDR_IN_CLK_DELAY = "0" // задержка тактового сигнала на IOB ) // !!! последние 2 параметра - строковые !!!! ( input wire [9:0] par_data_ser, input wire ddr_clk_ser, input wire par_sync_ser, input clk_in_ds_p, input clk_in_ds_n, input data_in_ds_p, input data_in_ds_n, output clk_out_ds_p, output clk_out_ds_n, output data_out_ds_p, output data_out_ds_n, input wire sync_en, output wire [9:0] par_data_des, output wire par_clk_en, output par_clk_des, output reg carrier_lost = 1, output ddr_clk_des ); // !!! Внимание!!! в данном коде везде имеет место путаница: сигналы с суффиксом _o (odd, т.е. нечётный) // по порядку на самом деле чётные. Но отсчёт начинается с нуля. Аналогично сигналы с суффиксом _e // (even, т.е. чётный) по порядку на самом деле нечётные, но если считать с нуля, то это 0, 2, 4, ... // Кроме того, в одном блоке защёлкивание происходит по одному фронту, а в смежном блоке (смежные блоки - // это сериализатор и десериализатор) - по другому фронту (по положительному и отрицательному) wire ddr_data_out_e; wire ddr_data_out_o; wire ddr_data_in_e; wire ddr_data_in_o; // ниже группа назначений для пробы прямого подключения к глобальным буферам без параметров // (в нормальном режиме должно быть закомментировано) // wire ddr_clk_des_inbuf; // wire par_clk_des_nobuf; // assign ddr_clk_des = ddr_clk_des_inbuf; // assign par_clk_des = par_clk_des_nobuf; // Ниже делаем параметризируемое подключение тактовых сигналов к глобальным линиям wire ddr_clk_des_inbuf/* synthesis syn_noclockbuf = 1 */; wire par_clk_des_nobuf/* synthesis syn_noclockbuf = 1 */; generate if (DDR_CLK_DES_GBUF != 0) begin wire ddr_clk_des_bufg; BUFG BUFG_ddr_clk_des_bufg ( .O(ddr_clk_des_bufg), // Clock buffer output .I(ddr_clk_des_inbuf) // Clock buffer input ); assign ddr_clk_des = ddr_clk_des_bufg; end else assign ddr_clk_des = ddr_clk_des_inbuf; endgenerate generate if (PAR_CLK_DES_GBUF != 0) begin wire par_clk_des_bufg; BUFG BUFG_par_clk_des_bufg ( .O(par_clk_des_bufg), // Clock buffer output .I(par_clk_des_nobuf) // Clock buffer input ); assign par_clk_des = par_clk_des_bufg; end else assign par_clk_des = par_clk_des_nobuf; endgenerate // Выше делаем параметризируемое подключение тактовых сигналов к глобальным линиям wire ddr_data_des, // последовательные данные между входным усилителем и DDR-триггером ddr_data_ser, // последовательные данные между DDR-триггером и выходным усилителем ddr_clk_ser_outbuf; // тактовый сигнал между DDR-триггером и выходным усилителем IBUFDS #( .DIFF_TERM("FALSE"), // Differential Termination (Virtex-4/5, Spartan-3E/3A) .IBUF_DELAY_VALUE(DDR_IN_CLK_DELAY), // Specify the amount of added input delay for // the buffer, "0"-"16" (Spartan-3E/3A only) .IOSTANDARD("LVDS_33") // Specify the input I/O standard ) IBUFDS_DDR_clk_des_inbuf ( .O(ddr_clk_des_inbuf), // Buffer output .I(clk_in_ds_p), // Diff_p buffer input (connect directly to top-level port) .IB(clk_in_ds_n) // Diff_n buffer input (connect directly to top-level port) ); // D input IBUFDS #( .CAPACITANCE("DONT_CARE"), // "LOW", "NORMAL", "DONT_CARE" (Virtex-4 only) .DIFF_TERM("FALSE"), // Differential Termination (Virtex-4/5, Spartan-3E/3A) .IBUF_DELAY_VALUE("0"), // Specify the amount of added input delay for // the buffer, "0"-"16" (Spartan-3E only) .IFD_DELAY_VALUE(DDR_IN_DATA_DELAY), // Specify the amount of added delay for input // register, "AUTO", "0"-"8" (Spartan-3E/3A only) .IOSTANDARD("LVDS_33") // Specify the input I/O standard ) IBUFDS_sdr_data_in ( .O(ddr_data_des), // Buffer output .I(data_in_ds_p), // Diff_p buffer input (connect directly to top-level port) .IB(data_in_ds_n) // Diff_n buffer input (connect directly to top-level port) ); // !!! Внимание!!! в данном коде везде имеет место путаница: сигналы с суффиксом _o (odd, т.е. нечётный) // по порядку на самом деле чётные. Но отсчёт начинается с нуля. Аналогично сигналы с суффиксом _e // (even, т.е. чётный) по порядку на самом деле нечётные, но если считать с нуля, то это 0, 2, 4, ... // Кроме того, в одном блоке защёлкивание происходит по одному фронту, а в смежном блоке (смежные блоки - // это сериализатор и десериализатор) - по другому фронту (по положительному и отрицательному) IDDR2 #( .DDR_ALIGNMENT("NONE"), // Sets output alignment to "NONE", "C0" or "C1" .INIT_Q0(1'b0), // Sets initial state of the Q0 output to 1'b0 or 1'b1 .INIT_Q1(1'b0), // Sets initial state of the Q1 output to 1'b0 or 1'b1 .SRTYPE("SYNC") // Specifies "SYNC" or "ASYNC" set/reset ) IDDR2_DDR_IN ( .Q0(ddr_data_in_e), // 1-bit output captured with C0 clock .Q1(ddr_data_in_o), // 1-bit output captured with C1 clock .C0(ddr_clk_des), // 1-bit clock input .C1(~ddr_clk_des), // 1-bit clock input .CE(1), // 1-bit clock enable input .D(ddr_data_des), // 1-bit DDR data input .R(0), // 1-bit reset input .S(0) // 1-bit set input )/* synthesis syn_useioff=1 */; OBUFDS #( .IOSTANDARD("LVDS_33") // Specify the output I/O standard ) OBUFDS_clk_out ( .O(clk_out_ds_p), // Diff_p output (connect directly to top-level port) .OB(clk_out_ds_n), // Diff_n output (connect directly to top-level port) .I(ddr_clk_ser_outbuf) // Buffer input ); OBUFDS #( .IOSTANDARD("LVDS_33") // Specify the output I/O standard ) OBUFDS_data_out ( .O(data_out_ds_p), // Diff_p output (connect directly to top-level port) .OB(data_out_ds_n), // Diff_n output (connect directly to top-level port) .I(ddr_data_ser) // Buffer input ); // !!! Внимание!!! в данном коде везде имеет место путаница: сигналы с суффиксом _o (odd, т.е. нечётный) // по порядку на самом деле чётные. Но отсчёт начинается с нуля. Аналогично сигналы с суффиксом _e // (even, т.е. чётный) по порядку на самом деле нечётные, но если считать с нуля, то это 0, 2, 4, ... // Кроме того, в одном блоке защёлкивание происходит по одному фронту, а в смежном блоке (смежные блоки - // это сериализатор и десериализатор) - по другому фронту (по положительному и отрицательному) ODDR2 #( .DDR_ALIGNMENT("C0"), // Sets output alignment to "NONE", "C0" or "C1" .INIT(1'b0), // Sets initial state of the Q output to 1'b0 or 1'b1 .SRTYPE("SYNC") // Specifies "SYNC" or "ASYNC" set/reset ) ODDR2_L_DDR_OUT ( .Q(ddr_data_ser), // 1-bit DDR output data .C0(ddr_clk_ser), // 1-bit clock input .C1(~ddr_clk_ser), // 1-bit clock input .CE(1'b1), // 1-bit clock enable input .D0(ddr_data_out_e), // 1-bit data input (associated with C0) .D1(ddr_data_out_o), // 1-bit data input (associated with C1) .R(1'b0), // 1-bit reset input .S(1'b0) // 1-bit set input )/* synthesis syn_useioff=1 */; ODDR2 #( .DDR_ALIGNMENT("NONE"), // Sets output alignment to "NONE", "C0" or "C1" .INIT(1'b0), // Sets initial state of the Q output to 1'b0 or 1'b1 .SRTYPE("SYNC") // Specifies "SYNC" or "ASYNC" set/reset ) ODDR2_L_DDR_OUT_clk ( .Q(ddr_clk_ser_outbuf), // 1-bit DDR output data .C0(ddr_clk_ser), // 1-bit clock input .C1(~ddr_clk_ser), // 1-bit clock input .CE(1'b1), // 1-bit clock enable input .D0(1), // 1-bit data input (associated with C0) .D1(0), // 1-bit data input (associated with C1) .R(1'b0), // 1-bit reset input .S(1'b0) // 1-bit set input )/* synthesis syn_useioff=1 */; // !!! Внимание!!! в данном коде везде имеет место путаница: сигналы с суффиксом _o (odd, т.е. нечётный) // по порядку на самом деле чётные. Но отсчёт начинается с нуля. Аналогично сигналы с суффиксом _e // (even, т.е. чётный) по порядку на самом деле нечётные, но если считать с нуля, то это 0, 2, 4, ... // Кроме того, в одном блоке защёлкивание происходит по одному фронту, а в смежном блоке (смежные блоки - // это сериализатор и десериализатор) - по другому фронту (по положительному и отрицательному) Serialiser Ser ( .par_data_in(par_data_ser), .ddr_clk(ddr_clk_ser), .par_sync(par_sync_ser), .ddr_data_out_e(ddr_data_out_e), .ddr_data_out_o(ddr_data_out_o) ); // !!! Внимание!!! в данном коде везде имеет место путаница: сигналы с суффиксом _o (odd, т.е. нечётный) // по порядку на самом деле чётные. Но отсчёт начинается с нуля. Аналогично сигналы с суффиксом _e // (even, т.е. чётный) по порядку на самом деле нечётные, но если считать с нуля, то это 0, 2, 4, ... // Кроме того, в одном блоке защёлкивание происходит по одному фронту, а в смежном блоке (смежные блоки - // это сериализатор и десериализатор) - по другому фронту (по положительному и отрицательному) Deserialiser #( .sync_frm_p(sync_frm_p), .sync_frm_n(sync_frm_n), .resync_period(resync_period) ) Des ( .ddr_data_in_e(ddr_data_in_e), .ddr_data_in_o(ddr_data_in_o), .ddr_clk_in(ddr_clk_des), .sync_en(sync_en), .par_data_out(par_data_des), .par_clk_en(par_clk_en), .par_clk(par_clk_des_nobuf), .counter_out_e(), .counter_out_o() ); //=============================== //Carrier detect // //=============================== //Dividing input frequency reg [4:0] f_in_div = 0; always @(posedge ddr_clk_des) begin f_in_div <= f_in_div + 1; end //Crossing clock domain reg [2:0] f_in_div_local; always @(posedge par_sync_ser) begin f_in_div_local[0] <= f_in_div[4]; f_in_div_local[1] <= f_in_div_local[0]; f_in_div_local[2] <= f_in_div_local[1]; end //detecting of carrier loss reg [3:0] carrier_cnt = 0; always @(posedge par_sync_ser) begin if(f_in_div_local[2] != f_in_div_local[1]) begin carrier_cnt <= 0; carrier_lost <= 0; end else begin if(carrier_cnt == 4'hF) carrier_lost <= 1; else carrier_cnt <= carrier_cnt + 1; end end endmodule `endif В модуле serdes_lr используются другие модули, которые инклюдятся (приводить их не буду из соображений хоть некоторой коммерческой тайны - чтобы руководство не обвинило в раскрытии исходников - думаю приведённых исходников достаточно для понимания проблемы). Как видно даже из приведённых исходников в коде применяются xilinx-specific примитивы. Они описаны в библиотеке OVI_Unisim. Функциональная симуляция запускается, ошибок не даёт (пробовал командой Simulation - Initialize Simulation, дальше не пробовал, т.к. для данного кода мне необходима временная симуляция. А временная уже на этапе данной команды выдаёт ошибку. Об это будет ниже). Замечательно. Делаю синтез через Synplify. Синтез проходит нормально. Делаю Implementation как вызов из Active-HDL ксайлинксовского имплементатора, входящего в комплект Xilinx ISE Studio. Результаты имплемента смотрю в FPGA Editor'е - все примитивы расставлены, как мне надо. Т.е. проект не липовый. Перехожу непосредственно к временной симуляции согласно этому сообщению. Настраиваю параметры симуляции в окошке Timing Simulation Options. Оно у меня выглядит так: Нажимаю в Design Flow кнопочку Timing Simulation. Вылазит следующая ошибка (привожу полный лог сообщений Active-HDL после нажатия этой кнопочки): # ELBREAD: Elaboration process. # ELBREAD: Elaboration time 0.0 [s]. # Checking if synthesis needs to be updated... # Checking if implementation needs to be updated... vlcomp -l ovi_simprim -l SPARTAN3A -l ovi_unisim -work serdes_lr_timing "$dsn\IMPLEMENT\TIME_SIM.V" # Compile... # Pass 1. Scanning modules hierarchy. # Module \$root found in current working library. # Module X_IPAD found in library ovi_simprim. # Module X_BUFGMUX found in library ovi_simprim. # Module X_ZERO found in library ovi_simprim. # Module X_AND2 found in library ovi_simprim. # Module X_SFF found in library ovi_simprim. # Module X_XOR2 found in library ovi_simprim. # Module X_INV found in library ovi_simprim. # Module X_IBUFDS found in library ovi_simprim. # Module X_OBUFDS found in library ovi_simprim. # Module X_ONE found in library ovi_simprim. # Module X_FF found in library ovi_simprim. # Module X_MUX2 found in library ovi_simprim. # Module X_FDDRRSE found in library ovi_simprim. # Module X_OPAD found in library ovi_simprim. # Module X_BUF found in library ovi_simprim. # Module X_LUT4 found in library ovi_simprim. # Pass 2. Processing instantiations. # Pass 3. Processing behavioral statements. # ELB/DAG code generating. # Module \$root found in current working library. # Unit top modules: wrapper glbl. # $root top modules: wrapper glbl. # Compile success 0 Errors 0 Warnings Analysis time: 0[s]. # done asim +access +r -advdataflow -L ovi_simprim -PL ovi_simprim -sdftyp -AUTO="$dsn\implement\time_sim.sdf" wrapper # ELBREAD: Elaboration process. # ELBREAD: Elaboration time 0.0 [s]. # asim: Stack memory: 32MB # asim: Retval memory: 32MB # KERNEL: Main thread initiated. # KERNEL: Kernel process initialization phase. # KERNEL: Time resolution set to 1ps. # ELAB2: Elaboration final pass... # ELAB2: Create instances ... # ELAB2: Fatal Error: ELAB2_0036 Unresolved hierarchical reference to "glbl.GTS" from module "wrapper.\serdes_uut/OBUFDS_clk_out/OBUFDS \" (module not found). # ELAB2: Last instance before error: .\serdes_uut/OBUFDS_clk_out/OBUFDS \ # KERNEL: Error: E8005 : Kernel process initialization failed. # Error: Fatal error occurred during simulation initialization. wave wave /wrapper/* .wrapper.* Смысл ошибки какой? Что она не видит сигнал GTS, объявленный в модуле glbl. А на этот сигнал ссылается примитив wrapper.\serdes_uut/OBUFDS_clk_out/OBUFDS. Открываю исходник, на основе которого было выдано такое сообщение (это сам v-файл для временной симуляции - time_sim.v - см. в прилагаемом архиве весь файл: sources.rar) Делаю поиск по этому файлику строки serdes_uut/OBUFDS_clk_out/OBUFDS. Нахожу вот что: X_OBUFDS #( .LOC ( "PAD60" )) \serdes_uut/OBUFDS_clk_out/OBUFDS ( .I(\serdes_uut/ddr_clk_ser_outbuf ), .O(L_clk_out_ds_p), .OB(L_clk_out_ds_n) ); Т.е. создаётся экземпляр примитива типа X_OBUFDS, который находится в библиотеке OVI_Simprim: `timescale 1 ps/1 ps module X_OBUFDS (O, OB, I); parameter LOC = " UNPLACED"; parameter CAPACITANCE = "DONT_CARE"; parameter IOSTANDARD = "DEFAULT"; output O, OB; input I; [b] tri0 GTS = [u]glbl.GTS[/u]; [/b] bufif0 (O, I, GTS); notif0 (OB, I, GTS); specify (I => O) = (0:0:0, 0:0:0); (I => OB) = (0:0:0, 0:0:0); specparam PATHPULSE$ = 0; endspecify endmodule Здесь-то мы и обнаруживаем ту самую ссылку, которую не находит программа при попытке запуска симуляции и о которой она выдаёт ошибку # ELAB2: Fatal Error: ELAB2_0036 Unresolved hierarchical reference to "glbl.GTS" from module "wrapper.\serdes_uut/OBUFDS_clk_out/OBUFDS \" (module not found) (я выше её уже приводил). Я начинаю искать, где же этот модуль glbl может быть указан... и обнаруживаю, что этот модуль указан в том же самом файле time_sim.v, в котором и содержится вся симуляционная модель моего устройства (т.е. модуль wrapper) (исходник выше я приводил, см. самую нижнюю часть). Я ничего не понимаю: получается, что модуль wrapper в файле time_sim.v видится, потому что ошибка ссылается на \serdes_uut/OBUFDS_clk_out/OBUFDS. А этот экземпляр описывается именно в time_sim.v. Т.е. модуль wrapper в файле time_sim.v программа видит, а модуль glbl она не видит. Хотя этот модуль находится в том же файле, только ниже... Ну как такое может быть???... Ничего не понимаю... Пробовал описание модуля glbl переставить в начало, чтобы его первым проходило при анализе - ничего не поменялось... Дополнительно привожу настройки в меню Design - Settings: Помогите, пожалуйста... работа стоит... Больше всего я не понимаю, почему не видится glbl, если он в том же файле, другой модуль из которого видится? Может ссылка glbl.GTS не годится, а надо записать эту ссылку в другой форме, чтобы увиделось? Или где-то какую-то галочку поставить? Или куда-то какую-то библиотеку дописать?... Прилагаю архив с исходниками: sources.rar. 4 Vetal: сори, не догадывался, что есть различия в code и codebox, думал code, как раз, и сделает с прокруткой. А codebox'а вообще нет в панельке инструментов: А сам я в html-е не силён :)

-

Симуляция в Active-HDL

Krys ответил VitalyM4 тема в Среды разработки - обсуждаем САПРы

Ещё одно добавление по Xilinx: Если в проекте используются Xilinx-specific примитивы (типа IBUFDS и т.п.), то чтобы всё компилилось под функциональную симуляцию достаточно в меню Design - Settings выбрать в дереве Compilation - Verilog и там в окошке Verilog Libraries указать OVI_Unisim (она уже будет присутствовать в списке выбора после установки библиотек Xilinx Verilog Libraries с сайта Альдека). Затем эту же библиотеку необходимо указать в том же самом меню в дереве Simulation - Verilog в том же окошке Verilog Libraries (там будет 2 одинаковых окошка слева и справа, можно в обоих). Если необходима временная симуляция, то вместо OVI_Unisim ссылаемся на OVI_Simprim в обоих местах (в дереве Simulation и Compilation). Насчёт "обоих" я неуверен. Но в дереве Simulation - точно. Про временную симуляцию есть информация здесь. Далее если мы используем при функциональной симуляции корки ксилинксовские, то нам нужно поставить наряду с OVI_Unisim библиотеку OVI_Xilinxcorelib (она также уже будет в списке выбора). Уточнение по поводу записи glbl glbl(); Её нужно применять, если используются примитивы, описанные в OVI_Unisim. В этих примитивах используется сигнал GSR (глобальный сигнал сброса кристалла), а модуль glbl его имитирует при симуляции. При синтезе "прошивки", т.е. при операции Synthesis или Implementation этот модуль не требуется, поэтому, допустим, для Synplify необходимо указать: /* synthesis translate_off */ glbl glbl (); /* synthesis translate_on */ -

Всё, с параметрами вопрос решил. Вставляется через меню Diagram - Verilog - Parameter С дефайнами вопрос решён не до конца. Дефайны можно прописать в Diagram - Verilog - Design Unit Header. Правда `endif в конце файла этой штукой поставить не удастся. Появился вопрос: что такое Declaration For Module в меню Diagram - Verilog? Пробовал там писать всякие всячности и генерировать код - нигде в коде не появляется то, что я там написал. Что в этом блоке можно описать?

-

Здравствуйте. Кто работал с Aldec Active-HDL, он в графике умеет делать параметризируемые модули и всякие дефайны? Пока нашёл только локальные параметры, а передаваемые извне - нет... Т.е. мне надо такое чтобы получилось после компиляции схемы в верилог: `ifndef SERDES_V `define SERDES_V `include "Serialiser.v" `include "Deserialiser.v" module SerDes_LR #( parameter sync_frm_p = 10'b0011111010, parameter sync_frm_n = 10'b1100000101, parameter resync_period = 40, ) ( input wire [9:0] par_data_ser, ... Я когда кусок кода в графику вставляю как кодовый блок, то он мои параметры естественно все запихивает внутрь модуля типа такого: module SerDes_LR ( input wire [9:0] par_data_ser, ... ) parameter sync_frm_p = 10'b0011111010; parameter sync_frm_n = 10'b1100000101; parameter resync_period = 40; ... А всякие инклюды вообще никак вне модуля... А хотелось бы...

-

Altium для новых начинающих

Krys ответил Uladzimir тема в Altium Designer, DXP, Protel

Вот тут задаётся по Вашему желанию: Но похоже непосредственно выравнивания нет. Есть только смещение на указанную величину. -

Нельзя забывать. А какие тут выходы? Что нужно реально сделать?