-

Постов

2 052 -

Зарегистрирован

-

Посещение

Весь контент Krys

-

Свою приводить не буду, представлял именно так, что реализовано одним из показанных способов. Просто подозревал, что правый вариант реализует мультиплексор на отдельном внешнем LUT, а левый вариант - это и есть ENA "в лоб". Вот тут я не понимаю, откуда гонки. Признаюсь, "плаваю" в теоретических вопросах конечных автоматов, и про многофазную синхронизацию не понимаю. Если нетрудно, можно примерчик (я так понял, Вам всё равно в академических целях примерчики потребуются). Думаю, при применении идеологии синхронного дизайна термин "гонки" должен отсутствовать как класс, поэтому я про него и думать уже давно забыл. Ну раскрыла бы она на уровне транзисторов, а что это изменит? Главное, что инструмент гарантирует выполнение временных ограничений. А как он этого добивается - его дело ))

-

А откуда следует такое убеждение?

-

Вот тут будет точно звучать иронично, что учиться никогда не поздно, даже после вуза и 7 лет разработчиком ))) Вы про рассыпушные говорите? Можно для примера? В ПЛИС то триггеры и сейчас без коммутатора на входе. Коммутатор отдельно на LUT. Ничего не понял, ну да ладно )) А где про это почитать можно? А оно надо, синхроимпульс этот? В тех современных "каверах" на тему асинхронной логики, которые я подразумевал выше, предельное быстродействие при отсутствии ложных срабатываний достигается, как я писал, за счёт введения обратной связи по сигналу типа "импульс принят". А если вводить синхроимпульс, то он будет гробить все достижения предельного быстродействия, полученные таким вот образом.

-

Хм... никогда не задумывался об этой тонкости. А где про это почитать (что бороться не может)? Чисто абстрактные логические рассуждения, не привязанные к SRL: если SRL - это память, а ведь память же это триггеры, а триггеры борются с метастабильностью. Почему SRL не борется?

-

Человек сам обучать будет, а Вы ему говорите ещё учиться и учиться ))) Дак если бы эта асинхронная технология завоевала сердца - то и пользовались бы ей не капли в море. Как так получилось? Плис с асинхронной начинкой, но предназначена для синхронных дизайнов.

-

На идеях того, что тактовый сигнал по тактовой цепи всегда дойдёт быстрее любого не тактового сигнала, т.е. для этого по кристаллу проброшена соответствующая быстродействующая сеть. Далее... все задержки по кристаллу заранее известны программе-разводчику, и она всегда знает, какие у неё задержки распространения конкретного сигнала от выхода одного триггера до входа другого. Ну почему же... это всё очень тесно взаимосвязано. Логика без схемотехники никуда. А схемотехника в принципе одна и та же, что в ПЛИС, что на рассыпухе, что в ASIC. Вот мне стало интересно: Вы теоретик или практик? "Прошивки" для БМК разрабатывали? Спрашиваю не с целью помериться пиписьками. Просто чувствуется у Вас фундаментальный, энциклопедический подход. Честно признаюсь: мало знаком с кухней подготовки ASIC, поэтому вопрос: неужели и вправду делают сейчас такие вот асики на основе асинхронного дизайна? А как же его верифицировать? Есть для этого инструменты? Я конечно когда-то давно слышал статьи, что вот новая технология асинхронного дизайна - хорошо забытое старое - что мол позволяет выжать всё возможное из логики, работает однозначно быстрее синхронного дизайна. Особенность в этом забытом старом было в том, что для достижения предельного быстродействия и отсутствия сбоев нужно было вводить обратные связи типа "сигнал принят". Но уже много лет прошло, а что-то я так и не заметил адаптации структуры ПЛИС под асинхронные дизайны.

-

А в асиках не так как в плисах? Насколько я знаю, логика для асиков сначала отлаживается на плис, следовательно, применяются все те же методологии, в т.ч. и синхронного дизайна. Выгоднее, но в доках от производителей плис рекомендуется всё же обходиться без gated clock. А там где это действительно требуется - существует специальный элемент типа BUFGCE, который обеспечивает примерно то же, что на Вашей картинке. Тем более речь идёт об одном триггере, о его схеме с CE. Я так думаю, если не упоминал - то это хуже. Скорее всего, для него это открытие )) Зато я упоминал, что асинхронщина устарела. А не устарел - синхронный дизайн.

-

у нас на предприятии все проекты делаются в планахеде, никаких подобных глюков не было.

-

и в ПЛИС тоже? Это всё устарело )) безопасный он до тех пор, пока задержки не начинают быть сравнимы с периодом сигналов. По какому параметру совсем другое? Понятно, что буквы названия другие. А по потреблению ресурсов - примерно та же байда )) Дак по идеологии синхронного дизайна не надо так делать (в момент фронта). Либо ставьте на сигнал управления мультиплексором такой же синхронизатор, как на Вашей картинке.

-

Либо по формуле с 3 вещественными умножениями и 5 сложениями из датащита на DSP48

-

Поздно увидел сообщение. В ПЛИС по первой схеме вообще не принято делать триггеры, т.е. должна быть идеология синхронного дизайна. На это даже синтезатор должен ругнуться и сказать, что это gated clock или ripple clock. Т.е. тактовая должна подаваться всегда прямо на тактовый вход, безо всяких комбинационных схем. Аналогичную идеологию синхронного дизайна можно применять и для цифровых микросхем

-

да он ничего не значит, просто его надо ставить, если нужно вытянуть максимальную тактовую. В датащите на дсп-блок про это есть.

-

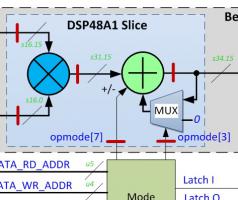

Хочу похвастаться своими успехами. Вот такую схему: реализовал вот таким кодом: (* use_dsp48 = "yes" *) reg addsub_pp, muxzero_pp; (* use_dsp48 = "yes" *) reg [DIN_BW-1 : 0] din_pp, cin_pp, din_pp2, cin_pp2; (* use_dsp48 = "yes" *) reg [DIN_BW*2 - 1 : 0] mult; (* use_dsp48 = "yes" *) reg [ACC_BW - 1 : 0] acc; (* use_dsp48 = "yes" *) wire [ACC_BW - 1 : 0] dsp48_z; // z input of post-adder // dsp48 slice logic always @(posedge clk) begin addsub_pp <= addsub; muxzero_pp <= muxzero; din_pp <= din; cin_pp <= cin; din_pp2 <= din_pp; cin_pp2 <= cin_pp; mult <= din_pp2 * cin_pp2; if(addsub_pp == 0) begin acc <= dsp48_z + mult; end else begin acc <= dsp48_z - mult; end end assign dsp48_z = muxzero_pp ? acc : 0; Т.е. это простой перемножитель комплексных чисел с накоплением суммы нескольких произведений (взятие линейной комбинации входных сигналов с применением некоторых весовых коэффициентов), реализованный в последовательной форме, когда одна операция делается за несколько тактов. Здесь необходимо переключать сложение-вычитание, а также в некоторые моменты времени начинать накопление с начала, для чего подавать 0 вместо обратной связи. Радуюсь, что удалось обойтись вот такой малой кровью, а то поначалу светила перспектива описывать DSP48 как макроблок (неприятная рутина). ЗЫ: это всё скушал XST под Spartan-6.

-

Точнее так для общего случая: +ceil(log2(N_add)) бит. Т.е. если заранее известно, что будут складываться 4 числа, то разрядность надо увеличить не на 4 бита, а всего на 2.

-

aldec active hdl ещё умеет схемы по коду рисовать. Правда такая фигня получается ))) (бородатый анекдот: я умею печатать слепым набором со скоростью 1000 знаков в минуту! ... правда такая фигня получается...)

-

спасибо, бегу патентовать! ))))

-

Я про вот это в смысле:

-

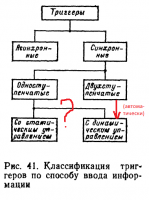

А из какой книжки это взято? И как это работает? Можете плиз на пальцах объяснить?

-

Ну дифцепь на резисторе и конденсаторе грубо говоря ))) В книжке Триггеры об этом говорится ))) Типа способ был не распространён в виду сложности реализации емкостей в микросхемах (того времени ))) ) А цифровой - как в современных двухступенчатых триггерах. Есть и другие способы выделения фронта на цифровых элементах, в частности, реализуемые на ПЛИС, но к синхронной логике это не относится (так делали в первобытность ПЛИС, когда о синхронном дизайне мало кто догадывался).

-

А Вы об истории в той книжке Триггеры прочитали? Мне кажется, с динамическим управлением придумали раньше (не уверен). Но фронт выделяли аналоговым способом.

-

Правильно - что учили по книжке. Неправильно - что книжка содержит неправильную картинку. Итого: учили неправильно ))) Правильная картинка должна быть такая: Автор книжки в виду её (и своей) архаичности поперемешал в одну кучу аналоговые и цифровые способы получения динамического входа. В итоге связь, указанная на моей картинке вопросом - она справедлива лишь для аналогового способа выделения фронта. Итого - это всё неактуально для современных ПЛИС. С другой стороны, автор книжки забыл провести связь, указанную на моей картинке стрелкой. Эта связь образуется автоматически, т.е. любой двухступенчатый триггер по умолчанию динамический (нет, ну можно, если очень надо, умудриться сделать нединамический двухступенчатый триггер, но это неконструктивно, как велосипед с квадратными колёсами).

-

Спасибо за тайное знание! Вот уж точно хакерство ))) Т.е. это придётся делать ручками для каждой цепи?...

-

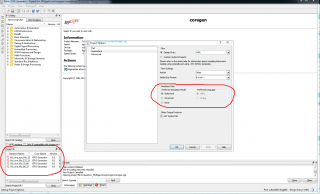

ActiveHDL+ISE (IP core)

Krys ответил hendehoh тема в Среды разработки - обсуждаем САПРы

Вот смотрите: в ISE заходите в меню tools - core generator. В нём заходите в меню file - open project, указываете путь к файлу *.cgp (обычно coregen.cgp) в общей папке ваших корок. Когда откроете - увидите внизу в окошке весь список сгенерённых Вами корок. Далее заходите в меню Project - Project Options и там видите следующее: Делаете нужные настройки симуляционных файлов. Затем заходите в Project - Regenerate all project IP (можно и по одной перегенерить). Но вполне возможно эти настройки уже и так правильно стояли, поэтому симуляционные файлы и так были сгенерены. И искать их нужно в папке с коркой. Открывайте в этой папке все подряд файлы с расширениями *.vhd и смотрите - то, не то. -

Ну видимо неправильно учили )) Динамическое управление невозможно сделать без двух ступеней. Либо, как написано в той же книжке выше, на аналоговых дифференциальных цепях. Двухступенчатый - это не обязательно 2 строго одинаковых последовательно соединённых триггера. Это просто 2 триггера последовательно, неважно одинаковых или немного разных. В конце концов все "разные" триггеры сделаны из RS путём навешивания на его входы и выходы всякой логической обвязки )))

-

Вычисление фазы

Krys ответил Alexey_pashinov тема в Алгоритмы ЦОС (DSP)

Вот тут например: http://www.dsplib.ru/content/complex/complex.html Частное от деления комплексных чисел имеет амплитуду, равную отношению модулей, и фазу, равную разности фаз, от этого и плясать.