Поиск

Показаны результаты для тегов 'pci-e'.

-

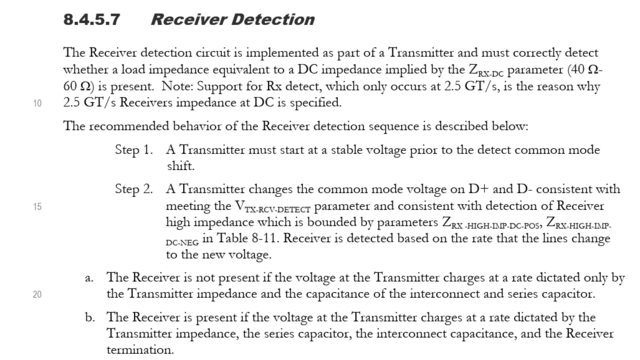

Доброго всем дня, Столкнулся с ещё одной проблемой наличия линка на PCI-E у плат с Артиксами, причём в этот раз LTSSM не может пройти дальше практически самой начальной фазы - Detect.Active, т.е. не отрабатывает процедура Receiver Detection. В описании GTP есть следующий пункт: Судя по нему в начале процедуры определения наличия приёмника ПЛИС должна установить уровень сигнала на линиях TXN и TXP равным (Vdd - Vswing/2). Отдельный вопрос, какое именно значение Vswing они считают правильным, но я предполагаю что 500 мВ. Vdd судя по всему это Vmgtavtt, т.е. 1,2 В. Т.е. в итоге на выходах ПЛИС должно появиться значение напряжения около 0,95 В. Далее, судя по описанию, происходит отключение управляющей цепи и уровень сигнала должен вернуться к Vcmoutac (1,2 В / 2 = 0,6 В) и ПЛИС через заданный интервал должна измерить величину напряжения на линиях TXP/TXN, по которому принимается решение о наличии на линии приёмника. Это полностью согласуется с логикой описания этого процесса в спецификации PCI-E: Однако по факту я наблюдаю совсем другую картину: 1. перед началом процедуры определения приёмника напряжение на выходах 560 мВ; 2. при включении режима определения приёмника на выходе ПЛИС появляется уровень 1,18 В с крутым фронтом (если приёмника нет или он не готов), если приёмник есть и с ним всё хорошо, то уровень около 960 мВ. 3. далее передатчик ПЛИС формирует крутой спад сигнала и уровни возвращаются к исходным 560 мВ; Т.е. не видно никакого длительного процесса заряда-разряда конденсатора, по которому бы ПЛИС с помощью компаратора (сравнивающего уровень сигнала в линии с опорным значением) могла судить о наличии приёмника на другом конце. Напротив, всё выглядит так, что ПЛИС формирует достаточно мощный импульс и в зависимости от получившегося практически стабильного по времени уровня напряжения принимает решение о наличии/отсутствии приёмника. Проблема в том, что на некоторых слотах x16 (подключённых напрямую к процессору) процессор далеко не сразу правильно настраивает свои приёмники (подключает терминаторы) или они не сразу включаются и в результате ПЛИС не может определить их наличие, а значит пойти дальше по графу состояний LTSSM. При этом особенно интересно, что в то же самое время, пока ПЛИС не может определить наличие приёмника на другом конце, процессор успешно видит приёмник в ПЛИС и начинает слать TS1/TS2, пытаясь поднимать линк. Однако через некоторый таймаут всё это прекращается, т.к. он по всей видимости не дожидается получения TS1/TS2 от ПЛИС, что логично, т.к. ПЛИС не видит приёмника. Т.е. по факту процессор сам себе обрубает линк с платой. При этом после тёплого ресета линк стабильно поднимается (процессор прогрелся и у него стало всё хорошо? 😉). Такое поведение наблюдается на паре материнских плат и число чудящих Artix`ов всего два. При этом такая проблема далеко не нова - https://support.xilinx.com/s/article/51135?language=en_US Правда в моём случае процессор не третьего, а четвёртого поколения, для которого такой эрраты в доступной документации нет и значение TX_RXDETECT_REF уже равно рекомендованному 3'b011. На проблемных платах помогает уменьшение TX_RXDETECT_REF до значения 3'b010, при этом на рабочих платах увеличение значения TX_RXDETECT_REF до 3'b100 ломает установку линка. Однако логика работы параметра TX_RXDETECT_REF непонятна, т.к. в первую очередь кажется, что этот параметр определяет пороговое значение опорного уровня сигнала внутренного компаратора, при котором приёмник считается подключенным к линии. Однако если установить значение 3'b000, то я вижу, что максимальный уровень выходного сигнала ПЛИС в процессе проверки наличия приёмника снижается до 1,03 В вместо исходных 1,18 В. При этом Detect.Active пролетает с первого раза. Если всё так хорошо, то почему AMD (Xilinx) рекомендует ставить 3'b010 в крайнем случае и то после консультации с их техподдержкой? Есть-ли у кого-нибудь понимание, как на самом деле работает механизм определения наличия приёмника у Xilinx в седьмой серии? В шестой серии, судя по осциллограммам, механизм реализован плюс-минус также. Чем на практике чревата установка низких значений TX_RXDETECT_REF? PS: предложения вида "забить и забыть" принимаются, но игнорируются, т.к. в серии возможны массовые отказы и/или проблемы в совместимости. Поэтому ищется решение, которое бы гарантировало работоспособность плат на Артиксах в максимально широком спектре материнских плат и платформ.

-

Всем доброго времени суток, Возникла проблема с работой платы с XC7A25T-1CSG325 на материнских платах с интеловскими чипсетами 3хх и 4хх серий в слоте x16 (подключен напрямую к процессору) после ресета по кнопке. Т.е. сразу после включения питания плата определяется, линк есть, регистры платы пишутся и читаются без каких-либо ошибок и сбоев, но сразу после ресета системы по кнопке Reset или после перезагрузки системы через меню операционной системы линк пропадает и плата больше не определяется до следующего выключения/включения. При этом на той же материнской плате эта плата прекрасно работает в других слотах. Ещё более интересно, что такое странное поведение наблюдается только на одной из пяти одинаковых по схемотехнике и топологии плат, взятых из одной партии. Остальные четыре платы запускаются/работают и после ресета. При этом сбоящая плата чудит только в материнских платах фирмы MSI, в аналогичных платах на 3хх и 4хх чипсетах других производителей (например, Asus) она работает. Инструкция Xilinx по отладке проблем с PCI-E изучена от корки до корки, но никаких результатов это не принесло. С физикой проблем нет, т.к. на других мат.платах сбоящая плата работает даже через удлинитель, сделанный из кабеля USB 3.0 длиной около полуметра. Пробовал ресетить плату в проблемном слоте вручную, замыкая PERST# на землю и сразу после ресета линк пропадает и далее успешно восстанавливается. Однако если в процессе или после "ручного" ресета отресетить систему, то линк пропадает окончательно и бесповоротно. Дальнейшие ручные ресеты уже ничего не дают. Ядро сконфигурировано в режиме Gen1 (2.5 GT/s). В BIOS для слота x16 выбран режим Gen1. Это не помогает. Что ещё стоит попробовать, куда еще можно посмотреть (какие сигналы ядра)?

- 50 ответов

-

- pci-e

- link training

- (и ещё 4 )

-

Тополог г. Москва (high-speed PCB)

Kaola опубликовал тема в Предлагаю работу

Компания Бифорком Тек находится в поисках Инженера-тополога. Мы разрабатываем и производим телекоммуникационное оборудование, находимся в Особой экономической зоне «Технополис «Москва» рядом с метро Текстильщики. Если вас заинтересовала вакансия, пишите или звоните по номеру 89152033710 (Екатерина). Telegram: https://t.me/terina_ekat Также можно откликнуться на вакансию в hh.ru. Обязанности: Разработка ПП в Altium Designer. Формировать и оптимизировать стек МПП (стоимость — производительность) Трассировка сложных многослойных печатных плат; подготовка GERBER (CAM) файлов для производства печатной платы; Подготовка файлов для расстановщиков (placement) и сборочных чертежей (Assembly); Взаимодействие с разработчиками и конструкторами; Участие в разработке конструкторской документации. Будет плюсом: Моделирование целостности сигналов (SI); Моделирование распределения емкостей и полигонов питания (Power); Тепловое моделирование платы; Знание цифровой, аналоговой, СВЧ схемотехники Разработка топологии сложных печатных плат, желательно с использованием «глухих» и «слепых» переходных отверстий; Требования: Высшее техническое образование образование Работа в команде. Аккуратность; Нацеленность на результат, исполнительность и желание развиваться. Опыт проектирования многослойных печатных плат для цифровых высокоскоростных устройств; Английский достаточный для чтения технической документации; Опыт работы в радиоэлектронной промышленности; Опыт трассировки печатных плат с цифровыми интерфейсами типа PCIe Gen3, DDR3/4; Понимание проблем перекрестных помех, целостности сигнала, электромагнитной совместимости; Опыт проектирования печатных плат с высокой плотностью компоновки, в том числе с применением BGA-компонентов с мелким шагом выводов; Опыт: Трассировка с выравниванием длины линий, расчетом импеданса, моделированием целостности сигнала, использованием теплоотводящих слоев; приветствуется опыт работы с аппаратными платформами на процессорах архитектур ARM, MIPS и с высокоскоростными интерфейсами Ethernet (до 10GB, SFP), DDR3 и выше, PCIe, SATA, HDMI. Разработка посадочных мест в соответствии с IPC с учетом требований автоматической сборки ПП; Подготовка выходных файлов для производства. Согласование стеков, материалов, выбор технологии используемых в печатных платах. Условия: График 5/2; ЗП определяется по итогу собеседования; Официальное трудоустройство (белая заработная плата, оплачиваемые отпуска, больничные); После прохождения испытательного срока ДМС; 5 минут от м. Текстильщики-

- топология

- маршрутизатор

- (и ещё 16 )

-

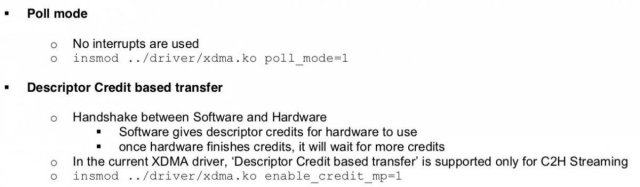

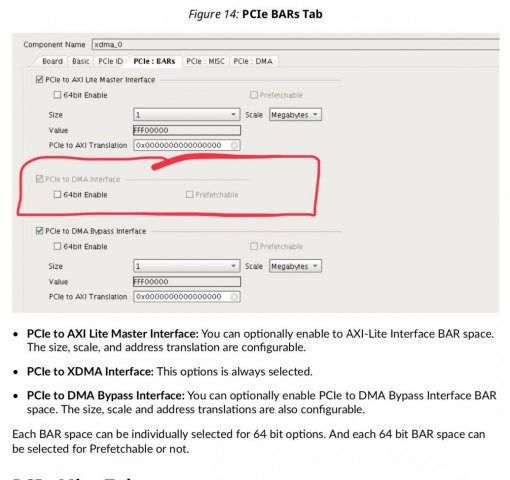

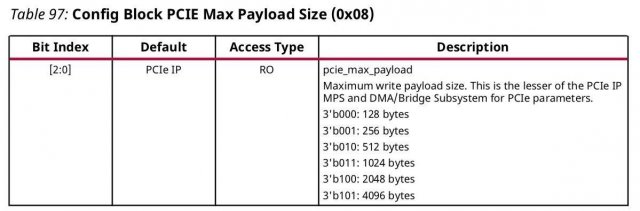

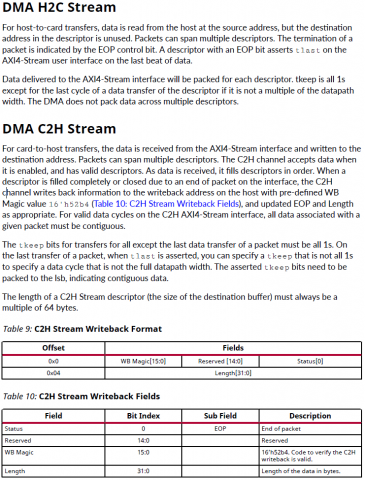

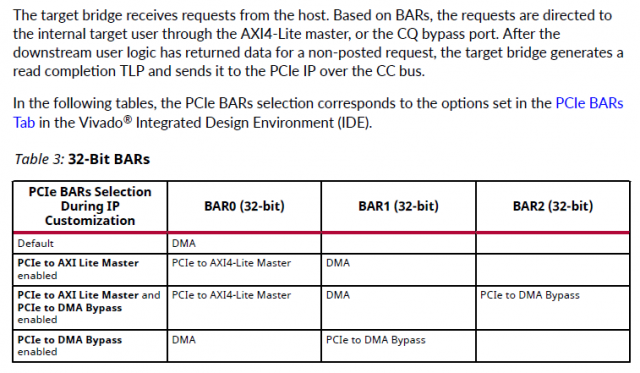

Собственно задача - с минимальными потерями времени и усилий работать с хоста через PCI-E с ускорителем в ПЛИС. Насколько я понял самый простой способ - использование ядра XDMA (обёртка над ядром PCI-E) [1], готовых драйверов xdma.ko [2] и шаблонов приложений которые идут в комплекте [3] Но после вдумчивого изучения pg195 и запуска на плате тестового примера остались вопросы, хотя они скорее системного плана, но связаны именно со спецификой ядра XDMA. Что надо от ускорителя (для определенности - пусть будет крипто-ускоритель): 1) "стримить" с хоста данные на обработку, притом чтобы ускоритель мог сообщать, что достаточно, пока больше не надо присылать данные (т.е. некий flow control на отправку) 2) уведомлять хост о том, что данные обработаны и можно забирать, и соответственно отдавать "стрим" в хост. Почему стрим в кавычках: по сути это не непрерывный стрим, а блоки по 4К (притом с заголовками, чтобы на приёмной стороне (хосте) можно было сматчить контекст - какому выходному блоку какой входной соответствовал), но по природе обработки ускоритель это как PIPE: с одной стороны вышло, с другой вышло и есть некая "глубина" внутри - чтобы начал выдавать первые данные надо несколько десятков блоков в него "застримить". Т.о. в терминах xdma для этой задачи AXI Stream подходит очень хорошо, но вот на тестовом проекте заметил нестабильную работу AXI Stream (пропадание данных) в связи с чем рассматриваю и AXI MM как альтерантиву. Но что бы написать "правильное" и надёжно работающее хостовое приложение хотелось бы понимать несколько вещей (далее список вопросов): ##### BAR ##### pg195, таблица 3, соответствующа вкладка в конфигураторе XDMA * DMA - это собственно работа с самим движком * Bypass DMA - думал что это прямой доступ к пространству памяти карточки в обход движка ДМА, но похоже это не так, это ЕЩЕ ОДНО выделенное адресное пространство (доп.канал) никак не связанное ни с движком ДМА ни с памятью в которую пишет движок ДМА. * AXI Lite Master - видимо от Bypass DMA отличается только тем, что это Lite 1.1 Смущает то, что для BAR DMA в режиме AXI MM в конфиге вивадо никак не задаётся размер BAR - это как?.. где/чем определяется размеры адресного пространства с которым работает карточка? 1.2 Далее в разделе про прерывания вскользь упомянуто, что BAR может быть _address space_ а может быть и _register space_. Надо ли держать это в уме или при использовании готового драйвера просто работать с /dev/xdma0_xxx и не париться? 1.3 Какие реальные кейсы могут быть для использования Bypass DMA ? ##### IRQ & user app ##### У самого IP-ядра есть внешние ножки прерывания, но как их использовать pg195 ответа не даёт, ограничиваясь тестовым примером проекта, в котором прерывания взводятся записью из хостовой программы в регистр в пространстве AXI Lite Master. Но как это обработать из хостовой программы совершенно неясно: 2.2 Вот мы открыли /dev/xdma0_h2c и льём туда данные, как считать прерывание "BUSY", что дескать лить хорош уже (и дальше ждать прерывания "FREE") - как это на стороне пользователя обрабатывать? 2.2 При приёме мы открываем /dev/xdma0_c2h и ждём прерывания "READY" указывающее на готовность данных в /dev/xdma0_c2h - как это на стороне пользователя обрабатывать? 2.3 Чем "правильнее" пользоваться на стороне карточки - ножками usr_irq_req и usr_irq_ack, или же механизмом MSI (msi_enable, msi_vector_width)? 2.4 В AR654444 еще описан способ загрузки драйвера в режиме поллинга (работает только в направлении c2h) - стоит ли использовать его вместо прерывания для упощения логики приложения? ##### AXI ST ##### Самое интересное: управление потоками, нарезка на "пакеты" DMA H2C Stream -------------- For host-to-card transfers, data is read from the host at the source address, but the destination address in the descriptor is unused. Packets can span multiple descriptors. The termination of a packet is indicated by the EOP control bit. A descriptor with an EOP bit asserts tlast on the AXI4-Stream user interface on the last beat of data. - т.е. на стороне хоста за формирование для AXI4-Stream сигнала tlast, который фактически нарезает пакеты как мне надо, отвечает отвечает механизм, выставляющий бит EOP (в TLP???) 3.1 достаточно ли для user app указать size=4K, для формирования EOP в xdma.ko? 3.2 см. пп.1.1 если мы не задали размер BAR для DMA, то кто будет заботиться о буферах в движке DMA на карточке и в пользовательском РТЛ коде? Буферы в движке DMA на карточке вообще черный ящик: вот отправим мы пакет с size=1М - куда его сохраняет движок DMA? - не налету же он его в пользовательскую логику передаёт??? 3.3 по размерам нашёл такое упоминание в PG195, эти значения как-то завязаны на размер внутренних буферов движка ДМА??: DMA C2H Stream -------------- For card-to-host transfers, the data is received from the AXI4-Stream interface and written to the destination address. Packets can span multiple descriptors. The C2H channel accepts data when it is enabled, and has valid descriptors. As data is received, it fills descriptors in order. When a descriptor is filled completely or closed due to an end of packet on the interface, the C2H channel writes back information to the writeback address on the host with pre-defined WB Magic value 16'h52b4 (Table 10: C2H Stream Writeback Fields), and updated EOP and Length as appropriate. - тут вроде бы тоже всё прозрачно - нарезаем пакаты для отправки сигналом tlast в AXI4-Stream, который по идее должен устанавливать в дескрипторе поле EOP 3.4 Удаляет ли при приёме дескриптор с WB Magic драйвер xdma.ko или же его должно удалять пользовательское приложение? 3.5 не очень понятна строка "For valid data cycles on the C2H AXI4-Stream interface, all data associated with a given packet must be contiguous" - означает ли это, что до взведения tlast надо держать tvalid и лить данные без пропуска клоков (иначе движок ДМА "отрежет" и отправит пакет на хост по таймауту)? ##### AXI MM ##### 4.1 опять см. пп.1.1 - как задаётся размер пространства для AXI MM? В интерфейсе конфигурирования нет такой настройки. ##### источники ##### [1] https://www.xilinx.com/support/documentation/ip_documentation/xdma/v4_1/pg195-pcie-dma.pdf [2] https://github.com/Xilinx/dma_ip_drivers [3] https://github.com/Xilinx/dma_ip_drivers/tree/master/XDMA/linux-kernel/tools

- 47 ответов

-

- pcie

- pciexpress

- (и ещё 8 )

-

Компания Бифорком Тек находится в поисках тополога в свою команду RnD. Пару слов о нас. Мы существуем с 2015 года, занимаемся разработкой и производством продуктовой линейки высокотехнологичных устройств с использованием технологий SDN/IoT/4G/5G/6LoWPAN и решений в области передачи данных. Находимся в в Особой экономической зоне «Технополис «Москва» рядом с метро Текстильщики. Ссылка на наш сайт - https://b4com.tech. Если вас заинтересовала вакансия, пишите или звоните по номеру 89152033710 (Екатерина). Также можно откликнуться на вакансию в hh - https://hh.ru/vacancy/72745516. Инженер-тополог: Обязанности: Разработка ПП в Altium Designer. Формировать и оптимизировать стек МПП (стоимость — производительность) Трассировка сложных многослойных печатных плат; Подготовка GERBER (CAM) файлов для производства печатной платы; Подготовка файлов для расстановщиков (placement) и сборочных чертежей (Assembly); Взаимодействие с разработчиками и конструкторами; Участие в разработке конструкторской документации. Будет плюсом: Моделирование целостности сигналов (SI); Моделирование распределения емкостей и полигонов питания (Power); Тепловое моделирование платы; Знание цифровой, аналоговой, СВЧ схемотехники Разработка топологии сложных печатных плат, желательно с использованием «глухих» и «слепых» переходных отверстий; Требования: Опыт проектирования многослойных печатных плат для цифровых высокоскоростных устройств; Английский достаточный для чтения технической документации; Опыт работы в радиоэлектронной промышленности; Опыт трассировки печатных плат с цифровыми интерфейсами типа PCIe Gen3, DDR3/4; Понимание проблем перекрестных помех, целостности сигнала, электромагнитной совместимости; Опыт проектирования печатных плат с высокой плотностью компоновки, в том числе с применением BGA-компонентов с мелким шагом выводов; Опыт: Трассировка с выравниванием длины линий, расчетом импеданса, моделированием целостности сигнала, использованием теплоотводящих слоев; Приветствуется опыт работы с аппаратными платформами на процессорах архитектур ARM, MIPS и с высокоскоростными интерфейсами Ethernet (до 10GB, SFP), DDR3 и выше, PCIe, SATA, HDMI. Разработка посадочных мест в соответствии с IPC с учетом требований автоматической сборки ПП; Подготовка выходных файлов для производства. Согласование стеков, материалов, выбор технологии используемых в печатных платах. Условия: График 5/2; ЗП определяется по итогу собеседования; Официальное трудоустройство (белая заработная плата, оплачиваемые отпуска, больничные); После прохождения испытательного срока ДМС; 5 минут от м. Текстильщики; Компания внесена в реестр аккредитованных IT-компаний

-

Переходник-конвертер USB-PCI-E

dimasiki опубликовал тема в RS232/LPT/USB/PCMCIA/FireWire

Уважаемое сообщество. Подскажите пожайлуста по такому вопросу. Существуют ли в "дикой природе" переходники с USB на PCI-E? То есть, к компьютеру нужно подключить устройство PCI-E по шине USB, а НЕ наоборот. Потому что переходников и всевозможных адаптеров С PCI-E на USB огромное количество... Вкратце суть вопроса. Есть у меня куча радиокарт от ноутбуков, но они соответственно формата mini pci-e или M.2(что по сути и есть PCI-E). Для подключения этих крточек нужен соответсвенно ноутбук или другое хост-устройство. Хотелось бы иметь возможность подключать такие карточки через какой нибудь переходник к шине USB. Гугл нашел вот такой чип JMS583 (ссылка на производителя http://www.dgysr.com/JMS580?product_id=15&product_category=5). И соответственно на его основе переходники. Только в описаниях к этим переходникам упоминается режим накопителя, что немного сбивает с толку... Подскажите, заработает ли такая связка при установке в такой адаптер ноутбучной радиокарты? Ведь этот чип-переходник на выходе создает линию PCI-E 3.0x2...- 30 ответов