Поиск

Показаны результаты для тегов 'axi'.

-

Здравствуйте, коллеги Попал ко мне на стол VIP от Cadence под названием CDN_AXI. Подключил его классически: интерфейс+конфиг+агент+sequence. Но сигнал WVALID ведёт себя неадекватно, т.е. переводится в единицу и так в ней и висит до конца симуляции... VIP настроен на полный AXI4. У всех транзакций burst законстрейнен до длины 1. Бывало ли такое у кого и как лечится?

-

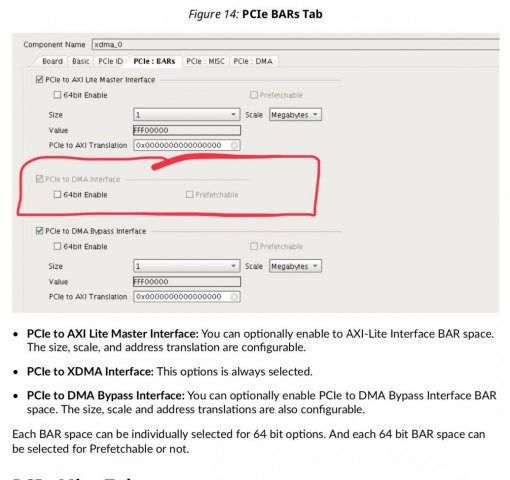

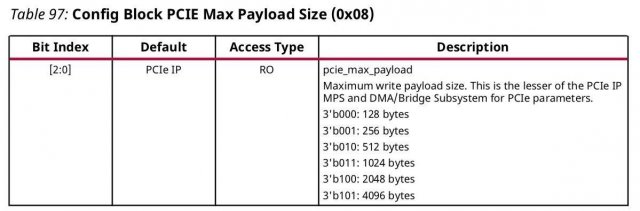

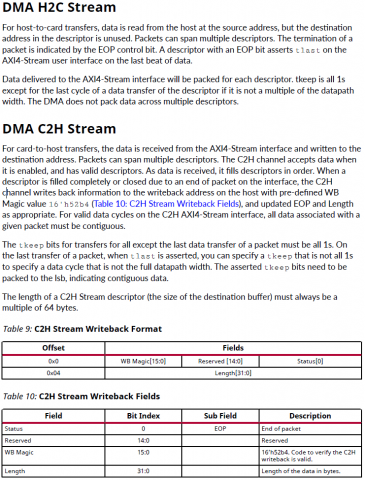

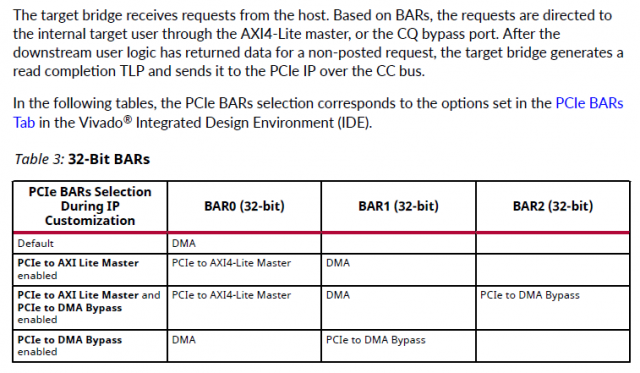

Собственно задача - с минимальными потерями времени и усилий работать с хоста через PCI-E с ускорителем в ПЛИС. Насколько я понял самый простой способ - использование ядра XDMA (обёртка над ядром PCI-E) [1], готовых драйверов xdma.ko [2] и шаблонов приложений которые идут в комплекте [3] Но после вдумчивого изучения pg195 и запуска на плате тестового примера остались вопросы, хотя они скорее системного плана, но связаны именно со спецификой ядра XDMA. Что надо от ускорителя (для определенности - пусть будет крипто-ускоритель): 1) "стримить" с хоста данные на обработку, притом чтобы ускоритель мог сообщать, что достаточно, пока больше не надо присылать данные (т.е. некий flow control на отправку) 2) уведомлять хост о том, что данные обработаны и можно забирать, и соответственно отдавать "стрим" в хост. Почему стрим в кавычках: по сути это не непрерывный стрим, а блоки по 4К (притом с заголовками, чтобы на приёмной стороне (хосте) можно было сматчить контекст - какому выходному блоку какой входной соответствовал), но по природе обработки ускоритель это как PIPE: с одной стороны вышло, с другой вышло и есть некая "глубина" внутри - чтобы начал выдавать первые данные надо несколько десятков блоков в него "застримить". Т.о. в терминах xdma для этой задачи AXI Stream подходит очень хорошо, но вот на тестовом проекте заметил нестабильную работу AXI Stream (пропадание данных) в связи с чем рассматриваю и AXI MM как альтерантиву. Но что бы написать "правильное" и надёжно работающее хостовое приложение хотелось бы понимать несколько вещей (далее список вопросов): ##### BAR ##### pg195, таблица 3, соответствующа вкладка в конфигураторе XDMA * DMA - это собственно работа с самим движком * Bypass DMA - думал что это прямой доступ к пространству памяти карточки в обход движка ДМА, но похоже это не так, это ЕЩЕ ОДНО выделенное адресное пространство (доп.канал) никак не связанное ни с движком ДМА ни с памятью в которую пишет движок ДМА. * AXI Lite Master - видимо от Bypass DMA отличается только тем, что это Lite 1.1 Смущает то, что для BAR DMA в режиме AXI MM в конфиге вивадо никак не задаётся размер BAR - это как?.. где/чем определяется размеры адресного пространства с которым работает карточка? 1.2 Далее в разделе про прерывания вскользь упомянуто, что BAR может быть _address space_ а может быть и _register space_. Надо ли держать это в уме или при использовании готового драйвера просто работать с /dev/xdma0_xxx и не париться? 1.3 Какие реальные кейсы могут быть для использования Bypass DMA ? ##### IRQ & user app ##### У самого IP-ядра есть внешние ножки прерывания, но как их использовать pg195 ответа не даёт, ограничиваясь тестовым примером проекта, в котором прерывания взводятся записью из хостовой программы в регистр в пространстве AXI Lite Master. Но как это обработать из хостовой программы совершенно неясно: 2.2 Вот мы открыли /dev/xdma0_h2c и льём туда данные, как считать прерывание "BUSY", что дескать лить хорош уже (и дальше ждать прерывания "FREE") - как это на стороне пользователя обрабатывать? 2.2 При приёме мы открываем /dev/xdma0_c2h и ждём прерывания "READY" указывающее на готовность данных в /dev/xdma0_c2h - как это на стороне пользователя обрабатывать? 2.3 Чем "правильнее" пользоваться на стороне карточки - ножками usr_irq_req и usr_irq_ack, или же механизмом MSI (msi_enable, msi_vector_width)? 2.4 В AR654444 еще описан способ загрузки драйвера в режиме поллинга (работает только в направлении c2h) - стоит ли использовать его вместо прерывания для упощения логики приложения? ##### AXI ST ##### Самое интересное: управление потоками, нарезка на "пакеты" DMA H2C Stream -------------- For host-to-card transfers, data is read from the host at the source address, but the destination address in the descriptor is unused. Packets can span multiple descriptors. The termination of a packet is indicated by the EOP control bit. A descriptor with an EOP bit asserts tlast on the AXI4-Stream user interface on the last beat of data. - т.е. на стороне хоста за формирование для AXI4-Stream сигнала tlast, который фактически нарезает пакеты как мне надо, отвечает отвечает механизм, выставляющий бит EOP (в TLP???) 3.1 достаточно ли для user app указать size=4K, для формирования EOP в xdma.ko? 3.2 см. пп.1.1 если мы не задали размер BAR для DMA, то кто будет заботиться о буферах в движке DMA на карточке и в пользовательском РТЛ коде? Буферы в движке DMA на карточке вообще черный ящик: вот отправим мы пакет с size=1М - куда его сохраняет движок DMA? - не налету же он его в пользовательскую логику передаёт??? 3.3 по размерам нашёл такое упоминание в PG195, эти значения как-то завязаны на размер внутренних буферов движка ДМА??: DMA C2H Stream -------------- For card-to-host transfers, the data is received from the AXI4-Stream interface and written to the destination address. Packets can span multiple descriptors. The C2H channel accepts data when it is enabled, and has valid descriptors. As data is received, it fills descriptors in order. When a descriptor is filled completely or closed due to an end of packet on the interface, the C2H channel writes back information to the writeback address on the host with pre-defined WB Magic value 16'h52b4 (Table 10: C2H Stream Writeback Fields), and updated EOP and Length as appropriate. - тут вроде бы тоже всё прозрачно - нарезаем пакаты для отправки сигналом tlast в AXI4-Stream, который по идее должен устанавливать в дескрипторе поле EOP 3.4 Удаляет ли при приёме дескриптор с WB Magic драйвер xdma.ko или же его должно удалять пользовательское приложение? 3.5 не очень понятна строка "For valid data cycles on the C2H AXI4-Stream interface, all data associated with a given packet must be contiguous" - означает ли это, что до взведения tlast надо держать tvalid и лить данные без пропуска клоков (иначе движок ДМА "отрежет" и отправит пакет на хост по таймауту)? ##### AXI MM ##### 4.1 опять см. пп.1.1 - как задаётся размер пространства для AXI MM? В интерфейсе конфигурирования нет такой настройки. ##### источники ##### [1] https://www.xilinx.com/support/documentation/ip_documentation/xdma/v4_1/pg195-pcie-dma.pdf [2] https://github.com/Xilinx/dma_ip_drivers [3] https://github.com/Xilinx/dma_ip_drivers/tree/master/XDMA/linux-kernel/tools

- 47 ответов

-

- pcie

- pciexpress

- (и ещё 8 )

-

Добрый день. У меня, что называется, быстровопрос, для тех кто в теме. Никогда ранее не работал с ethernet и вообще пакетной передачей. Использую 10G/25G Ethernet subsystem и к нему прикручен AXI DMA контроллер (примерно как в https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/18842542/Baremetal+XXV+Ethernet+driver с тем отличием что у них MCDMA, у меня просто DMA), который берет данные для передачи из памяти и пихает в stream-интерфейс ethernet. И точно так же берет принимаемые данные из stream-интерфейса и пишет в память. Никакого fifo-буфера между ними нет. Данные пока передаю в простом loopback на трансивере самому себе. При передаче пакетов я вижу, что в процессе подачи данных на ethernet-контроллер на потоковом интерфейсе могут возникать паузы когда tvalid уходит в 0. Контроллер воспринимает это, видимо, как окончание пакета (несмотря на отсутствие tlast). В итоге на приемной стороне я вместо одного пакета вижу пачку невалидных пакетов разной длины (и, видимо, не в loopback-тесте, а через настоящий свитч, эти пакеты не пройдут). По моим представлениям это должно работать как-то не так. Я так понимаю, нужно обеспечить непрерывную подачу данных на ядро ethernet: Увеличить скорость памяти. Но не факт, что это решит проблему (а с внешней DDR точно не решит) Поставить FIFO-буфер размером в один пакет. Но это какой-то перерасход ресурса (особенно если использовать jumbo-фреймы) и лишняя задержка - нужно включить fifo в packet mode чтобы он накапливал весь пакет, потом только отдавал дальше. Что вообще обычно с этим делают?

-

помогите разобраться с AXI lite

Drakonof опубликовал тема в Работаем с ПЛИС, области применения, выбор

Всем привет, друзья помогите разобраться с AXI lite. Vivado 2018.3, linux mint Для начала, думаю можно просто зажечь диоды(их всего 4) на платке с помощью axi_gpio ip и моего контроллера, который пока не работает. Кто знает, может подскажет где ошибка. Диоды исправные, назначены верно, частота подается. Спасибо `timescale 1 ns / 1 ps module project_1 # ( parameter integer C_M_AXI_ADDR_WIDTH = 32, parameter integer C_M_AXI_DATA_WIDTH = 32 ) ( input wire CLK, input wire A_RESET_N, output wire [C_M_AXI_ADDR_WIDTH-1 : 0] M_AXI_AWADDR, output wire [2 : 0] M_AXI_AWPROT, output wire M_AXI_AWVALID, input wire M_AXI_AWREADY, output wire [C_M_AXI_DATA_WIDTH-1 : 0] M_AXI_WDATA, output wire [C_M_AXI_DATA_WIDTH/8-1 : 0] M_AXI_WSTRB, output wire M_AXI_WVALID, input wire M_AXI_WREADY, input wire [1 : 0] M_AXI_BRESP, input wire M_AXI_BVALID, output wire M_AXI_BREADY, output wire [C_M_AXI_ADDR_WIDTH-1 : 0] M_AXI_ARADDR, output wire [2 : 0] M_AXI_ARPROT, output wire M_AXI_ARVALID, input wire M_AXI_ARREADY, input wire [C_M_AXI_DATA_WIDTH-1 : 0] M_AXI_RDATA, input wire [1 : 0] M_AXI_RRESP, input wire M_AXI_RVALID, output wire M_AXI_RREADY ); reg axi_awvalid; reg axi_wvalid; reg [C_M_AXI_DATA_WIDTH-1 : 0] axi_ardata; reg start_single_read; reg start_resp_read; reg axi_arvalid; reg axi_rready; reg axi_bready; assign M_AXI_BREADY = axi_bready; assign M_AXI_RREADY = axi_rready; // адрес на axi, он же регистр данных порта 1 axi_gpio assign M_AXI_AWADDR = 32'h40000000; // записать в регистр данных порта gpio 1 данные, значение должно загореться на диодах assign M_AXI_WDATA = 32'h0000000A; assign M_AXI_AWPROT = 3'b000; assign M_AXI_AWVALID = axi_awvalid; assign M_AXI_WVALID = axi_wvalid; assign M_AXI_WSTRB = 4'b1111; always @(posedge CLK) begin if (A_RESET_N == 0) begin axi_awvalid <= 1'b0; axi_wvalid <= 1'b0; end else begin axi_awvalid <= 1'b1; axi_wvalid <= 1'b1; if (M_AXI_AWREADY && axi_awvalid) begin axi_awvalid <= 1'b0; start_single_read <= 1'b1; end if (M_AXI_WREADY && axi_wvalid) begin axi_wvalid <= 1'b0; end end end always @(posedge CLK) begin if (A_RESET_N == 0) begin axi_bready <= 1'b0; end else if (M_AXI_BVALID && ~axi_bready) begin axi_bready <= 1'b1; end else if (axi_bready) begin axi_bready <= 1'b0; end ; end assign M_AXI_ARADDR = 32'h40000008; assign M_AXI_ARPROT = 3'b001; assign M_AXI_ARVALID = axi_arvalid; always @(posedge CLK) begin if (A_RESET_N == 0) begin axi_arvalid <= 1'b0; end else if (start_single_read) begin axi_arvalid <= 1'b1; end else if (M_AXI_ARREADY && axi_arvalid) begin axi_arvalid <= 1'b0; end end always @(posedge CLK) begin if (M_AXI_RVALID && ~axi_arvalid) begin axi_ardata <= M_AXI_RDATA; end end always @(posedge CLK) begin if (A_RESET_N == 0 ) begin axi_rready <= 1'b0; end else if (M_AXI_RVALID && ~axi_rready) begin axi_rready <= 1'b0; end else if (axi_rready) begin axi_rready <= 1'b0; end end endmodule -

В двух словах. Во-первых, это мой первый опыт с Zynq, во-вторых, не могу уловить суть работы с потоковой шиной AXI-Stream. Или не понимаю сообщений от тайминг-аналайзера. Теперь подробней... Перед собственно запуском АЦП, наслушавшись как в Zynq все быстро и удобно, посмотрев несколько видео, и почитав несколько статей, создал простой проект, где Microblaze для конфигурирования в будущем АЦП и ЦАП, а ARM уже для работы с данными. Есть общая память между Zynq и Microblaze, есть общая периферия. Частота работа с периферией 50 Мгц. Раньше делал со стороны ARM 100 МГц, сейчас сделал поменьше. Не уверен, что выходную частоту процессорного ядра можно использовать в FPGA безболезненно, поэтому пропустил на всякий случай клок через Clock-wizard. Создал пару кастомных компонентов куда в дальнейшем перекочует работа с АЦП и ЦАП соответственно. И для проверки "скелета" все соединил и собрал. Сообщения про времянки уверяют меня, что ничего не работает. Пробовал вставлять регистры, вставил двухклоковую FIFO, опустил частоту работы с портом HP до смешных значений. Увеличил разрядность с 32 до 64 разрядов, завел два выхода в компоненте и использовал сразу два порта HP, помня рекомендацию Xilinx, что подключать нужно к портам через один, т.е. к 0 и 2 или к 1 и 3. Можно услышать от опытных людей критику по структуре проекта в целом и рекомендации по констрейнам? Я так понял, что как и для спартан-6 констрейны нужно прописывать только ко входной частоте, а производные клоки просчитываются автоматически. Тут также? Проект размещу по ссылке, т.к. его размер превышает ограничение в 5 Мб: EK-Z7-ZC702-G_Zynq_MB

- 19 ответов

-

- zynq

- microblaze

- (и ещё 4 )

-

В DDR памяти Xilinx Ultrascale+ находятся два равных по длине буфера, буфер A ( последовательные данные А1, А2 ….. ) и буфер В ( последовательные данные В1, В2 …..). Эти буфера читаются под контролем DMA на шину AXI Stream и должны попасть соответственно на два входа DSP блока, но строго синхронно (A1, B1) , (A2, B2) ….. Проблема просто решается в случае 2-x FIFO c embedded шиной (DIN, clk_wr, clk_wr_en, empty и DOUT, clk_rd, clk_rd_en). Подскажите как перейти с AXI Stream на embedded FIFO? Возможно есть более правильное/простое решение? AXI MM + BRAM_CTRL + embedded FIFO?