Поиск

Показаны результаты для тегов 'pci express'.

-

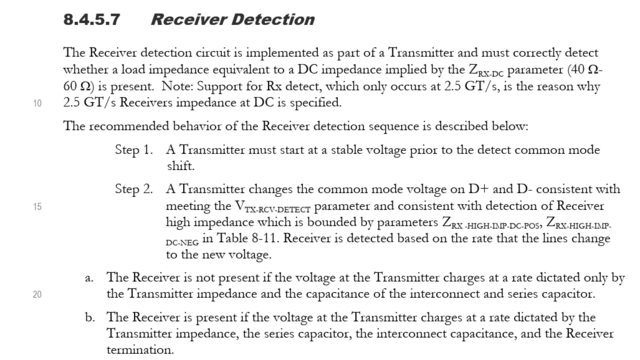

Доброго всем дня, Столкнулся с ещё одной проблемой наличия линка на PCI-E у плат с Артиксами, причём в этот раз LTSSM не может пройти дальше практически самой начальной фазы - Detect.Active, т.е. не отрабатывает процедура Receiver Detection. В описании GTP есть следующий пункт: Судя по нему в начале процедуры определения наличия приёмника ПЛИС должна установить уровень сигнала на линиях TXN и TXP равным (Vdd - Vswing/2). Отдельный вопрос, какое именно значение Vswing они считают правильным, но я предполагаю что 500 мВ. Vdd судя по всему это Vmgtavtt, т.е. 1,2 В. Т.е. в итоге на выходах ПЛИС должно появиться значение напряжения около 0,95 В. Далее, судя по описанию, происходит отключение управляющей цепи и уровень сигнала должен вернуться к Vcmoutac (1,2 В / 2 = 0,6 В) и ПЛИС через заданный интервал должна измерить величину напряжения на линиях TXP/TXN, по которому принимается решение о наличии на линии приёмника. Это полностью согласуется с логикой описания этого процесса в спецификации PCI-E: Однако по факту я наблюдаю совсем другую картину: 1. перед началом процедуры определения приёмника напряжение на выходах 560 мВ; 2. при включении режима определения приёмника на выходе ПЛИС появляется уровень 1,18 В с крутым фронтом (если приёмника нет или он не готов), если приёмник есть и с ним всё хорошо, то уровень около 960 мВ. 3. далее передатчик ПЛИС формирует крутой спад сигнала и уровни возвращаются к исходным 560 мВ; Т.е. не видно никакого длительного процесса заряда-разряда конденсатора, по которому бы ПЛИС с помощью компаратора (сравнивающего уровень сигнала в линии с опорным значением) могла судить о наличии приёмника на другом конце. Напротив, всё выглядит так, что ПЛИС формирует достаточно мощный импульс и в зависимости от получившегося практически стабильного по времени уровня напряжения принимает решение о наличии/отсутствии приёмника. Проблема в том, что на некоторых слотах x16 (подключённых напрямую к процессору) процессор далеко не сразу правильно настраивает свои приёмники (подключает терминаторы) или они не сразу включаются и в результате ПЛИС не может определить их наличие, а значит пойти дальше по графу состояний LTSSM. При этом особенно интересно, что в то же самое время, пока ПЛИС не может определить наличие приёмника на другом конце, процессор успешно видит приёмник в ПЛИС и начинает слать TS1/TS2, пытаясь поднимать линк. Однако через некоторый таймаут всё это прекращается, т.к. он по всей видимости не дожидается получения TS1/TS2 от ПЛИС, что логично, т.к. ПЛИС не видит приёмника. Т.е. по факту процессор сам себе обрубает линк с платой. При этом после тёплого ресета линк стабильно поднимается (процессор прогрелся и у него стало всё хорошо? 😉). Такое поведение наблюдается на паре материнских плат и число чудящих Artix`ов всего два. При этом такая проблема далеко не нова - https://support.xilinx.com/s/article/51135?language=en_US Правда в моём случае процессор не третьего, а четвёртого поколения, для которого такой эрраты в доступной документации нет и значение TX_RXDETECT_REF уже равно рекомендованному 3'b011. На проблемных платах помогает уменьшение TX_RXDETECT_REF до значения 3'b010, при этом на рабочих платах увеличение значения TX_RXDETECT_REF до 3'b100 ломает установку линка. Однако логика работы параметра TX_RXDETECT_REF непонятна, т.к. в первую очередь кажется, что этот параметр определяет пороговое значение опорного уровня сигнала внутренного компаратора, при котором приёмник считается подключенным к линии. Однако если установить значение 3'b000, то я вижу, что максимальный уровень выходного сигнала ПЛИС в процессе проверки наличия приёмника снижается до 1,03 В вместо исходных 1,18 В. При этом Detect.Active пролетает с первого раза. Если всё так хорошо, то почему AMD (Xilinx) рекомендует ставить 3'b010 в крайнем случае и то после консультации с их техподдержкой? Есть-ли у кого-нибудь понимание, как на самом деле работает механизм определения наличия приёмника у Xilinx в седьмой серии? В шестой серии, судя по осциллограммам, механизм реализован плюс-минус также. Чем на практике чревата установка низких значений TX_RXDETECT_REF? PS: предложения вида "забить и забыть" принимаются, но игнорируются, т.к. в серии возможны массовые отказы и/или проблемы в совместимости. Поэтому ищется решение, которое бы гарантировало работоспособность плат на Артиксах в максимально широком спектре материнских плат и платформ.

-

Продолжаются приключения с Ultrascale и PCI-E портом. Плата пробовалась на бытовом компьютере через CPCI-Serial самодельный переходник - отлично, пробовалась в корзине с i7 процессорным модулем - отлично. Но вот, этот i7 модуль умер. И срочно нашли замену, Fastwel CPC-512. И с ним проблемы На этом CPC-512 чтение запись MMIO работает отлично, MSI прерывания ходят. Но по зависанию прошивки ПЛИС, я обнаружил, что зависание прям с первой же попытки, не случайное не периодическое, а просто с ходу, когда я пытаюсь делать MRd запросы по шине s_axis_rq и получать ответы по шине m_axis_rc, тут "s" это имеется ввиду что это у PCI-E ядра это slave, и "m" наоборот, просто не стал инвертировать эти буквы RQ - запрос, RC - тут ответ. На предыдущих системах, которые я описал всё работало, даже на Байкал-Т1 работало ровно это самое. Но вот пришла система на замену, и другой нет, и она не хочет давать ответы! Работало с адресами, выделенными через dma_alloc_coherent, но пробовал также и через dma_map_single - результат всё тот же, оно просто не хочет давать результаты чтения! Как понять, что запрос ушел без ошибки? Ориентируюсь на s_axis_rq_tready. Пробовал выделять не сколько надо, а больше, например по размеру страницы памяти Подозрения: 1) Ориентируюсь на if(s_axis_rq_tready == 4'b1111) begin, а вдруг оно просто один бит ready? 2) Оно дает мне ready, но вдруг оно как то сигнализирует что надо повторить? Я снимаю valid бит на отправку лишь когда есть второй s_axis_rq_tready == 4'b1111 3) А может настройка компьютера какая то неверная? Что предположительно может быть 4) Я проверял, что у меня dma_mask 32 битное, все адреса 32 битные должны быть в запросах MWr и MRd 5) У меня фиксированные tag биты и прочие биты не меняю в запросе, но для одного запроса это не должно быть проблемой. Увы, на первом же и повиснет, то есть повиснет в месте где жду ответ CplD Добавлено: Драйвер для Linux. Может какие то флаги в kmalloc добавить дополнительные? GFP_DMA есть. Может работать через softmmu - не пробовал еще, или это не относится к реальному железу. Может какие диапазоны указать пошире. Явно какая то настройка кроется в ОС, и в БИОС всё облазил

- 38 ответов

-

- kintex ultrascale

- pcie

-

(и ещё 3 )

C тегом:

-

Выбор PCI Express Switch

kirra.cat опубликовал тема в ISA/PCI/PCI-X/PCI Express

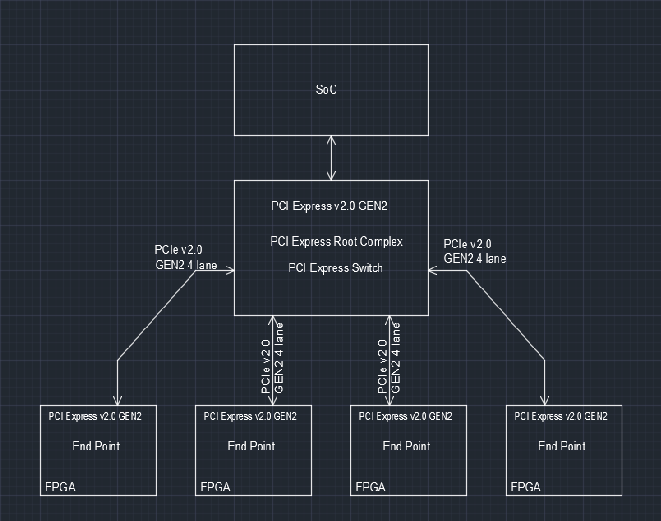

Добрый день. Проектирую свое первое устроство с использованием PCI Express, и появился такой вот вопрос. Для начала хотел несколько описать, что из себя представляет разрабатываемая мной система. Система представлет из себя совокупность некой SoC, и 4 конечных точек, соединеных коммутатором PCI Express (как на приложенной картинке). Каждый квадратик на картинке - это отдельная плата. Т.к. этот SoC (реализованный на жирной ПЛИС) чёт какой-то сложный получается, поэтому было принято решение PCI Express Root Complex из него выкинуть. В итоге, по задумке, поставить микросхему коммутатора PCI Express со встроенным Root Complex, либо если такой не бывает, то отдельную микросхему Root Complex и отдельную микросхему коммутатора. Собственно вопрос: бывает ли микросхемы коммутаторов со встроенным Root Complex? Если есть, то можете подсказать как они называются. Даже не обязательно, чтобы Root Complex и коммутатор были в одной микросхеме, вполне устраивает вариант, когда коммутатор и Root Complex в разных микросхемах. P.S. Просто я таким микросхем (коммутаторов со встроенным Root Complex) не смог найти, скорее всего не правильно давал гуглу запрос на поиск -- С наилучшими пожеланиями, kirra