-

Постов

2 052 -

Зарегистрирован

-

Посещение

Репутация

2 ОбычныйИнформация о Krys

-

Звание

Гуру

Контакты

-

Сайт

Array

Информация

-

Город

Array

Посетители профиля

5 841 просмотр профиля

-

Китайские ПЛИС

Krys ответил МАСТЕР LO тема в Работаем с ПЛИС, области применения, выбор

https://inf.news/en/economy/7b07c778506a36eeb6bf1b5381f930b3.html -

Krys подписался на Design Space Explorer , Китайские ПЛИС , Vivado ML Edition - 2022.1 и 2 других

-

Vivado ML Edition - 2022.1

Krys ответил Alex77 тема в Среды разработки - обсуждаем САПРы

Я проверил, можно. Только что закончил скачивание и установку. Сначала поставил полный пакет из закромов, 2022.1, а затем на него сразу аптейт 2022.1.2. -

Vivado ML Edition - 2022.1

Krys ответил Alex77 тема в Среды разработки - обсуждаем САПРы

Здравствуйте. Запускаю установщик 2022.1 из закромов, пишет сразу ошибку There is no valid Xilinx installation that this Update can be applied to. Подскажите пожалуйста, ЧЯДНТ? Надо установить какую-то предыдущую версию? Как точно узнать, какие промежуточные нужно поставить, чтобы эта поставилась? Ведь даже это весит немало (около 70 гигов). -

Тут тоже внутренний перфекционист негодует ))) Вопрос мой скорее можно ли штатным образом так сделать

-

ну так тоже не очень красиво (чисто из перфекционизма). Всё равно вытаскивается мнимая часть, которая здесь не участвует в вычислениях. Мне бы как-то получить доступ только к вещественной части числа на запись. Вот в этом вопрос.

-

Спасибо за подсказку, действительно, элементарно, формула Эйлера, что ж я раньше об этом сам не догадался )) Однако в моём вопросе меня интересовал общий случай, любые функции и переменные. Не знаете решение? И также есть у меня вопрос: можно ли получить доступ к отдельным квадратурам комплексного числа? Вот типа допустим есть у меня c = x + 1i*y Я бы хотел записать примерно такое: c.Re = с.Re*3 Т.е. выполнить некоторые преобразования только с одной квадратурой. Сейчас я знаю лишь способ сначала разложить на отдельные вещественные числа квадратур, выполнить преобразование с одной квадратурой, затем собрать обратно в комплексное число: x = real(c); y = imag(c); x = x*3; c = complex(x, y); Но чисто из перфекционизма мне так делать не нравится. Хочется как-то напрямую получить доступ к квадратуре.

-

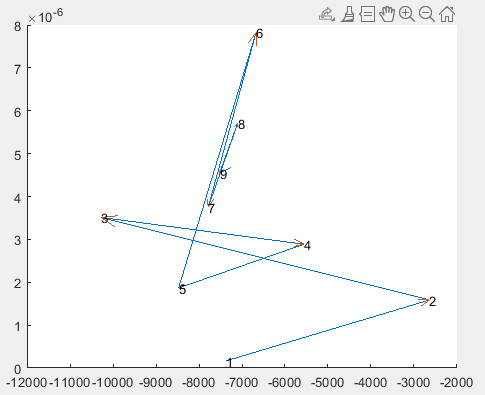

На основе вашей подсказки доработал свою функцию (изменения под комментариями со словами aspect ratio): И вызывающий её код теперь выглядит вот так: Теперь выглядит неплохо: Так что в принципе вопрос можно считать решённым.

-

Вот-вот, именно это у меня и получалось ))) Спасибо за подсказку! Попробую разобраться ) Я так понимаю, вы в матлабе далеко не новичок. Не загляните в тему? https://electronix.ru/forum/index.php?app=forums&module=forums&controller=topic&id=168358 Разобрался! Очень просто оказывается. Как здорово, что вам приходят в голову такие вещи, со стороны кажется: ну почему я сам не догадался )) Я так понимаю, можно и с помощью quiver такой же финт провернуть?

-

Vivado ML Edition - 2022.1

Krys ответил Alex77 тема в Среды разработки - обсуждаем САПРы

не поделитесь? Сейчас только выложили 2022.1.1 https://electronix.ru/forum/index.php?app=forums&module=forums&controller=topic&id=79468&do=findComment&comment=1825023 -

Здравствуйте. Есть у меня желание чисто ради перфекционизма кода в матлабе подставить сразу несколько выходных переменных одной функции в несколько входных переменных другой функции? Гулил, нашёл похожую проблему, но решения не увидел: https://uk.mathworks.com/matlabcentral/answers/180164-use-a-function-that-returns-multiple-values-as-input-argument-to-another-function Своими словами: Есть встроенная функция [x,y] = pol2cart(theta,rho) Я хотел бы из x и y сделать комплексное число такой подстановкой: С = complex(pol2cart(theta,rho)) Но при такой записи передаётся только вещественная часть, мнимая по нулям. Пока реализовал через промежуточные переменные, но это костыли: [x,y] = pol2cart(theta,rho) С = complex(x,y) Может есть всё же способ сделать красиво, в одну строчку, без промежуточных переменных?

-

Спасибо. Хотел напрямую слямзить этот код. Но он бажный. В некоторых направлениях стрелки рисует нормально, в некоторых коряво. В результате свой написал (см.ниже). Огромное спасибо за подсказку. Да, я смотрел эту функцию, но не так понял. Посчитал, что 3й и 4й аргументы это модуль и угол вектора. Испугался полярных координат, что типа некогда искать функции по пересчёту. В результате по примеру по ссылке из второго сообщения сделал свою функцию: И потом увидел ваше сообщение. Да, quiver в принципе повторяет то, что я сделал, только куда проще. К сожалению, общая проблема моей функции и quiver в том, что стрелки выглядят красиво только при одинаковом масштабе по вертикали и горизонтали. А у меня это просто ужасно разные масштабы, и стрелки вообще ломают весь график, на графике видно только стрелки ))) Пока не представляю, как исхитриться, чтобы при моих условиях красиво было нарисовано.

-

Здравствуйте. Вопрос такой. Вот есть у меня вектор значений X и вектор значений Y какого-то процесса, который последовательно передвигается от одной точки к другой. Если я напишу plot(X, Y), то мне нарисует изломанную кривую из прямых линий, соединяющих мои точки в X и Y. Вроде мне так и надо. Но мне бы ещё к этому в конце каждой линии, соединяющей мои точки в X и Y, пририсовать хвостик у стрелочки. А желательно ещё и номерок подписать, какая это по счёту стрелочка. Чтобы я понимал, в какой очерёдности и в каком направлении движется процесс. Я попробовал annotation. И всё бы хорошо, но там точные координаты не задать, там либо в пикселях, либо в см и т.п., короче привязано к самому окошку графика. А мне бы в единицах измерения моего процесса. feather, quiver смотрел - вроде не то.

-

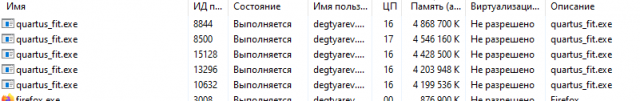

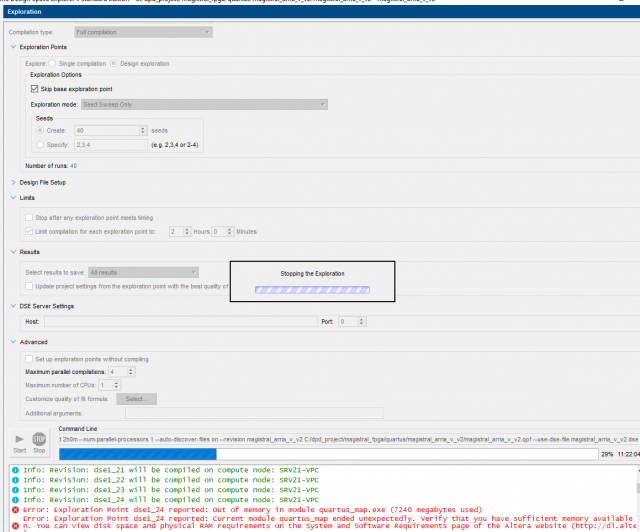

Design Space Explorer

Krys ответил Serega Doc тема в Среды разработки - обсуждаем САПРы

Дополнение: DSE оставляет для каждой exploration point отдельную папку. Там есть запакованный архив проекта, а есть незапакованный проект. Я попробовал распаковать и скомпилить из архива. И попробовал незапакованный скомпилить. Проблема со слаками остаётся. Да, ещё есть кнопка Write to project на вкладке Results. По её нажатию я ожидал, что требуемые настройки запишутся в мой проект основной, откуда я из квартуса через меню Tools и вызвал DSE. Но я не увидел, чтобы что-то поменялось при нажатии этой кнопки. Как будто кнопка не действует. -

Design Space Explorer

Krys ответил Serega Doc тема в Среды разработки - обсуждаем САПРы

Подниму бородатую тему. Полез в сабж решать проблему со слаками. Да, в сабже она решилась. Но как я могу перетащить в свой основной проект (для разводки чисто в квартусе, без использования каждый раз сабжа) те настройки, что были сделаны для exploration point с лучшим результатом? Я попробовал тупо скопировать файл проекта *.qsf, дам видно, что только seed отличается. Развёл этим файлом проекта - никуда не делись слаки. Значит данная exploration point имеет и другие настройки, кроме seed, которые отличаются от моего основного проекта, но где их выколупать - я не знаю. Также есть жалоба на кривоватость работы... -

QUARTUS, MODELSIM

Krys ответил aosp тема в Среды разработки - обсуждаем САПРы

Переделал всё на верилог. Умножение сделал через генерацию LPM_MULT в визарде. Прописал latency большую в надежде, что упихает в регистры внутри DSP-блока. Нифига. Сделал снаружи на рассыпухе. Сейчас умножение напишу прямо на верилоге, может поможет. Дополнение: но при этом слаков больше нет. Значит переделывать не буду, так и оставлю, не стоит оно идеализации.