dmitrykhom

Участник-

Постов

20 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о dmitrykhom

-

Звание

Участник

-

Проблема в том, что этот 32x таймер работает от кварца 25 МГц, который на всем диапазоне температур, что я испытывал (-20+65), дает нестабильность до 20 ppm, а это много. У кварца 32768 эта нестабильность в разы меньше. Устройство будет стоять на холоде включенным без синхронизации, и за сутки отстанет/набежит больше положенной 0,5 секунды. Есть лучше - таймер EMAC_PTP, которому еще и дисперсию задавать можно. И корректировать, просто занеся в специальный регистр разницу. Но он работает от AHB, который, в свою очередь, то 25 МГц. Никакие приоритеты здесь не помогают, все виснет глухо.

-

Момент перехода в другие сутки тогда придется вычислять, хотя это тоже можно при желании. За дельту спасибо, простое решение. Действительно, уперся в эту синхронизацию... Читается без задержек, но для точности результата приходится ждать перехода регистра подсекунд на следующее значение (до 4 мс задержка), но там ничего не вешается. Спасибо!

-

Интересно, если к этим регистрам сделать DMA, то получится работа или нет?! Проверю в следующем году. И, если получится будут ли тормоза

-

Может быть, плохо искал, но в мануале этого не нашел. Хотел писать часто, так как ERTC даёт возможность получать точные метки времени, притом кварц 33768 более термостабилен, чем кварц процессора на 8 МГц. Но когда устройству приходит точное время, и оно точнее получаемых меток от ERTC, то хочется в ERTC обновить время. В принципе, я могу отказаться от термостабильного кварца, а в моей задаче можно обойтись EMAC_PTP.

-

Продолжаю писать под этот мк, вот добрался до ERTC (часы реального времени). Пришлось хлебнуть несладко, есть интересные тонкости. (Например, если ввести в режим инициализации (ERTC->IMEN), ERTC->IMF поднимется, и в этом режиме выполнить рестарт мк, то ERTC->IMF сбросится, а часы будут стоять. Поэтому узнать, идут ли часы реально, можно только дождавшись, пока они тикнут или нет.) Но речь сейчас не о том... Вот код, который мне нужен, но мне он не нравится: ERTC->time = stime.time; // Время ERTC->date = sdate.date; // Дата ERTC->ctrl_bit.hm = ERTC_HOUR_MODE_24; Разумеется, режим доступа в область pwr включен (и не выключаю), защита записи ERTC отключена (и не включаю), и перед этим была команда ввода в режим инициализации - здесь все проверено. Так вот. Регистры пишутся, часы корректируются. НО каждая из этих команд глухо вешает процессор приблизительно на 100 мкс! Это чересчур - у меня прерывание раз в 10 мкс, мне так нельзя. Вопрос: как этого избежать? Подскажите, пожалуйста Если не подскажете, то мне ничего не останется, как не трогать ERTC, и делать это только при сигнале отключения питания. (Кстати, команды вкл/откл режима доступа в pwr тоже вешают где-то на 200 мкс, снятие/установка защиты от записи в ERTC тоже порядка 20 мкс, поэтому от них пришлось отказаться.)

-

Здравствуйте. Ничего полностью не соответствует. Нужно везде работать напильником

-

Как это задействовать (внеочередное исполнение)? Есть ли какой пример на ассемблере? Я не спорю, что M7 эффективнее. Я просто сравнил конечный результат, используя прагматичный расчет. Мне важно, что сможет процессор успеть сделать за цикл вычислений, и сколько будет стоить спецификация PCB.

-

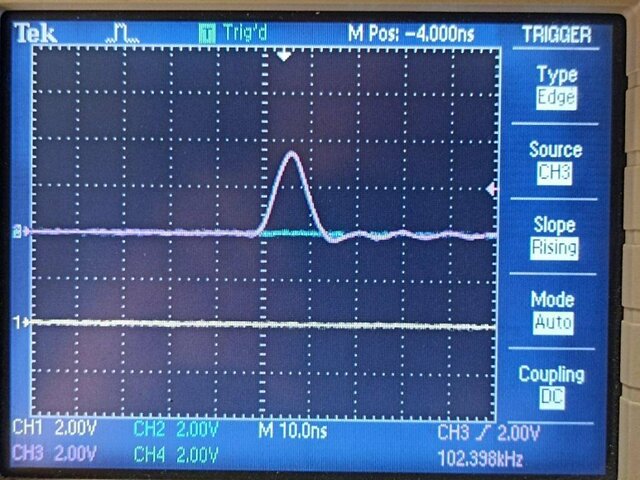

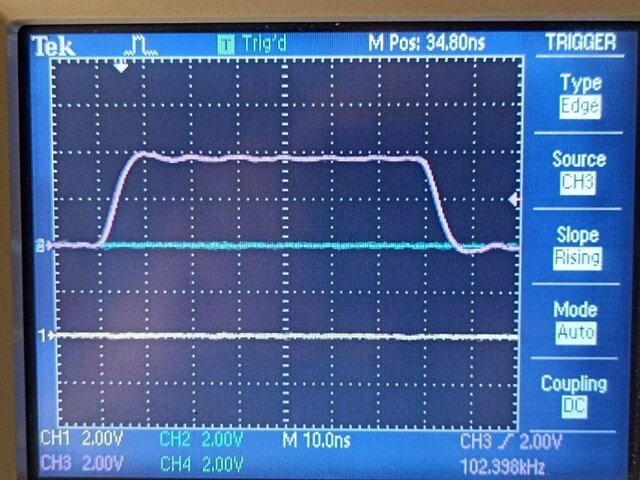

Нашел ошибку у себя: задал частоту процессора вдвое меньше (144 против 288). Но результаты исследования были очень полезны! Я поигрался с памятью, с оптимизацией и вот что получилось. Попробовал поиграться с взятием из памяти - получилось улучшить. Пример (R0 = 0x20001A7C, R2 = 0x20001A80, R4 = 0x20001A84): LDR R1, [R0] ADD R1, #0 STR R1, [R0] LDR R3, [R2] ADD R3, #0 STR R3, [R2] LDR R5, [R4] ADD R5, #0 STR R5, [R4] выполняется 49 нс (14 тактов), а последовательность LDR R1, [R0] LDR R3, [R2] LDR R5, [R4] ADD R1, #0 STR R1, [R0] ADD R3, #0 STR R3, [R2] ADD R5, #0 STR R5, [R4] выполняется 42 нс (12 тактов). (Да, я мерил своим любимым GPIO, но все сходится). В принципе, разница невелика, но есть. Да, AT действительно работает быстрее STM. Поэтому, если речь идет об оптимизации, то лучше, если будет длительная вычислительная цепочка. Т.е. взял значения - и долго-долго обрабатываешь, потом кладешь. Но, если говорить о целочисленных вычислениях, то взять значения особо-то и некуда - регистров всего 12. Иное дело обстоит с регистрами FPU - их 32. Но AT работает быстрее! Так, я запустил весь алгоритм (без оптимизации!), и получилось, что эффективность возросла где-то на 30-40 % (собственно, пропорционально тактовой частоте - 288/216 МГц). Выводы. 1. AT на Cortex-M4 работает быстрее во всех отношениях, чем STM на Cortex-M7. 2. Оптимизация при целочисленных вычислениях не имеет смысла - мало регистров, да и процесс, как правило, один. 3. Оптимизация при "плавучных" вычислениях даст превосходный результат, т.к. есть 32 FPU регистра. 4. Если программа, требующая быстрой работы (0WS), до 512 кБ, то не надо кэшировать ее, создавать системы управления памятью - она сама грузится в SRAM и работает быстро. 5. Цена где-то в 2-3 раза ниже у китайца. Резюме: выбираю китайца AT32F437, всё закладываю под него. Но делаю так, чтобы можно было запаять STM32F745. Всем спасибо!

-

Всё правильно - gpio вносит задержки, и мой осциллограф тоже. Но мне бы сейчас разобраться с гораздо бо́льшими задержками, которые вносятся, елки-палки, обработчиком команд! А вот за это спасибо. Похоже, что в этих деталях кроется самое основное.

-

Процесс запущен в прерывании, его некому перебивать. В фоновом цикле запускал - результат тот же. Снимал отладчик, втыкаю плату в розетку - результат тот же. Идея правильная, об этом я забыл. Попробую. Ещё как честно! А если меня AT обманывает? Картинка, мною представленная, очень стабильна, с небольшим джиттером. Если поставить повторение этих команд, картинка будет стабильно повторена. Я не запомнил точные данные, но команды приблизительно от 1 до 5 единиц по счётчику. Посмотрю этот бит. Уверен, так задано в проекте, да и по disassembly это видно. Перерыл все документы, ничего не нашел по конфигурации банков. Везде написано, что кэширование происходит автоматически в старшую область sram. Причем я смотрел - в этой области данных из флэшки нет. Видать, это сделано для защиты кода инструкций. Почему вторая инструкция так долго выполняется. Это же чтение данных из памяти, и оно выполняется дольше, чем запись. Думал по первой инструкции, может, процессор долго лезет к смещению РС. Делал локацию рядом с перепрыгиванием и даже до команды - результат тот же.

-

Думал над этим. Но это тот же cortex-M4, возможно, чуть более лучший, чем AT32F437. Но GD он ввел санкции, в отличие от AT, поэтому я уж лучше останусь на STM, потому что там cortex-M7, и скорость адекватная. То самое прерывание, которое запускается раз в 10 мкс, на STM отрабатывает за 1..1,2 мкс (т.е. загрузка ресурсов 10..12%), а на AT оно же работает 2,7..3 мкс (загрузка 27..30%). Я понимаю, что на AT стоит Cortex-M4. Но всё же было заявление с исполнением команд без задержек. Ну даже допустим 2 мкс было бы, но 3 - это чересчур..

-

PHY можно взять например KSZ8041 и повесить ему кварц или генератор. Паралельно точно ничего не запущено! Процесс запущен в единственном прерывании, которое срабатывает от EXINT по спаду на ноге PC9 раз в 10 мкс . Нет ни DMA, ни чего-то еще. Я запустил протестировать самые критические процедуры, поэтому я грузанул весь проект, но ничего не инициализировал. Код получился большой, потому что я загружал ассемблерный код, а он не оптимизируется. Это чтоль DWT-счетчик? Спасибо, что обратили мое внимание на джиттер! Буду наперед интересоваться такими вещами. Но могу сказать, что у меня очень много устройств на ETH PHY, тактируемых от STM MCO1, и обмен отличный, связь всегда есть. Про AT32F437 - буду использовать отдельный источник.

-

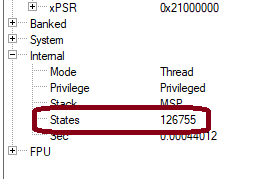

Всем доброго времени! Занялся переносом программ с STM32F745 на AT32F437 и наткнулся на вещи, не совместимые с документацией.... Также для меня было новостью, что если используешь кварц 25 МГц, то выстроить 288 МГц не получится. А если взять иной кварц, то не получится с CLKOUT выдать 25/50 МГц для работы ETH PHY. Печалька, но придется использовать кварц 16 МГц, разгонять до 288 МГц, а для ETH использовать свой собственный кварц или генератор. Но дело даже не в этом. Я вижу, что некоторые ассемблерные команды исполняются где-то за 6-7 нс, но некоторые - аж за 28-36 нс! Что я сделал. Я разогнал AT до 288 МГц. Проверил на таймере - действительно, это так: таймер TMR2 проходит ровно за 1 секунду 144000 такта. Я в С описал PF10 как выход, а в asm использовал команды для быстрой SET/CLR: ; код установки бита LDR R5, GPIO_DBG_ptr ;; GPIO_DBG_ptr содержит GPIOF_BASE + смещение регистра SCR LDR R5, [R5] ; Грузим адрес GPIOF->SCR MOVS R4, #DBG_SET_BSRR ; R4 <= 1<<10 STR R4, [R5] ; Сохраняем 4 команда ; код сброса бита LDR R5, GPIO_DBG_ptr ; 5 команда LDR R5, [R5] ; Грузим адрес GPIOF->SCR MOVS R4, #DBG_CLR_BSRR ; R4 <= 1<<(10+16) STR R4, [R5] ; Сохраняем 8 команда Код разместил в FLASH, вся программа целиком (включая эти команды) влезла чуть более чем 16 кБ, загружена начиная с 0x08000000, т.е. она 100% попала в область NWS (WS=0). Если просто запустить эти 8 команд, то при помощи осциллографа можно поймать импульс длиной аж в 70 нс! (картинка 2) Идем дальше. Если убрать команды 5-6, то импульс резко сокращается до 7 нс. (картинка 1) Опытным путем выяснил, сколько исполняются каждая из команд: LDR R5, GPIO_DBG_ptr ; 36 нс! (это по сути команда LDR R5, [PC + 60], PC смотрит на Flash NWS (0 WS)) LDR R5, [R5] ; 24 нс! MOVS R4, #DBG_SET_BSRR ; эта и следующая - около 7 нс. STR R4, [R5] ; Получается, что взять значение из периферии дольше, чем туда положить.... Кто-нибудь имеет такой опыт? Может ли подсказать, как нивелировать разницу? Или что я не учёл, когда рассчитывал, что все команды будут исполняться где-то за 1-2-4 такта. А 1 такт это около 3,5 нс.

-

А в чем вопрос?

-

Нет, конечно, это ж бред полный. Одно устройство - один мас. Просто 2 сетки представляют собой зеркало, и мас-адрес устройства N будет одинаковым в обеих сетках. И если мое устройство будет свитчем KSZ, то свитч этого может не понять - мас-адрес устройства N начнет мигрировать у KSZ туда-сюда, между портами. И так будет со всеми мас-адресами всех устройств в двух сетях. Эта нагрузка может гипотетически перегрузить свитч, что может аукнуться в ненужный момент. А сетка должна быть надёжной.