jojo

Свой-

Постов

572 -

Зарегистрирован

-

Посещение

Весь контент jojo

-

>такого, что по цене операции может конкурировать с GPU на тех же разрядностях ? Большие Spartan-6 или средние Virtex-6 успешно конкурируют с GPU. Что лучше - зависит напрямую от алгоритма и реализации. Вы на какие алгоритмы нацелились?

-

VHDL or Verilog

jojo ответил D-Luxe тема в Языки проектирования на ПЛИС (FPGA)

Вот вы разные высокоуровневые SV/VHDL-2008 обсуждаете, скажите, вы ресурсы ПЛИС и градации скорости экономите или с запасом закладываете? Ведь, наверное, нужен запас ресурсов и дополнительная градация скорости на реализацию "несчастливых" участков программы... Тех участков, которые человек может лучше машины сделать. Или вы выискиваете несчастливые конструкции HDL и стараетесь их не применять? Вообще, вы как высокоуровнево пишете на HDL, как-то иначе, чем низкоуровнево? -

xst: сумматоры и LUT6

jojo ответил Victor тема в Среды разработки - обсуждаем САПРы

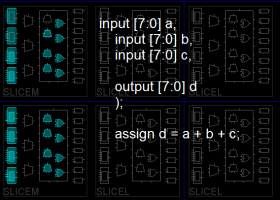

В ISE 12.4 для Virtex-6 и Spartan6 получается LUT с двумя выходами. Настройки по умолчанию, констрейнов нет. А у вас какая версия и какие настройки? -

xst: сумматоры и LUT6

jojo ответил Victor тема в Среды разработки - обсуждаем САПРы

Увы, редактором paintbrush :) -

xst: сумматоры и LUT6

jojo ответил Victor тема в Среды разработки - обсуждаем САПРы

-

Возможно, из-за дрожания тактового сигнала данные сбиваются. Я сейчас больше с Xilinx работаю. По памяти, вроде надо в Timequest провести анализ путей на Fmax, потом построить список путей в отчёте, потом нажать на сбойный путь и сделать Locate in Chip Planner. Там подсветятся ресурсы сбойного пути. Наверное, можно прямее сделать это же. В том же отчёте TimeQuest можно увидеть, из чего складывается задержка. Нажмите на сбойный путь и Locate in Technology Map Viewer. Что-то в документации должно быть на эту тему. Надо либо законстрейнить положение, либо добавить регистры, либо перестроить сбойный путь.

-

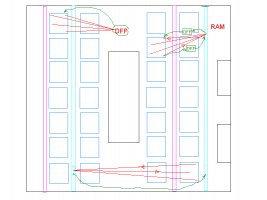

Нужно сопоставлять отчёт анализатора задержек (Timequest др.) и вид проблемного пути на кристалле (FloorPlan Editor и т.п.). Проблемный триггер или блок памяти может быть расположен в "левом" месте на кристалле, вдали от разумного, желаемого положения. Поскольку таких элементов может быть много, их положение можно оптом законстрейнить. Ресурсы ПЛИС расположены немонотонно, например, узкими колонками, простым констрейном размещения дело может не обойтись. В этом случае добавляем в конвейер пустые регистры, которые по алгоритму вроде не нужны, но задержку сокращают. Покажите, если можете, аналогичную картинку своего проекта с подсвечиванием сбойных путей.

-

Да, и частоту в констрейнах можно уменьшить, чтобы понапрасну не ждать. После трассировки для неправильно размещаемых элементов можно задавать (уточнять) области, где им положено быть. Это если элементы в макрос не входят.

-

Можно попробовать Design Space Explorer, или как он сейчас называется в Altera. В Xilinx ISE нарвался на аналогичную проблему: на одних настройках (таблицах) MAP проект в итоге трассируется, на других - нет. Причём при минимальных правках нужно искать новую "счастливую таблицу" из 100*5 возможных. Проблема появилась при большом количестве плотных макросов с размещением (RPM) и большом количестве блоков ОЗУ. Для получения fmax пришлось навтыкать "ненужные" регистры с запасом, хотя при малом тираже макросов доп. регистры не требовались.

-

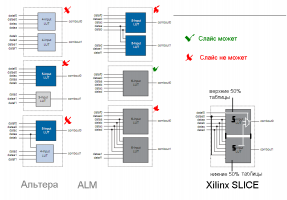

Как SLICE уступает ALM-у в чём-то, сразу картинка неправильная :) 2 независимых LUT4 в LUT с двумя выходами не пакуются? Не пакуются. Я же не сказал, что в SLICE нет памяти. По количеству логических функций SLICE уступает ALM-у. На то я этот огрызок нарисовал. А память - не логическая функция. Ввели в SLICE второй триггер - можно было хоть входы таблиц LUT5 разделить. SLICE с LUT6 ведь позже ALM появился? Содрали, но не до конца.

-

А вроде ALM-то многофунциональнее будет, чем современный SLICE? Stratix III со скидками ещё как-то мог конкурировать с Virtex-5. У Stratix IV была какая-то дикая розничная цена, так что оптовую даже узнавать не хотелось.

-

>Во-первых: с GPU, конечно, спавнивать тяжело. Сейчас GPU часто используют для не графических вычислений, а там ПЛИС бывает лучше, чем GPU. >Сказать, что в таких-то задачах такие-то FPGA выгоднее, чем современные ЦП (надеюсь, что где-то все-таки выгоднее). Выгоднее, даже при большой разнице в частотах. Некоторые классы задач прямо перечислены в http://www.altera.com/literature/manual/cookbook.zip. Я бы ещё добавил генетические задачи http://www.timelogic.com/. Железка простая, а выигрыш в сотни раз.

-

>Например самый младший Virtex6 VLX75T стоит порядка $700 и содержит порядка 4.8 миллиона вентилей (75000 LC). Virtex6 VXL240T стоит порядка $3000 и содержит порядка 15.3 миллиона вентилей (240000 LC). Кстати, Virtex6 VLX240T оптом значительно дешевле, как отмечалось выше на примере Альтеры. При сравнении одинаковых проектов в Quartus и ISE нужно задавать констрейны на размещение (прямоугольники), и эти прямоугольники "зажимать", постепенно уменьшая площадь. Иначе ресурсы в ALM и SLICE не спариваются и смысла такое сравнение архитектур не имеет. >Альтера разрывает в клочья Ксайликс и по загрузке плис, и по скорости работы и по скорости компиляции. Никто никого не разрывает.

-

>Сейчас делаю собственно сопроцессор (фреймворк, в некотором роде). А что такое фреймворк? Просто интересно. Advanced Synthesis Cookbook: A Design Guide for Stratix II, Stratix III, and Stratix IV Devices http://www.altera.com/literature/manual/cookbook.zip

-

>Остается открытым вопрос о производительности FPU при наличии всего одного потока. >Ну вот допустим у нас 10 стадий в конвейере FPU (В альтеровской либе 12 вообще). Это ж будет латентность 10 клоков при любой зависимости. >Но вообще наверное можно попробовать забить на это и действительно сделать на ниосе. У вас получается действительно всего один поток и требуется готовность результата FPU через такт? Задержка готовых FPU бывает от 2...4 до 24...48 тактов. http://www.eecg.toronto.edu/~myrto/gpuarch-ispass2010.pdf

-

>Ну это в идеале наверное, да. Я так далеко не смотрю пока) Я думал, вы Nvidiю хотите побить. У простого мультпроцессора код килобайт на 100 в в верилоге. Если FPU взять из ядер (Xilinx?), своего кода совсем мало будет.

-

>Но вообще чем больше времени я на это трачу тем больше понимаю, что затея не очень удачная. >Собственно я пока-что делаю свой мультипроцессор, но замучался) Подумал, что может лучше поискать на стороне Нормальная, нормальная затея. Будем считать, что чистая производительность синтезируемых в микросхеме FPU вам подходит. Пусть этих FPU 100-200 шт. Оборачиваем каждый FPU триггерами и блоками памяти для подачи данных и снятия результата. Это будет процессор. Считаем, что процессор будет специализированным и что "программу" можно реализовать аппаратно. Соединяем процессоры древовидной или кольцевой шиной, возможно, с переходом на пониженную частоту. Получаем мультипроцессор, что-то вроде GPU. С мультипроцессорами работаем из корневого узла шины Дополнительные компоненты процессора и шины должны быть на уровне 10-20% от ресурсов FPU. Иначе перформанс вряд ли получится впечатляющим.

-

Если контроллер на Virtex-5/6 в контрольной панели Windows отключить, перешить ПЛИС, а потом обратно включить, то контроллер продолжает работать, перезагрузка не нужна. Можно как-то этот процесс автоматизировать, а шить хоть через Impact. >Но это не всегда удобно. К примеру, если основной интерфейс для общения с внешним миром - PCI-express, и прошивки получаем по нему же, то становится интересно. >Заливать прошивку на флэш, а потом перестартовать с неё? >Довольно геморойно, флешку опять же заездить можно быстро. Вместо ПЗУ можно сделать "конфигурационное ОЗУ" параллельно ПЗУ. В это ОЗУ загружается новая прошивка, дёргается PROG, подробности можно домыслить. Это так, просто вариант. >Общаться с PCI-express'ом через дополнительный чип? Можно, но стоит денег и ресурсов. Через вторую ПЛИС и Selectmap нормально получается грузить. >В идеале, хочется чтобы ПЛИСина сама меняла свою конфигурацию, без посторонней помощи. Желательно ещё и по частям >Собственно вопрос: есть ли у Xilinx какие-либо средства для переконфигурации ПЛИС изнутри и/или по частям? Partial Configuration в PlanAhead, лицензия отдельная нужна на это. Есть какой-то tuitorial на эту тему.

-

Xilinx ISE 13.1

jojo ответил vugluskr тема в Работаем с ПЛИС, области применения, выбор

>Как показывет практика, 1-ые версии обычно глючат. Подождем 13.2 или 13.3. Теперь все версии глючат, и первые, и последние. В 12.4 Planahead глючит. -

Рецепт для 95-100% слайсов и максимальных частот. Действуя так, можно добиться впечатляющих 110-120 % :) использования LUT с учётом комбинирования LUT2 и LUT3 в LUT6: Этап 1. Подготовка IP Ограничить пути распространения ~2...4 LUT или ~32 бита при суммировании с переносом. Экспортировать крупные или многочисленные блоки IP в Planahead (сделав для них отдельный проект). Этап 2. Сборка основного проекта Привязать вручную импортированные крупные блоки констрейнами. Для всей остальной логики основного проекта назначить области в Planahead. На всех этапах, по необходимости: Перебрать таблицы Cost в поисках "счастливого номера" при сбалансированной стратегии. Увеличить усилия и включить продвинутые галки Mapper-у. Вручную переставить несколько совсем неудачно расположенных LUT. Все эти действия имеют свою трудоёмкость и последствия, поэтому выжимать максимум из Xilinx - занятие не из приятных.

-

Xilinx инновирует !

jojo ответил maugli тема в Работаем с ПЛИС, области применения, выбор

Я первоисточник. Источник на 20 А не тянет, для LX240T надо 30-40, а лучше 50 А, если планы по получению производительности грандиозные. Может и 50 А получиться, если поднять частоту до 500 МГц и занять всю LX240T. Другой вопрос, как и зачем это делать. -

Xilinx инновирует !

jojo ответил maugli тема в Работаем с ПЛИС, области применения, выбор

Забитый на 90% слайсов Virtex-6 LX240T на частотах 300...400 МГц способен потреблять 30...40 А. Проблема ещё - ISE - беспросветный тормоз. 3D ПЛИС он не потянет. -

Требуется разработчик в проект с Xilinx Virtex-6

jojo опубликовал тема в Предлагаю работу

Основные требования - - знание архитектуры Virtex-5 и Virtex-6, - умение самостоятельно разрабатывать сложные устройства на ПЛИС, - опыт работы с IP Xilinx PCI Express, Ethernet, Microblaze. - ISE, Modelsim, Visual C, - Verilog, C, - английский язык, - спокойный характер. Обязанности - - разработка IP ядер, - разработка интерфейсов, - разработка изделий с ПЛИС Virtex-6. Расположение - Москва, Ленинский проспект. График работы - постоянный. Если есть интерес - прошу прислать личное сообщение. -

>У вас Virtex-6 ES? с этим ES у нас непонятки... очень сильно греется при отсутствии прошивки. У нас ES. А греться вроде он должен, в datasheet ток покоя 2.5 А. Только я думал, что это с прошивкой, а оказалось - и без прошивки даже 2.6 А. iMPACT output from CES Silicon '2': IDCODE is '24250093' (in hex). '2': : Manufacturer's ID = Xilinx xc6vlx240t, Version : 2

-

Это понятно. Один из ответов про синтез нас в сторону увёл. И с нетлистом тоже не имеет, и со временным моделированием и моделированием потребления, я делал. У Xilinx Power Estimator сделан для Virtex-5 и Virtex-6 общий, насколько я могу судить, а реальные данные для модели есть только для Virtex-5 LX330T. Оценка для Virtex-6 выполняется пересчётом. Зато я нашёл dll, в которой упомянуты искомые трассировочные ресурсы. Можно копать дальше.