alex_bface

Участник-

Постов

53 -

Зарегистрирован

-

Посещение

Весь контент alex_bface

-

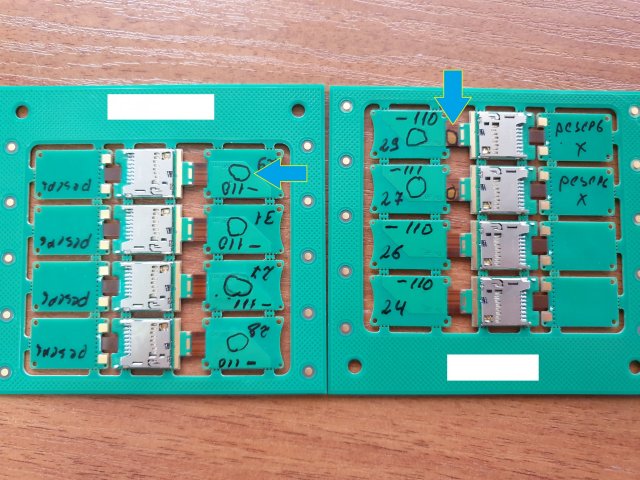

Здравствуйте. Сталкивались с подобной проблемой при прогреве ГЖ платы. См картинку во вложении. При чём расслоения возникали как в гибкой части, отслоение коверлея от адгезива, так и в жёсткой части, расслоение набора no-flow препрегов. Термопрофиль пайки в конвекционной печи безсвинцовый, проверенный на подобных дизайнах многократно. Но с указанной моделью дефект расслоения оказался хорошо повторяем. Платы хранились пару месяцев в заводской упаковке с селикогелем. После просушки плат дефект расслоения после пайки полностью пропал. Сушка: 60-70°С, 2%RH, двое суток. Аналогичный результат эксперимента подтвердил и сам производитель (Фаст принт). стекло-текстолит и полимид проверенные, а вот по адгезиву и nf препрегам завод долго инфу не выдавал. Закрались сомнения, но позже завод сообщил марки материалов. Правда проверить их мы ни как не смогли. Рекламацию завод не принял. После этой ситуации взяли за правило сушить все ГЖ платы перед монтажом вне зависимости от условий хранения. Если в вашем случае дефект появляется даже после просушки плат, то это уже однозначно не ликвидная продукция и нужно настоять на рекламации к производителю плат.

-

GPIO interrupt: Rising & Falling Edge два в одном

alex_bface ответил evgen2 тема в NXP

Тут, действительно, ни чего странного. За время входа в обработчик быстро меняющиеся сигналы успевают устанавить несколько флагов, которые вы проверяете в обработчике. Мы и на stm-ке с этим пролетали )). С текущим контроллером прерываний, быстро меняющиеся сигналы с одного пина не получится регистрировать. Мой коллега извращался, подключая один внешний сигнал на два разных пина МК и устанавливал в разных группах прерываний разные маски условий. Но в итоге, всё равно, схематику переделывали ). -

Спасибо за ответ. Пробовал и "Design -> Make Schematic Library" и "Design -> Make Integrated Library". В библиотеки попадают только компоненты согласно Original Library. Для примера: на картинке ниже показана строка с таким компонентом. Только CC0603_68PF_50V_2%_COG попадает в сгененированные библиотеки. CC0603_43PF_50V_2%_COG теряется совсем. Похоже, придётся просить бомы у трассировщика платы. :(

-

AD 19.1.8 / Varians / Alternate Part

alex_bface опубликовал тема в Altium Designer, DXP, Protel

Ситуация: в проекте два варианта. Часть компонентов по вариантам разделена через механизм Alternate Part (т.е. указаны ссылками на конкретные библиотеки компонентов, но эти библиотеки не входят в состав проекта). При компиляции проекта получаю кучу ошибок, но листы схематики с финальными нетлистами создаются и там можно увидеть правильные параметры компонентов (green italic font) для разных вариантов. Логично предположить, что вся информация по вариантам в проекте присутствует. Но есть проблема: При генерации БОМ файлов для разных вариантов, для компонентов с Alternate Part в бом попадают параметры от компонента Original Library Link, а не параметры, которые видны в схематике для этого компонента в выдранном варианте. Т.е. бом файлы по вариантам генерируются не правильно. Бомы генерирую через Job file, в качестве источника - проект. Пробовал до компиляции и после. Результат не меняется, бомы с ошибками. Вопрос: можно ли не имея всех библиотек проекта получить корректные бомы по вариантам? П.с. Проект прикрепить не могу, нет согласия клиента. Альтиум лицензионный указанной в шапке версии. Есть мнение, что тут получу ответ быстрее, чем на офф форуме. -

ого ажиотаж! Если у ТС устройство - светодиодка шир.потреб, то всё решат деньги. Прототип однослойной платы (условно, 1 кв.дм. 1,5мм толщиной) на аллюм. основании выйдет порядка 50-150$. Прототип однослойной платы на медном основании 500$+. При массовом заказе ценник тоже не приблизится к аллюминию. И получается, что добавить при трассировке горсть smd перемычек (и втулить всю схему в один слой платы) и использовать аллюминий выйдет в разы дешевле однослойки на медном основании. Любые варианты электрически связать сигнальный слой платы и медное основание технологически сложны в реализации и из за этого ценник становится совсем не адекватный. Различные варианты подобных стеков мы прорабатывали не однократно на разных заводах (Китай, Тайвань, Италия, Германия - это в порядке увеличения ценников). Основные технологические проблемы с которыми мы столкнулись: 1. твёрдости меди основания и диэлектрика сильно разные и при механической сверловке мелких диаметров уже не получается подобрать приемлемый режим сверления пакета да и сами свёрла. С диаметрами 2+мм уже можно работать, но кому нужны такие переходные? 2. лазером через T-preg, практически, ни кто работать не хочет. Т.е. с фабричным ламинатом с медным основанием уже проблемы, а прессовать сигнальный слой меди на основание через препрег для микровиасов - уже очень больно по цене, да и теплопроводность такого диэлектрика некудышная (дай бог 0,3Вт/м*°). В итоге жизнь увидели только два варианта: 2-слойка приклеенная на медное основание через coolspan от rogers и двухслойка припаянная через паяльную пасту на отдельно фрезерованное основание (вариант по-дешевле, но гемороище при пайке не реальное). Это всё была СВЧ электроника для спец-техники (т.е. бюджеты были). Короче, для коммерческой электроники идея утопическая, но если бюджет проекта позволяет, то варианты есть.

-

IPC стандарты это ценный материал. Но вот самая свежая ревизия IPC-7525B Stencil Design Guidelines аж от 2011 года, что как бы намекает, что тематика не особо актуальна и стандартизация тут не особо востребована. И это потому, что как бы трассировщик платы не старался задизайнить слой пасты, реальные файлы для изготовления трафарета 100% будут переделываться и пересчитываться инженером/технологом монтажного производства. Так зачем трассировщику напрасно тратить на это время? В этом вопросе почти все технологи монтажных производств с которыми я общался склоняются ко мнению, что лучше получить слой пасты 1в1 с SMD площадками платы, чем перелопачивать "типа подготовленный" слой пасты. Но если вы и трассировщик и технолог монтажного производства в одном лице, то изучить указанный выше стандарт всё же придётся.

-

Производителя не порекомендую, но чисто для себя хочу поинтересоваться. Такой массивный клеммник должен будет держаться только на тоненьком диэлектрике несущем проводники. По вопросу технологии: дешманкие фабричные материалы типа HRA-51xx или CCAF-01 тут не применишь, а значить только отдельно фрезеровка алюм. основания и отдельно тонкая плата и потом прессование. А значить хорошо оснащённые производства, а значить дорого (( Сами давно ищем что-то подобное для светодиодной тематики, но пока всё сильно за рамками бюджета. Так то тема интересная буду следить.

-

Забавный и редкий глюк. Лично с таким сталкивался только раз, когда проверял дизайн коллеги в котором он применил компоненты из ранее импортированного пикадовкого .pcb файла. Глюк обнаружил случайно, когда для файла проекта перестала вызываться панель PCBList. Ошибку выловили до заказа платы. Повезло )).

-

Говорите 10 лет цена на платы у Фп держится... Хм, наши менеджеры работают с ФП каждый день и жалуются, что за 5 лет цены на ФП выросли на 30-40% за одни и те же дизайны. И это по фобу, без таможки и транспортных. Только в хорошей серии можно рассчитывать на цены пятилетней давности. Если у вас есть на примете проверенный завод, с ценами и возможностями ФП десятилетней давности в том же регионе Китая - буду признателен за контакты.

-

to _4afc_ Спасибо, интересные проводочки. Жаль на пробу кусочек не нашёл где купить. А сразу бухту заказывать чисто для попробовать пока жаба душит.

-

Последний ремонт плат приходилось делать с применением МГТФ 0,03мм2 это самый тонкий из выпускаемых. Петли такого провода на плате крепили отрезками полимидной самоклеящейся ленты. Такое добро можно найти в любом магазине, торгующем эл.компонентами. Гуглится по словам kapton film adhesive. Очень тонкая, но прочная плёнка. Проверяли паяльным феном с температурой 150°С - не плавится и не отклеивается. Обычно обмотки трансформаторов такой лентой фиксируют. Стоит не дорого, 1-2 у.е. за рулончик нужной ширины. Попробуйте, может для ваших целей подойдёт.

-

BGA0.4 9x9

alex_bface ответил Electrophile тема в Работаем с трассировкой

to Aner Не передёргивайте, пожалуйста. Я не зря упомянул ответственную технику. С заводом по вашей ссылке я не сотрудничал, но в разделе сайта Сертификаты и стандарты почему-то только IPC – A600H класс 2. А в перечне возможностей производства: мин.отв - 0,1мм мин.поясок - 0,1мм мин.проводник на внутреннем слое - 75мкм. И как с такими параметрами топологии трассировать bga корпус с шагом выводов 0,4мм через сквозные виасы? И как быть с третьим классом IPC? Допускаю, что на сайте перечень устаревших тех-возможностей и этот завоз сделает сквозные переходные для платы под корпус из темы топика, но по какому классу? А захотите надёжную плату (IPC class3) - пожалуйста в HDI стек с соответствующим ценником. Если устройство не ответственного назначения и какая-то массовость есть, то можно и сквозные 0,25/0,1мм закладывать и радоваться как здорово отделались от HDI стеков. -

BGA0.4 9x9

alex_bface ответил Electrophile тема в Работаем с трассировкой

Стрёмно, конечно, но такие "переходные отверстия" делают. Например Тайваньский завод (http://www.speedy-circuits.com.tw/capabilities_technical.html). Делают механикой виасы pad0,25mm/hole0.1mm. При этом, со слов, менеджера на такие виасы требования IPC стандартов не распространяются, а виасы 0,15мм делают только по второму классу надёжности. Получается, что в ответственной технике такие корпуса лучше вообще не применять :( А так, то фанауты растягиваются через виа 0,25/0,1мм и проводники/зазоры 0,05/0,05мм на внутренних слоях, т.е. как на картинке выше. -

BGA0.4 9x9

alex_bface ответил Electrophile тема в Работаем с трассировкой

Здравствуйте. По таким корпусам есть хороший гайд от Латтиса. Гуглится по фразе "lattice pcb layout recommendation for bga packages" pdf на 5МБ. И для WLCSP 81 там, даже, 2 варианта фанаутов есть. Только не освещается вопрос с классом надёжности по IPC. Лично я, имея выбор, всегда выберу лазерные микро-отверстия, чем сквозные с дырками 0,1-0,15мм. Но лучше искать гайд именно от производителя м/с, он будет оптимальным. Вопрос цены плат под такие корпуса, действительно, стоит остро и запутанно. Мне в этом году приходилось уже дважды перетрассировать платы под "человеческие корпуса" после того как фин.менеджер охреневал от цены платы под bga корпуса c шагом 0,4мм. Правильно пишут, что на форуме решить вопрос оптимизации цены вы не сможете. Нужно теребить вопросами ваших предполагаемых подрядчиков/поставщиков. Я лично был свидетелем, когда 8-слойка с двумя последовательными парами лазерных микро-отверстий (staggered) обошлась дешевле, чем таких же габаритов 8-слойка но со сквозными переходными pad0,30mm/hole0,15mm +via filled&capped (оба варианта с доставкой в Украину). -

Буквально в январе этого года столкнулся с подобной проблемой. 3 платы из серии в 2000 шт. оказались с КЗ в самих платах. Платы делал фастпринт, в отчётах выходного электроконтроля - всё ок, но вот после монтажа - одна цепь питания на землю коротит. Снимал последовательно все компоненты (более 30 штук) и все с металлическими корпусами над проводниками. КЗ не ушло :) По совету бывалого прожёг эти цепи 5В с ограничением по току 3А. Как результат на одной плате выявил кз в области переходного, ещё на одной - обуглилась большая область. Третью не насиловал. Начальство скомандовало распаивать платы на компоненты, а сами доски в мусор. В вашем случае если не получается удобно высверлить переходные в цепях с кз и пробросить проводок, то лучше всего компоненты на новую плату пересадить.

-

Закрывать паяльной маской облуженный проводник (именно облуженный, а не оставленный металлорезист) - лишено всякого практического смыслы. Нужно пропустить больше тока через проводник - увеличивайте сечение. Упёрлись в производственные или ситуационные ограничения - напаивайте медную шинку. Эти велосипеды уже изобретены. Если и этого не достаточно - скорее всего архитектурный просчёт. Про экзотику вроде фабричных медных шин расписывать не стану. Россия/Украина против неё деньгами голосуют.

-

Это как минимум. И это уже не мало. Так же при компиляции схемы получаете предсказуемые имена цепей в каждом канале (заметно удобнее станет сочинять design rules). Самое ценное, на мой взгляд, в канальном дизайне - это именно одиночное представление дублирующегося элемента (канала) в схеме. В случае изменений в схемотехнике (а они возникают в большинстве проектов, даже, в ходе трассировки), не придётся вносить изменения ручками в каждый канал. Всё это сэкономит часы, если не дни, вашей работы. Если бы не печальный опыт с почти десятком итераций изменений схематики в "не канальном" дизайне и потеря двух дополнительных недель рабочего времени, то я бы и сам до сих пор каналы не юзал.

-

1) Если изначально создать канальную схематику не судьба, то только через компонентс линкс. Эта операция заполнит поле Unique id свойств компонентов соответствующими схематике значениями и при обновлении компоненты уже не будут удаляться. 2) В схематике кроме копипаста нужно будет сделать ещё несколько кликов. Выделяем скопированные компоненты -> F11(SCH inspector) -> нажимаем на строку "Component Designator" -> нажимаем на "...", откроется диалог смарт эдит -> в закладке Formula введите !+'_1' -> жмакаете ОК, в десигнаторы выделенных компонентов будет дописано "_1". Аналогично для остальных "каналов". В следуюший раз попробуйте "канальную" схематику. Откроете для себя неожиданные плюшки при трассировке ;).

-

Номер последнего компонента

alex_bface ответил jenya7 тема в Altium Designer, DXP, Protel

В менюшке Reports жмакаете Bill of materials и в поле Grouped columns перетаскиваете Designator. В основной части окна (где список компонентов) жмакаете на колонку Designator и сортировка покажет вам последний поз.номер в нужной группе компонентов. Сам бом-файл при этом можно не сохранять и просто закрыть диалоговое окно. Так мой товарищ схему дополнял. Быстрее пути пока не нашёл. -

Здравствуйте. В сфере проектирования, изготовления и монтажа плат (Украина) работаю уже 13-й год и за всё это время через мой компьютер прошли сотни трафаретов. Но мне так и не довелось повстречать на столько автоматизированный инструмент, как того хочет ТС. Большинство моих знакомых проектировщиков плат слабо ориентируются в особенностях монтажных производств, а многие из них не всегда сами могут выбирать целевое монтажное производство. Соответственно и качественное проектирование трафарета (а часто и групповой заготовки платы) проектировщик выполнить не в состоянии. И это не его вина, это последствие разделения труда/специализаций. Большинство моих коллег (в том числе инженеров-технологов монтажных производств) склоняются ко мнению, что подготовка трафарета, это забота инженерного отдела монтажного производства. В редких случаях, когда проектировщик организовывает и контролирует весь цикл производства изделия, проектирование и заказ трафарета входит в его обязанности. Обычно вместе с герберами платы я готовлю гербера паяльной пасты без заужения/расшивки апертур. Финальный файл трафарета готовит человек с монтажного производства. В редких случаях я готовлю финальные файлы трафарета сам, т.к. хорошо знаком с оборудованием и процессом монтажа, но всегда остаётся вероятность не учесть каких-то особенностей монтажного производства и выслушивать потом их претензии или бороться с последствиями "кривого" монтажа. На монтажных производствах ребята работают в основном в CAM350, некоторые в Gerbtool/Camtastic2000. Про редактор от LPKF слышали, пробовали, но единственное его преимущество - проверка aspect/area ratio в слоях паяльной пасты. Это оказывается не достаточной причиной для переучивания на другой гербер-редактор. К сожалению, не знаю в каких редакторах работают крупные PCBA компании, но есть подозрение, что в автоматическом режиме там трафареты не готовят. В Украине все PCBA маленькие, ну кроме филиала Jabil в Закарпатье, но от туда у меня инсайда нет.

-

Если вопросы теплоотвода и паразитных параметров такого перехода модуль-материнка остро не стоят и длины периметра хватает, то я рекомендую вариант с полу-отверстиями. Преимуществ перед LGA вагон: прощает больше ошибок хранения и монтажа; удобство визуального контроля и эл.тестирования; даёт возможность получить простую и дешёвую материнскую плату; выбрать материал основания модуля проще. Вообще, переход к LGA выводам в корпусах модулей исторически был вынужденной мерой, безысходностью. Т.к. через залитые припоем полуотверстия ни вч сигнал не передашь, ни тепла много не сбросишь.

-

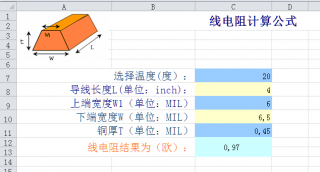

Если я правильно понял, весь кусок длины проводника проходит по внутреннему слою. И если на этом слое медь толщиной пол оза, то измеренное сопротивление вполне соответствует расчётному значению. На картинке результат калькулятора сопротивления от ФастПринта. Подписи ячеек на китайском, но увы, что есть. Этому калькулятору доверяю, т.к. расчётные значения подтверждались измерениями как на сигнальных проводниках, так и на "обмотках"спирального трансформатора. Расхождения были не более 10%. А вот для наружных слоёв, даже при пол озовой стартовой меди, сопротивление проводника указанной длины и ширины должно составлять не более 350 мОм. Нулевые показания вашего измерителя, уверен, связаны лишь с низкой точностью измерения.

-

, мой вам совет - ни когда не меняйте в списке слоёв тип с nc на graphic. Формирование композитов, это не единственная проблема с которой вы столкнётесь в таком случае. По вашему вопросу: Если вы хотите сделать композит из слоёв графики и сверловки, нужно сначала преобразовать нужные слои сверловки в слои графики. Это можно сделать перейдя в режим NC (закладка окна редактора) далее Utilities -> NC data to gerber и создаёте новые гербер-слои из слоёв сверловки. Далее возвращаетесь с САМ режим (закладка окна редактора) и составляете нужный композит Tables -> composites (указываете нужным слоям нужные полярности). Далее можно получившийся композит экспортировать или преобразовать в новый гербер-слой командой Utilities -> composite to gerber и работать с ним как с обычным слоем графики. Ваша ошибка была в изменении типа NC в списке слоёв.

-

Такой футпринт производитель рекомендует потому, что он позволит достигнуть желаемого результата с наименьшими ограничениями к производителю плат и монтажному производству. Микрочиповскому футпринту будет не важно работает ли завод с параметром solder mask registration 25мкм или 75мкм, посадочное место не пострадает и все краевые выводы компонента будут запаяны одинаково и AOI на монтажном производстве не отправит спаянные платы на доработку. В варианте EvilWrecker-а не видно слоя паяльной маски, но если от маски открывается весь сложный пад в форме расчёски, то рассчитать дозировку паяльной пасты будет заметно сложнее и флуктуации кол-ва нанесённой пасты чаще будут вызывать дефекты монтажа. В вашем варианте, где на группу краевых и внутренних падов один прямоугольный полигон, пады на плате будут определяться только паяльной маской. Как следствие, высокие требования к производителю плат и никакая ремонтопригодность такого посадочного места. Но если вы заранее настраиваетесь на хороший (=дорогой) PCB-fab и хорошее, современное (=дорогое) монтажное производство, то оба предложенных варианта хороши. А у EvilWrecker-а площадки ещё и выглядят красиво.

-

Я соглашусь с Viko. ВЧ токи потребления нагрузки будут замыкаться через конденсатор. Через катушку и виас пойдёт микроскопическая их доля, слишком высокий импеданс этого контура. Площадь петли замыкания ВЧ тока на обех картинках, практически одинакова и разницу заметить не удастся. А вот для НЧ токов в нагрузке правый вариант будет хуже на активное сопротивление кусочка проводника. На глаз это будет около 1мм, т.е. активное сопротивление порядка 2мОм. Даже при токе потребления через эту цепь питания, скажем, 200мА разница в падении напряжения будет порядка 0,4мВ. Я, даже, хз чем это в реальной плате можно будет измерить. Но опыт товарища Uree я не могу игнорировать. По этому прошу пояснить его позицию. Может я чего-то не понимаю.