BSACPLD

Свой-

Постов

912 -

Зарегистрирован

-

Посещение

-

Победитель дней

5

Весь контент BSACPLD

-

Схема на CycloneII

BSACPLD ответил torik тема в Работаем с ПЛИС, области применения, выбор

Позвольте с Вами немного не согласится, цитата из config_handbook.pdf (стр. 700, таблица 4-21, примечание 1): Existing batches of EPCS4 manufactured on 0.15 μm process geometry supports AS configuration up to 40 MHz. However, batches of EPCS4 manufactured on 0.18 μm process geometry support only up to 20 MHz. EPCS16 and EPCS64 serial configuration devices are not affected. For information about product traceability and transition date to differentiate between 0.15 μm process geometry and 0.18 μm process geometry EPCS4 serial configuration devices, refer to PCN 0514 Manufacturing Changes on EPCS Family process change notification on the Altera website at www.altera.com. Хотя M25P40, конечно же, дешевле. -

Вопрос по Verilog

BSACPLD ответил BSACPLD тема в Языки проектирования на ПЛИС (FPGA)

Спасибо - разобрался. Это в примере регистры. А так я планировал подключить несколько одинаковых периферийных модулей (порты (регистры), SPI, UART). -

Вопрос по Verilog

BSACPLD опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Собственно говоря, вопрос: Есть код на AlteraHDL, который я решил попробовать переписать на Verilog. ... VARIABLE PORT[3..0] : lpm_ff WITH ( LPM_FFTYPE = "DFF", LPM_TYPE = "LPM_FF", LPM_WIDTH = 8 ); ... BEGIN PORTA[] = PORT[0].q[]; PORTB[] = PORT[1].q[]; PORTC[] = PORT[2].q[]; PORTD[] = PORT[3].q[]; PORT[0].enable = IOW[0]; PORT[1].enable = IOW[1]; PORT[2].enable = IOW[32]; PORT[3].enable = IOW[33]; PORT[].clock = clock; PORT[].data[] = data_d[]; ... END; Предполагаю, что необходимо писать что-то вроде такой конструкции: lpm_ff #( .lpm_fftype ("DFF"), .lpm_type ("LPM_FF"), .lpm_width (8) ) PORT [3:0] ( // А вот как теперь правильно подключить все сигналы? ); Как наиболее правильно подключить сигналы в данном массиве из мегафункций? -

Дело в том, что у EPM очень резкие фронты. Линия не согласована, следовательно, от входа идет отраженная волна, которая и сбивает отладку. Варианта два. Первый - установка резисторов 22-120 Ом, которые будут гасить отраженную волну. Второй - установить режим пониженного быстродействия, тем самым загрубив фронты. misyachniy! У Вас что-то не то с главной страницей сайта - посмотрите скриншоты.

-

74AHC (VHC) - 5V->3V 74AHCT (VHCT) - 3V->5V Еще есть микросхемы "1 вентиль в одном корпусе" 74VHC1GT125, 74AHC1G125. Их можно купить в Митраконе и Терраэлектронике. 74AHC есть в ЭФО.

-

ATmega168 FLASH + EEPROM + FUSE При 1 МГц время программирования 5-6 с. При 20 МГц время программирования 2-3 с.

-

С Linux никогда не работал, поэтому вряд ли. Необходимо будет переписать весь интерфейс с WINAPI на что-то, что понятно Линуксу. Хотя ведь в Линуксе вроде бы есть эмулятор WIN32? Или я ошибаюсь? Сам лично не собираюсь переходить на Линукс по идейным соображениям. Предпочитаю Windows 2000 и XP, 98 и Vista Must Die! Если нужно могу скинуть исходники на почту.

-

Здравствуйте! Хочу, так сказать, предложить общественности свой вариант USB-программатора: http://www.mcu-cpld.narod.ru/ATprog2232.html Проблема "курицы и яйца" решена за счет применения микросхемы FT2232C (D). В общем, если будут какие-то проблемы, вопросы, пожелания - пишите, постараюсь помочь. С уважением, Сергей.

-

Кабель на 100 или 110 Ом - соответственно терминирующие резисторы на входе 100 или 110 Ом. Я использовал 0805, точность 5%. Расстояние от микросхемы до согласующего резистора < 2,54 см. В Cyclone III уже есть встроенные резисторы для согласования по выходу, правда, не во всех банках. Если нет встроенных резисторов в нужном банке, то ставится согласующая цепь из 3 резисторов. Схема и расчет есть в datasheet. Более подробно о стандарте LVDS можно почитать в документации фирмы National. Вместо гибкого шлейфа еще можно использовать кабель CAT5. LVDS.rar

-

1. По поводу нескольких метров все в порядке. Я на Cyclone II (EP2C8T144C6N) передавал сигналы со скоростью до 400 Мб/с на расстояние до 2,5 м. Передача велась по гибкому шлейфу (два земляных провода - LVDS пара - два земляных провода, и т. д.). Естественно полное согласование по входу и по выходу. 2. LVDS можно использовать лишь как электрический стандарт, а протокольную часть сделать самостоятельно (например, старт-бит, данные, стоп-бит). Для alt_lvds_rx опорный тактовый сигнал обязателен. 3. Сделайте две пары (по гибкому шлейфу, разъемы IDC-10) и не мучайтесь. С уважением, Сергей.

-

Читайте тему с начала. Программа I8I16.exe используется для конвертирования HEX файлов в файлы для инициализации памяти процессора. Путь к данному файлу необходимо указать в параметре INIT_PROGRAM. I8I16.rar

-

Немного обновленный вариант. Добавлен интерфейс к FT245BM. test_cpu_v2.rar

-

Можно еще попробовать такой вариант: http://murid0.narod.ru/math/sqrt8.htm

-

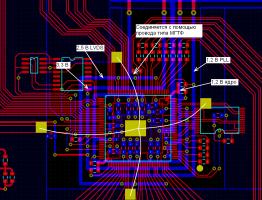

brumal! Вот файл с разводкой питания под EP2C8T144. 1.rar

-

1) Да, размер 0805. 2) МГТФ - земля, под 45' тоже земля.

-

Можно попробовать развести питание как на прилагаемом рисунке. У меня эта разводка работает на 200 МГц.

-

Добавил команды MUL, MULS, SLEEP. Также добавлен захват прерываний, т.е. если сигнал прерывания исчез до того как прерывания были разрешены, то прерывание все равно будет обработано. Флаг прерывания нужно сбрасывать записью лог. 1 в EINT_IF. Поздравляю всех с Новым Годом! :santa2: test_cpu.rar

-

Обнаружил ошибки при выполнении команд типа ld YL, X+. Исправленный файл прилагается. control_cpu.rar

-

Спасибо за ссылки! :a14:

-

Cyclone потому, что этот процессор делался для проекта на Cyclone. К тому же у Альтеры несколько выше быстродействие, в проекте для которого создавался процессор весь упор был на быстродействие логики (генератор синхроимпульсов), а не процессора. Что Вы понимаете под подмножеством AVR? Если Вы имеете ввиду, что он совместим по системе команд, то да. Данный процессор, скорее даже не AVR, а совместимый по командам с AVR, у него своя собственная периферия и несколько отличная организация памяти. РОН и РВВ не отображаются на область ОЗУ. Сейчас процессор поддерживает не все команды (см. cpu.txt), если можно будет настроить компилятор соответствующим образом, то можно использовать и "C". AHDL потому, что Verilog я сейчас только изучаю, а AHDL пользуюсь уже давно. Кстати, а Вы не можете мне посоветовать какую-нибудь толковую книжку по Verilog?

-

Без Квартуса залить не получиться, потому, что память программ организована как ROM. Если сделать логику заливки, то можно будет заливать и после конфигурации. Данный вариант не окончательный, он является лишь частью двух больших проектов. Я заливаю следующим образом: 1) I8I16.exe 2) Update Memory Initialization File 3) Assembler 4) JTAG

-

Если есть хороший инет, можно скачать по ссылке: ftp://ftp.altera.com/outgoing/release/61_dvd_windows.iso

-

rar подойдет? test_cpu_qar.rar

-

AVR CPU Core

BSACPLD опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Здравствуйте! В свое время искал AVR корку, но ничего подходящего не смог найти. В результате был создан данный проект, которым и хочу поделиться. В проекте создан CPU с SPI (master), GPIO, интерфейсом к DataFlash и линиями внешних прерываний. Тестовая программа реализует обмен по Ethernet через ENC28J60 (ARP, Ping и частично UDP). Из особенностей CPU: Программируемые адреса прерываний. Уменьшенное время выполнения некоторых команд. Список поддерживаемых команд находится в файле cpu.txt. Файлы: test_cpu.qar - проект с CPU. test_avr - тестовая программа I8I16.exe - конвертер файлов из Intel HEX в HEX для инициализации памяти в Quartus. С уважением, BSACPLD. test_cpu.rar -

По поводу AT91SAM7S64. Если поставить нужные VID и PID и сделать так, чтобы микросхема со стороны компьютера виделась как FTDI, то точно должно работать. А чем не нравится FT245BM? У FT245R вообще минимум обвески, так, что должно получится очень компактно. AS и не должен работать, я делал только JTAG и PS. У меня есть оригинальный Altera USB-Blaster Rev.C, как только будет время попробую снять лог работы с помощью BusHound.