BSACPLD

Свой-

Постов

863 -

Зарегистрирован

-

Посещение

-

Победитель дней

3

Весь контент BSACPLD

-

А ID чипа Artix-7 не проверяет?

-

В списке её нет. Но в моей плате реализован механизм удалённой перепрошивки через Ethernet. Главное чтобы с конфигурированием проблем не было.

-

W25Q64JVSSIQ и Artix-7

BSACPLD опубликовал тема в Работаем с ПЛИС, области применения, выбор

Коллеги, подскажите, пожалуйста, подойдёт ли W25Q64JVSSIQ для конфигурирования Artix-7? Может я слона в упор не вижу, но я перерыл весь datasheet и не нашёл конкретных значений ID code... UPD. Точно я не выспался... 16h 4017h -

Вставлю свои 5 копеек. Сейчас доступно: 1. Gowin как уже было выше сказано. Для задач с выскоми тактовыми частотами они не подходят. Проект что у меня на Xilinx спокойно собирается на 150 МГц, в Gowin едва ли вытягивает 60-70 МГц. 2. Fudan Частичный клон Xilinx. Не совместимы по распиновке с оригинальными Xilinx. Но зато частично совместимы с Vivado. Есть и своя собственная среда разработки. Все было бы хорошо, если бы не адово количество брака в поставке. В партиях 2021/2022 года брак 1%. В партии 2023 года брак 30%. В партии 2024 года брак 59%. Важно отметить, что схемотехника/топология в части ПЛИС/питания не менялись - это одно и то же изделие с минимальными модификациями в части заменить разъём, обновить Ethernet чип на новую ревизию. Брак проявляется в виде некорректной загрузки прошивки при отрицательных температурах (сам Fudan -40...+85 согласно datasheet). ПЛИС банально не проходит верификацию загруженной прошивки. 3. PangoMicro pin-to-pin с Xilinx, но среда разработки полностью своя. Отладочные платы доступны на AliExpress. Чипы пока едут. По частотам на 10-20% выше Xilinx/Fudan. 4. Б/У Xilinx после реболлинга. Доступны на AliExpress по вменяемой цене, но нужно брать у проверенного продавца чтобы не нарваться на совсем уж трэш. Также отдельные варианты доступны в Чип и Дип по не адекватной цене 10x от номинала.

-

Это очень жирно 🙂 Я уже сделал свои функции и устройство уже в серии. Тему можно закрывать.

-

Немного оффтоп, но у того же человека есть весьма неплохие корки для AXI: https://github.com/alexforencich/verilog-axi https://github.com/alexforencich/verilog-axis Использую их вместо корок от Xilinx - проект легко переносится хоть на PangoMicro, хоть на любого другого производителя. Тоже рекомендую к использованию.

-

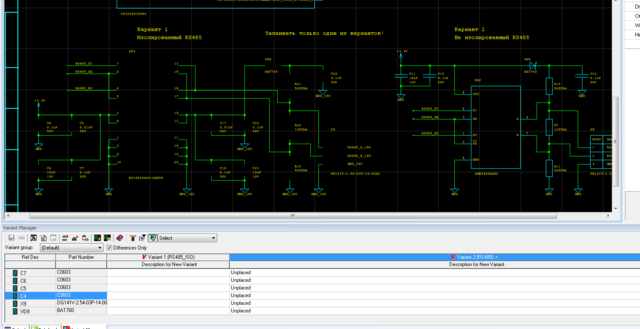

Коллеги, решил я тут попробовать Variants чтобы не прописывать руками что паять, а что нет. С генерацией BOM вопросов нет. Есть вопросы по схеме. Как сделать чтобы не используемые компоненты были зачеркнутые, а не просто становились невидимым? Версия EEVX2.7.

-

Чип слишком маленький чтобы туда сразу и Ethernet и PCIe пихать. Один только AXI Memory Mapped To PCI Express занимает 11911 LUT и 16 BRAM.

-

А если быть совсем точным, то не реально. Специалистов универсалов с глубокими знаниями хотя бы по 3 направлениям найти практически не реально - все уже давно пристроены. И ценник на таких специалистов начинается от 400К. И каждый такой специалист ооочень специфичен в общении, т.к. знает себе цену.

-

Китайские ПЛИС

BSACPLD ответил МАСТЕР LO тема в Работаем с ПЛИС, области применения, выбор

Причем тут маркировка? Они все по datasheet -40 обеспечивают. Брак чипов - замена сколько есть со склада и возврат денег за остальные. Новую партию сами заказали напрямую из Китая. -

А чем Вас готовый и отлаженный модуль не устраивает? Вот, например: https://github.com/alexforencich/verilog-i2c Сам я не любитель использовать чужой код, но этот модуль написан на мой взгляд весьма неплохо. Использую его уже третий год в своих проектах - пока никаких проблем не было. Да и документирован он довольно неплохо.

-

Решил я проблему с зависанием при выполнении кода из ОЗУ. Было: while(FLASH->STATR & SR_BSY); FLASH->CTLR &= ~CR_PAGE_PG; Стало: while(FLASH->STATR & SR_BSY); for (uint8_t i=0 ; i<10 ; i++) __asm__("nop"); FLASH->CTLR &= ~CR_PAGE_PG; Как я и предполагал, между сбросом флага SR_BSY и записью в FLASH->CTLR должна быть некоторая задержка.

-

Это Вы не понимаете, что ВЕСЬ код в 2КБ ОЗУ физически не помещается. Я уже писал Вам об этом.

-

0x08003FC0 Все define скопированы из SPL ch32v00x_flash.c как есть, я ничего не менял. Я просто скопировал к себе код из фирменной ch32v00x_flash.c добавив в свой flash.h атрибуты для размещения в RAM, и добавил к названиям функций RAM_* чтобы они не перекликались с функциями из фирменной библиотеки. К тому же судя по коду фирменных функций FLASH_BANK1_END_ADDRESS нигде не используется.

-

Я скопировал код из библиотеки SPL 1 в 1. Там только флаг SR_BSY проверяется. void RAM_FLASH_Unlock_Fast (void) { /* Authorize the FPEC of Bank1 Access */ FLASH->KEYR = FLASH_KEY1; FLASH->KEYR = FLASH_KEY2; /* Fast program mode unlock */ FLASH->MODEKEYR = FLASH_KEY1; FLASH->MODEKEYR = FLASH_KEY2; } void RAM_FLASH_ErasePage_Fast (uint32_t Page_Address) { if((Page_Address >= ValidAddrStart) && (Page_Address < ValidAddrEnd)) { FLASH->CTLR |= CR_PAGE_ER; FLASH->ADDR = Page_Address; FLASH->CTLR |= CR_STRT_Set; while(FLASH->STATR & SR_BSY) ; FLASH->CTLR &= ~CR_PAGE_ER; } } void RAM_FLASH_BufReset (void) { FLASH->CTLR |= CR_PAGE_PG; FLASH->CTLR |= CR_BUF_RST; while(FLASH->STATR & SR_BSY) ; FLASH->CTLR &= ~CR_PAGE_PG; } void RAM_FLASH_BufLoad (uint32_t Address, uint32_t Data0) { if((Address >= ValidAddrStart) && (Address < ValidAddrEnd)) { FLASH->CTLR |= CR_PAGE_PG; *(__IO uint32_t *)(Address) = Data0; FLASH->CTLR |= CR_BUF_LOAD; while(FLASH->STATR & SR_BSY) ; FLASH->CTLR &= ~CR_PAGE_PG; } } void RAM_FLASH_ProgramPage_Fast (uint32_t Page_Address) { if((Page_Address >= ValidAddrStart) && (Page_Address < ValidAddrEnd)) { FLASH->CTLR |= CR_PAGE_PG; FLASH->ADDR = Page_Address; FLASH->CTLR |= CR_STRT_Set; while(FLASH->STATR & SR_BSY) ; FLASH->CTLR &= ~CR_PAGE_PG; } } void RAM_FLASH_Lock_Fast (void) { FLASH->CTLR |= CR_LOCK_Set; } Может быть стоит добавить задержку перед первой проверкой флага в while? Помню с PIC18 был прикол с UART, что там флаги статуса не сразу менялись и приходилось вставлять nop перед первым опросом флага. Может быть здесь такая же проблема?...

-

Но это не объясняет, почему контроллер зависает - в тесте я программирую последнюю не используемую страницу FLASH, т.е. не затираю ни одного байта полезного кода. Кроме того он виснет на этапе RAM_FLASH_ProgramPage_Fast -> RAM_FLASH_Lock_Fast. И конечно же вопрос как заставить MRS не использовать функции из FLASH в функциях выполняемых из RAM.

-

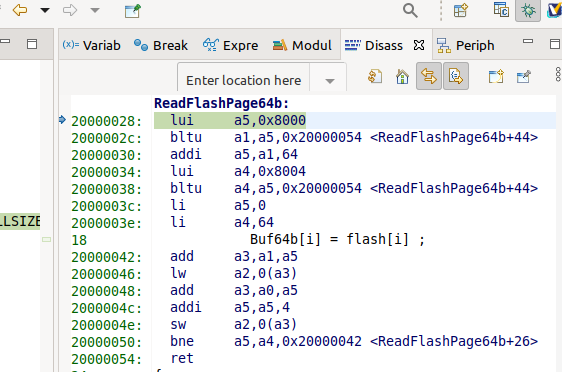

У меня ничего подобного не наблюдается: WriteFlashPage64b: 2000014a: jalr t0,160(zero) # 0x0 <_start> 138 RAM_FLASH_Unlock_Fast () ; 2000014e: addi sp,sp,-4 20000150: mv s0,a1 20000152: mv s1,a0 20000154: jal 0x20000028 <RAM_FLASH_Unlock_Fast> 140 RAM_FLASH_ErasePage_Fast (Page_Address) ; 20000156: mv a0,s0 20000158: jal 0x20000046 <RAM_FLASH_ErasePage_Fast> 142 RAM_FLASH_BufReset () ; 2000015a: jal 0x2000007c <RAM_FLASH_BufReset> 143 for (uint8_t i=0 ; i<(FLASH_PAGESIZE/4) ; i++) 2000015c: li a5,0 145 RAM_FLASH_BufLoad (Page_Address+4*i, Buf64b[i]) ; 2000015e: add a4,s1,a5 20000162: lw a1,0(a4) 20000164: add a0,s0,a5 20000168: sw a5,0(sp) 2000016a: jal 0x200000a4 <RAM_FLASH_BufLoad> 2000016c: lw a5,0(sp) 2000016e: li a4,64 20000172: addi a5,a5,4 20000174: bne a5,a4,0x2000015e <WriteFlashPage64b+20> 148 RAM_FLASH_ProgramPage_Fast (Page_Address) ; 20000178: mv a0,s0 2000017a: jal 0x200000da <RAM_FLASH_ProgramPage_Fast> 150 RAM_FLASH_Lock_Fast () ; 2000017c: jal 0x2000010e <RAM_FLASH_Lock_Fast> 2000017e: addi sp,sp,4 20000180: jr 170(zero) # 0x0 <_start> RAM_FLASH_ErasePage_Fast: 20000046: lui a5,0xf8000 2000004a: add a5,a5,a0 2000004c: lui a4,0x4 2000004e: bgeu a5,a4,0x2000007a <RAM_FLASH_ErasePage_Fast+52> 20000052: lui a5,0x40022 20000056: lw a4,16(a5) 20000058: lui a3,0x20 2000005c: or a4,a4,a3 2000005e: sw a4,16(a5) 20000060: sw a0,20(a5) 20000062: lw a4,16(a5) 20000064: ori a4,a4,64 20000068: sw a4,16(a5) 2000006a: lw a4,12(a5) 2000006c: andi a4,a4,1 2000006e: bnez a4,0x2000006a <RAM_FLASH_ErasePage_Fast+36> 20000070: lw a4,16(a5) 20000072: lui a3,0xfffe0 20000074: addi a3,a3,-1 20000076: and a4,a4,a3 20000078: sw a4,16(a5) 2000007a: ret RAM_FLASH_BufReset: 2000007c: lui a5,0x40022 20000080: lw a4,16(a5) 20000082: lui a3,0x10 20000084: or a4,a4,a3 20000086: sw a4,16(a5) 20000088: lw a4,16(a5) 2000008a: lui a3,0x80 2000008e: or a4,a4,a3 20000090: sw a4,16(a5) 20000092: lw a4,12(a5) 20000094: andi a4,a4,1 20000096: bnez a4,0x20000092 <RAM_FLASH_BufReset+22> 20000098: lw a4,16(a5) 2000009a: lui a3,0xffff0 2000009c: addi a3,a3,-1 2000009e: and a4,a4,a3 200000a0: sw a4,16(a5) 200000a2: ret RAM_FLASH_BufLoad: 200000a4: lui a5,0xf8000 200000a8: add a5,a5,a0 200000aa: lui a4,0x4 200000ac: bgeu a5,a4,0x200000d8 <RAM_FLASH_BufLoad+52> 200000b0: lui a5,0x40022 200000b4: lw a4,16(a5) 200000b6: lui a3,0x10 200000b8: or a4,a4,a3 200000ba: sw a4,16(a5) 96 *(__IO uint32_t *)(Address) = Data0; 200000bc: sw a1,0(a0) 97 FLASH->CTLR |= CR_BUF_LOAD; 200000be: lw a4,16(a5) 200000c0: lui a3,0x40 200000c4: or a4,a4,a3 200000c6: sw a4,16(a5) 99 ; 200000c8: lw a4,12(a5) 200000ca: andi a4,a4,1 200000cc: bnez a4,0x200000c8 <RAM_FLASH_BufLoad+36> 100 FLASH->CTLR &= ~CR_PAGE_PG; 200000ce: lw a4,16(a5) 200000d0: lui a3,0xffff0 200000d2: addi a3,a3,-1 200000d4: and a4,a4,a3 200000d6: sw a4,16(a5) 200000d8: ret 106 if((Page_Address >= ValidAddrStart) && (Page_Address < ValidAddrEnd)) RAM_FLASH_ProgramPage_Fast: 200000da: lui a5,0xf8000 200000de: add a5,a5,a0 200000e0: lui a4,0x4 200000e2: bgeu a5,a4,0x2000010c <RAM_FLASH_ProgramPage_Fast+50> 108 FLASH->CTLR |= CR_PAGE_PG; 200000e6: lui a5,0x40022 200000ea: lw a4,16(a5) 200000ec: lui a3,0x10 200000ee: or a4,a4,a3 200000f0: sw a4,16(a5) 109 FLASH->ADDR = Page_Address; 200000f2: sw a0,20(a5) 110 FLASH->CTLR |= CR_STRT_Set; 200000f4: lw a4,16(a5) 200000f6: ori a4,a4,64 200000fa: sw a4,16(a5) 112 ; 200000fc: lw a4,12(a5) 200000fe: andi a4,a4,1 20000100: bnez a4,0x200000fc <RAM_FLASH_ProgramPage_Fast+34> 100 FLASH->CTLR &= ~CR_PAGE_PG; 20000102: lw a4,16(a5) 20000104: lui a3,0xffff0 20000106: addi a3,a3,-1 20000108: and a4,a4,a3 2000010a: sw a4,16(a5) 2000010c: ret 119 FLASH->CTLR |= CR_LOCK_Set; RAM_FLASH_Lock_Fast: 2000010e: lui a4,0x40022 20000112: lw a5,16(a4) 20000114: ori a5,a5,128 20000118: sw a5,16(a4) 2000011a: ret

-

Чтение вызывается только два раза. В начале программы чтобы прочитать последнюю страницу в которую я сохраняю пользовательские настройки. И второй раз по команде с UART. Полностью слинковать программу в RAM нет возможности - она туда не поместится. У CH32V003 всего 2КБ RAM. Из окошек при отладке открыт только дизассемблер и исходник.

-

Проверил. Внутри функции записи FLASH все команды в RAM. Если поставить точку останова перед вызовом функции и пройтись по шагам, ничего не зависает. Если поставить точки останова перед вызовом функции и сразу после выхода из функции, то до первой точки программа доходит, затем я снова запускаю Run и контроллер виснет. После этого я попробовал добавить задержку после каждой команды обращения к регистрам FLASH - контроллер завис и перестал прошиваться, пришлось менять контроллер - он вообще перестал отвечать по SWIO.

-

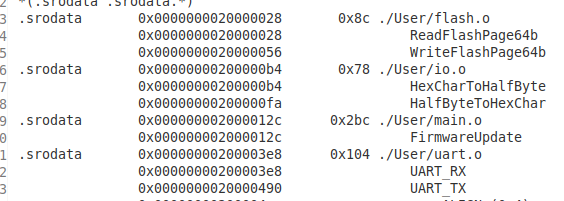

Все функции выполняемые из RAM объявлены подобным образом: void ReadFlashPage64b (uint32_t* Buf64b, uint32_t Page_Address) __attribute__((section(".srodata"))) __attribute__((used)) ; void WriteFlashPage64b (uint32_t* Buf64b, uint32_t Page_Address) __attribute__((section(".srodata"))) __attribute__((used)) ; Кроме того и map и пошаговая отладка в дизассемблере показывают адреса RAM. Вот, я даже специально сейчас вынес функции для работы с FLASH в отдельный файл. Выполняю из FLASH - работает нормально и штатно и в пошаговой отладке. Выполняю из RAM - штатно виснет, а в пошаговой отладке работает. flash.c flash.h

-

Штатный сброс только один - перезагрузка всей системы по питанию. У МК предельно простая задача - подавать питание на комп после прогрева системы, а также опрос датчиков. Этот функционал уже отлажен и работает, обновление прошивки как дополнительная необязательная опция. В части перезаливки FLASH - да. UART через DMA. Перед перезаливкой FLASH отключаю все прерывания.

-

Полностью - я по шагам прошелся, смотрел, что адреса везде из RAM. Код без прерываний - только поллинг в while.

-

Всем привет! У меня возникла необходимость реализовать удалённое обновление прошивки для CH32V003. Из-за особенностей устройства его нельзя ресетить перед началом обновления прошивки - устройство помимо своих основных функций в добавок управляет питанием компа, который им управляет (холодный старт, включает комп только после прогрева > 5 градусов). Если сбросить МК, питание с компа будет снято. Казалось бы можно загнать цикл и функции для обновления прошивки в RAM и шить оттуда. Раньше на STM32 я так и делал - шил из RAM и уже потом давал сброс чтобы перезапустить всю систему. Но с CH32V003 возникла проблема - если код выполняется из FLASH, запись страницы FLASH памяти проходит успешно (пробовал перезаписывать самую последнюю неиспользуемую страницу), но если выполнить тот же самый код из RAM, контроллер вешается намертво. А если выполнять этот код из RAM, но в пошаговой отладке, ничего не зависает - подозреваю, что дело в каких-то времянках. Также я попробовал разместить цикл и функции для обновления прошивки в System FLASH - если попытаться перейти в функцию обновления прошивки из основного кода, это вызывает HardFault. Можно ли как-то решить проблему с зависанием записи FLASH при выполнении кода из RAM, либо выполнять функции размещённые в System FLASH вызывая их из основного кода? Или может быть как-то можно перейти к выполнению кода из System FLASH не сбрасывая контроллер?

-

На фиксированный формат вида "%d.%d" ничего сложного. У меня только в одном месте требуется ввод - задание порогов срабатывания термодатчика по UART. На вывод ещё проще - вся телеметрия в формате "%s%d\r\n" либо "%s%x\r\n". Других форматов ввода/вывода не предполагается - устройство максимально простое и тупое. Главное код как можно более компактный, чтобы ещё влезло сохранение настроек во FLASH и удалённое обновление прошивки.

-

Да я уже написал свой sscanf, sprintf уже в процессе 🙂