BSACPLD

Свой-

Постов

912 -

Зарегистрирован

-

Посещение

-

Победитель дней

5

Весь контент BSACPLD

-

Попробовал забить MAC сетевой карты вместо multicast - тоже самое. Wireshark пакеты видит, карта не реагирует. Пробовал на 2 разных компах.

-

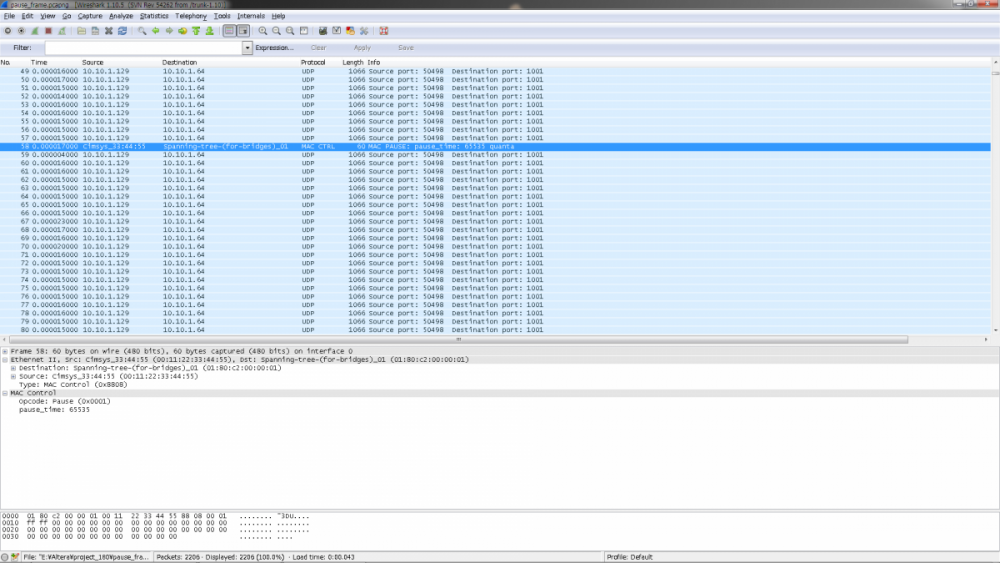

Я его уже 10 раз проверял и по размеру и по содержимому :( Вообще, насколько я понимаю, если приходит pause с multicast адресом 0180C2000001, то порт должен приостанавливать любую передачу. Вот лог wireshark. https://yadi.sk/d/4L1NBbEF27b-QA И где ff? Если Вы про pause, то 0xFFFF это максимальная длительность паузы равная 33 мс.

-

Читал. Биты 11 и 10 в регистре 4 установлены в 1.

-

Совпадает.

-

Для UDP точно правильные, т.к. эти пакеты я отсылаю с помощью своей тестовой программы и wireshark показывает правильные значения + это уже давно проверенный кусок кода + приёмную часть я не правил. Со стороны передачи pause frame вроде тоже все верно. dst 0180C2000001 - специальный MAC адрес для pause пакетов src 001122334455 - MAC адрес платы wireshark показывает что паузы нет - см. скриншот в первом посте. Да. Именно этого я и пытаюсь добиться.

-

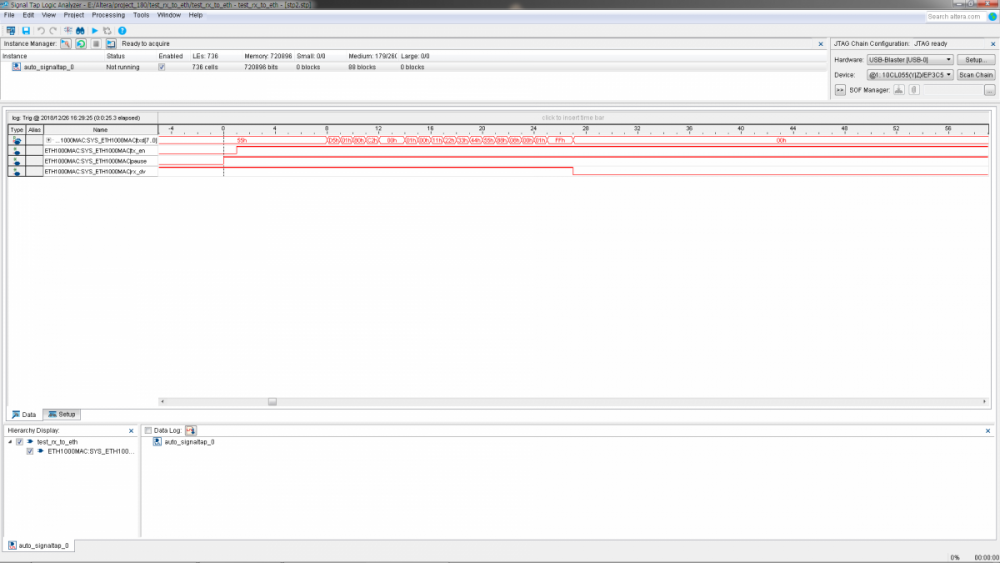

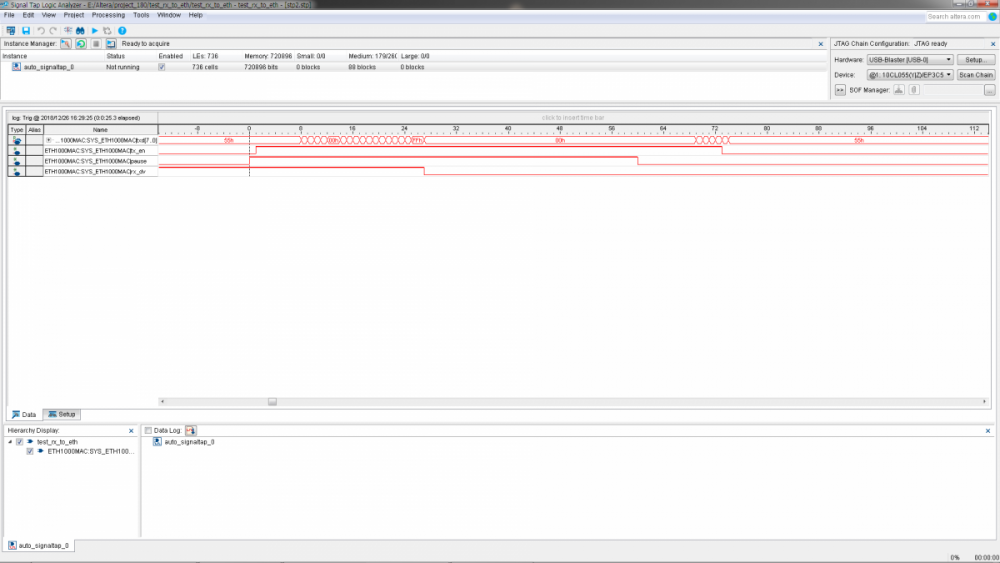

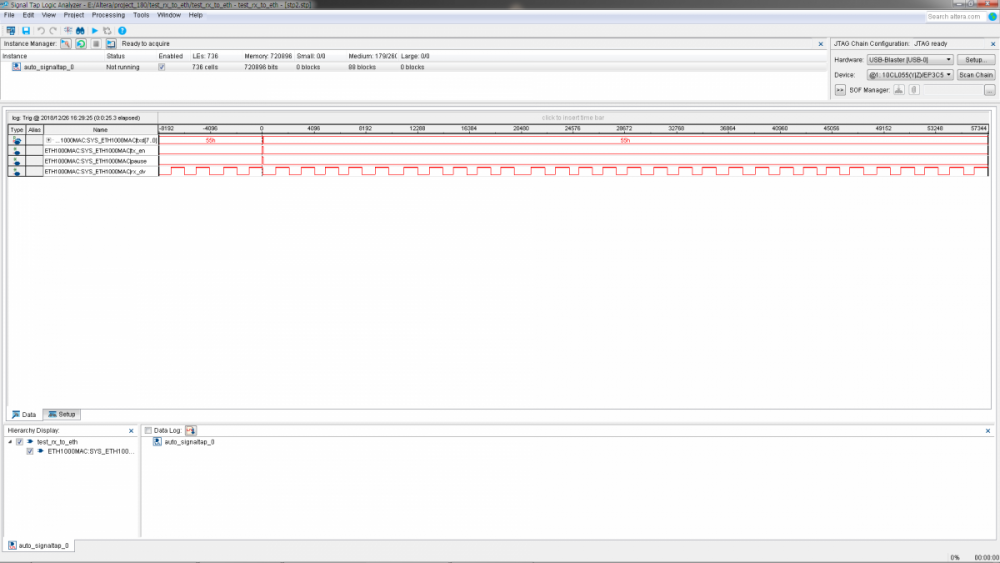

Это не служебные, т.к. по длине они совпадают с UDP потоком данных от ПК (8 байт преамбула + 1066 байт пакет + 4 байта CRC). Таймаут не мог так быстро закончится, т.к. он выставлен на 33 мс (0xFFFF). В SignalTap видно, что пакеты идут с интервалом чуть больше 1000 тактов 125МГц, а это явно меньше 33 мс.

-

FPGA+MAC+PHY pause frame

BSACPLD опубликовал тема в Работаем с ПЛИС, области применения, выбор

Добрый день, коллеги! Помогите, пожалуйста, разобраться в чем проблема. Есть самописный Ethernet MAC в который я решил добавить поддержку Flow Control. Алгоритм работы следующий: При заполнении приёмного FIFO более чем на половину MAC контроллер отсылает pause frame в сторону ПК. После отсылки pause frame MAC ждет таймаут равный pause time после чего снова проверяет заполнение приёмного FIFO. Со стороны ПК pause frame нормально ловится Wireshark и вроде бы никакой ругани на неправильный формат Wireshark не выдает. Со стороны ПЛИС смотрю наличие принимаемых пакетов с помощью SignalTap (на скриншоте флаг rx_dv). В настройках сетевой карты Flow Control включен, однако при приходе pause frame не происходит приостановки передачи пакетов на 33 мс (pause time = 0xFFFF). -

Месячная зарплата помноженная на количество месяцев которое потребуется на разгребание всего этого безобразия. Уровень ЗП зависит от Вашего опыта и определяется на собеседовании. Если Вам не нужно ничего объяснять это одно, а если нужно учить отличать резистор от конденсатора, то это другое. По конкретным цифрам я ничего сказать не могу, т.к. уровень ЗП определяет руководство НИИ. Пока не будет разобран склад, мы не будем нагружать человека задачами по закупке и работой с поставщиками. Но нужно понимать, что время это не бесконечно. Думаю, 6-8 месяцев вполне достаточно чтобы все это разобрать. Мы не проходим таможню, т.к. работаем только с российскими фирмами. Прохождение таможни это головная боль поставщика. Единственное исключение это работа напрямую с Белорусскими предприятиями, но подробностей я не знаю, т.к. занимаюсь разработкой, а не закупкой. Знаю только что отдел закупок очень не любит работать с Белорусскими предприятиями напрямую.

-

UP. Вакансия еще актуальна.

-

Кладовщик/снабженец НИИРЭТ МГТУ им. Н.Э. Баумана (Москва)

BSACPLD опубликовал тема в Предлагаю работу

Коллеги, нам требуется кладовщик/снабженец для выполнения следующих задач (в порядке приоритета): На текущий момент: 1. Привести в порядок бардак склад оставшийся от расформирования одного из отделов. 2. Привести в порядок бардак склад всего НИИ. 3. Вести учет компонентов на складе. 4. Поддержка в актуальном состоянии кассы с рассыпухой 0603, 0805 и т.д. По мере необходимости формировать заявки на закупку/пополнение закончившихся позиций. 5. Сбор комплектации для отправки плат на монтаж в соответствии со спецификацией от разработчика. В будущем, когда будет налажена работа по предыдущим пунктам: 6. Отработка заявок на закупку компонентов. 7. Налаживание контактов с поставщиками. Если какого-то компонента нет в известных нам фирмах, это не значит, что его нельзя купить. Это значит что нужно найти фирму которая нам его поставит. Опыт работы приветствуется, но можно и без него. Главное голова на плечах и умение общаться с совершенно различными типами людей. Отличать резистор от конденсатора и транзистор от микросхемы мы научим :) Зарплата очень сильно зависит от уровня знаний и умений кандидата, поэтому это вопрос для обсуждения на собеседовании. Оформление в соответствии с ТК. Рабочий график 5/2, 8 часов. Время прихода на работу обсуждается. Работа в Москве. Свои резюме и организационные вопросы просьба присылать на почту: bsa-one(собака)yandex.ru или bsa(собака)bmstu.ru -

Нашел в чем была проблема :) Нужно было поставить галочку Debugger->Download->Use flash loader(s). Странно, что GD32 являющийся полным аналогом нормально шился и без этой настроки...

-

Коллеги, помогите, пожалуйста, понять в чем грабли. Есть платы с STM32F103CBT6 и GD32F103CBT6. Если шить любую из этих плат через фирменный ST-Link с помощью IAR, то проблем нет. Если через китайский клон jlink v8.00, то, при попытке зашить STM32F103CBT6, почему-то включается Read-out protection. Если через этот же jlink прошить GD32F103CBT6 той же самой прошивкой, что и STM32F103CBT6, то проблем нет. Точнее почти нет, т.к. один раз Read-out protection все же почему-то включилась. Очень похоже, что jlink почему-то стирает Option bytes у STM32F103CBT6 и не стирает у GD32F103CBT6. И это очень странно, т.к. эти контроллеры отличаются только тактовой частотой и ресурсом flash, а в остальном они полностью одинаковы.

-

Проблема решена. Была ошибка в цикле из которого вызывалась FLASH_ErasePage.

-

Добрый день, Коллеги! Помогите, пожалуйста, понять где грабли. Пытаюсь стереть сектор(страницу) памяти через FLASH_ErasePage, но она почему-то не стирается. Последовательность следующая: FLASH_Unlock () ; перед началом работы бутлоадера FLASH_ErasePage (address) ; где address - физический адрес страницы FLASH_Lock () ; после завершения работы бутлоадера Пробовал перед стиранием страницы вызывать FLASH_ClearFlag, увеличивать таймауты на запись/стирание в коде библиотеки, но ничего не помогло. При этом если выполнить FLASH_EraseAllPages, то она отрабатывает корректно, но мне нужно стирать именно конкретную страницу, а не всю FLASH. В качестве библиотеки использую SPL 3.5.0 от ST.

-

Инженер-технолог НИИРЭТ МГТУ им. Н.Э. Баумана (Дмитров)

BSACPLD опубликовал тема в Предлагаю работу

Уважаемые коллеги! В НИИРЭТ МГТУ им. Н.Э. Баумана требуется инженер-технолог по монтажу печатных плат. Обязанности: - Проверять файлы печатных плат разработчиков/заказчиков на этапе их запуска в производство и при необходимости внесения изменений информировать разработчика/заказчика; - Расчет стоимости монтажа печатных плат (при выпонении внешних заказов); - Обеспечение подготовки производства; - Поиск и внедрение в производство новых технологий; - Разработка технических требований к комплектующим и материалам; - Расчет и контроль норм расхода комплектующих и материалов; - Контроль качества комплектующих и материалов и готовой продукции; - Запуск изделий электронной техники в серию, подготовка опытных партий и опытных образцов; - Подготовка трафаретов; - Выводной и поверхностный монтаж печатных плат (в том числе нестандартных); - Ремонт печатных плат. - Отвечать на электронную почту в течении 1 суток после поступления письма. Требования: - Высшее техническое образование; - Знание способов и методов монтажа сложных блоков, узлов, модулей; - Знание технологии пайки радиокомпонентов поверхностного и навесного монтажа; - Умение паять BGA, QFN, LGA; - Знание критериев контроля качества паяных соединений; - Общие знания современной элементной базы, владение технологией отмывки электронных узлов; - Личные качества: аккуратность, ответственность, обучаемость; - Особые требования: прямые руки, умение думать головой, хорошая письменная грамотность, доброжелательность, умение общаться; - Знание ЕСКД, умение работать с технической документацией; - Умение работы c офисными и CAD приложениями (Microsoft Office, CAM350); - Минимальный рабочий стаж по специальности: 5 лет; - Опыт работы на госпредприятиях приветствуется; - Знание английского (чтение технической документации); - Гражданство РФ. Условия: - Уровень оплаты от 60 000 р. в зависимости от уровня квалификации; - Оформление в соответствии с ТК; - Рабочий график 5/2, 8 часов. Начало в 9:00, но можно скорректировать в небольших пределах; - Работа в Дмитрове (загородная база) недалеко от платформы 75 км (56.429463, 37.488787). Свои резюме и организационные вопросы просьба присылать на почту нашему руководству: min-st-1986(собака)mail.ru Технические вопросы и вопросы по взаимодействию разработчиков и производства просьба присылать мне: bsa-one(собака)yandex.ru или bsa(собака)bmstu.ru -

HPS+DMA+Linux

BSACPLD опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Пытаюсь организовать общую память между FPGA и HPS. Сделал мост fpga2sdram и простейший DMA со стороны FPGA. Тестирование провожу следующим образом: 1. Выделяю в Linux приложении буфер uint32_t размером 1024 элемента (с выравниванием по страницам) и заполняю его тестовыми значениями. 2. Получаю физический адрес буфера и передаю его в DMA контроллер. 3. Запускаю DMA на копирование данных из HPS SDRAM в FPGA. 4. Смотрю считываемые данные со стороны FPGA с помощью SignalTap. Если зарустить DMA сразу после заполнения буфера, то в FPGA копируется мусор, если подождать несколько миллисекунд, то корректные данные. Есть предположение что при заполнении буфера данные сначала хранятся в кэше процессора и лишь затем сбрасываются в SDRAM. Каким образом я могу заставить процессор протолкнуть буфер из кэша в SDRAM или как выделить некэшируемый буфер? -

Заработало :) Я сам себе злобный буратино :) Копировал preloader не в тот раздел sd карты. Остался только вопрос почему linux пишет сразу во все gpio хотя я прописал linux,default-trigger = "heartbeat"; только для GPIO53.

-

Пробовал через loanio. Такой вариант вообще не работает. Пробовал на GPIO54, 55, 56. Т.е. сам linux стартует, но переключать пины настроенные как loanio не получается (на oe подавал 1, out выводил на кнопки). Причем если GPIO54 настроить как gpio, то он начинает работать. 55 и 56 не удалось заставить работать ни как gpio, ни как loanio. Подозреваю, что дело в некорректной настройке pinmux в preloader. Пробовал собирать preloader как в 15.1, так и в 18.0. Результат один и тот же. u-boot также пересобирал. Где-то читал, что вроде начиная с 13.1 loanio и gpio окончательно поломали. Так ли это? Во всяком случае очень похоже, т.к. при чтении регистров GENERALIO7 (GPIO55, 0xFFD0849C) и GENERALIO8 (GPIO56, 0xFFD084A0) для варианта gpio возвращается 1, хотя согласно документации там должен быть 0. При этом для GENERALIO6 (GPIO54, 0xFFD08498), который работает, как и положено, возвращается 0.

-

Написал программу для тестирования GPIO. dts переделал так чтобы система моргала только GPIO53 (linux,default-trigger = "heartbeat"). Остальными GPIO управляет моя программа. #include <stdio.h> #include <stdlib.h> #include <stdint.h> #include <fcntl.h> #include <sys/types.h> #include <sys/mman.h> #include <unistd.h> #include <errno.h> int main() { int fd = 0; void *fpga_leds = 0; void *hps_leds = 0; try { fd = open( "/dev/mem", O_RDWR | O_SYNC ); if(fd < 0) throw "mem open error"; printf("fpga_leds\n"); fpga_leds = (mmap(0, (16/4), PROT_READ | PROT_WRITE, MAP_SHARED, fd, 0xFF203000)); if(fpga_leds == MAP_FAILED) throw "fpga_leds mmap error"; for(int i=0 ; i<(16/4) ; i++) { uint32_t a = *(((uint32_t*)fpga_leds) + i); printf("0x%08X\n", a); } *(((uint32_t*)fpga_leds) + 0) = 0x0000000F; usleep(1000000); *(((uint32_t*)fpga_leds) + 0) = 0x00000000; usleep(1000000); *(((uint32_t*)fpga_leds) + 0) = 0x0000000A; usleep(500000); *(((uint32_t*)fpga_leds) + 0) = 0x00000005; usleep(500000); *(((uint32_t*)fpga_leds) + 0) = 0x0000000A; usleep(500000); *(((uint32_t*)fpga_leds) + 0) = 0x00000005; usleep(500000); *(((uint32_t*)fpga_leds) + 0) = 0x0000000F; printf("\n"); usleep(1000000); printf("hps_leds\n"); hps_leds = (mmap(0, (120/4), PROT_READ | PROT_WRITE, MAP_SHARED, fd, 0xFF709000)); if(hps_leds == MAP_FAILED) throw "hps_leds mmap error"; for(int i=0 ; i<(120/4) ; i++) { uint32_t a = *(((uint32_t*)hps_leds) + i); printf("0x%08X\n", a); } for(int i=0 ; i<32 ; i++) { *(((uint32_t*)hps_leds) + 0) = 1 << i; usleep(500000); } *(((uint32_t*)fpga_leds) + 0) = 0x00000000; *(((uint32_t*)hps_leds) + 0) = 0xFFFFFFFF; usleep(500000); printf("\n"); } catch(const char* msg) { printf("\n%s\n", msg); } if(fd != 0) close(fd); return 0; } GPIO со стороны FPGA отображенные в память процессора работают нормально, а вот со стороны HPS удается зажечь только первые 2 из 4. И ещё странный эффект. После того как я записываю 1 в GPIO54 он должен непрерывно гореть, но он сбрасывается после того как система моргнет GPIO53. P.S. Описание регистров и их адреса я брал вот отсюда: https://www.intel.com/content/www/us/en/programmable/hps/cyclone-v/hps.html#topic/sfo1410069909712.html#sfo1410069909712

-

Очередные грабли. Пересобрал preloader и u-boot. Подправил dts и сделал из него dtb. Закинул все это дело на SD карту, но проект заработал не так как я ожидал. GPIO53, 54, 55, 56 настроены как GPIO. I2C0 отключен. Светодиоды прописаны следующим образом: Для HPS. leds { compatible = "gpio-leds"; hps0 { label = "hps_led0"; gpios = <0x33 0x18 0x0>; linux,default-trigger = "heartbeat"; }; hps1 { label = "hps_led1"; gpios = <0x33 0x19 0x0>; linux,default-trigger = "heartbeat"; }; hps2 { label = "hps_led2"; gpios = <0x33 0x1a 0x0>; linux,default-trigger = "heartbeat"; }; hps3 { label = "hps_led3"; gpios = <0x33 0x1b 0x0>; linux,default-trigger = "heartbeat"; }; }; Для FPGA. leds { compatible = "gpio-leds"; fpga0 { label = "fpga_led0"; gpios = <0x31 0x0 0x0>; linux,default-trigger = "heartbeat"; }; fpga1 { label = "fpga_led1"; gpios = <0x31 0x1 0x0>; linux,default-trigger = "heartbeat"; }; fpga2 { label = "fpga_led2"; gpios = <0x31 0x2 0x0>; linux,default-trigger = "heartbeat"; }; fpga3 { label = "fpga_led3"; gpios = <0x31 0x3 0x0>; linux,default-trigger = "heartbeat"; }; }; По идее все светодиоды должны моргать одновременно, но: 1) 2 и 3 светодиоды на HPS вообще не моргают. Причем это именно те GPIO на которые в изначальном проекте был выведен I2C0. Я его отключил, но они все равно не работают. 2) Светодиоды на HPS и FPGA переключаются по очереди. Что я делаю не так?

-

UPD. Нашел в чем была проблема с переназначением светодиода на уже имеющийся GPIO. В u-boot.scr неправильно указал имя файла.

-

А если система в QSYS не менялась и есть свободный GPIO, достаточно просто пересобрать dtb? Просто я пробовал вообще убрать светодиод из dts чтобы его отключить, но даже с пересобранным dtb он продолжил моргать.

-

Есть отладочная плата с Altera SoC у которой светодиод, задействованный в linux (моргает при загрузке/работе HPS), выведен на GPIO53. Хочу вывести его на другой GPIO. Подскажите, пожалуйста, как его правильно переназначить. Пробовал вручную править dts, а затем собирать его в dtb, но это не сработало.

-

Может временный глюк форума? Сейчас проверил, все скачивается.

-

Китайские ПЛИС

BSACPLD ответил irinamiros тема в Среды разработки - обсуждаем САПРы

Мы у них пытались не платы купить, а самые большие чипы семейства Arora. Причем не одну штуку, а наладить контакт для постоянной закупки их чипов для всех наших проектов. Результат как я написал выше :(