BSACPLD

Свой-

Постов

922 -

Зарегистрирован

-

Посещение

-

Победитель дней

5

Весь контент BSACPLD

-

В пределах такта 200МГц, т.е. 5нс = 4 шага.

-

Блин. Слона то я и не приметил... У них на DevKit speed grade 2 запаян. Похоже придется изобретать свой SERDES на связке логика + ODDR с тактированием от 400МГц... Хотя я так однажды уже делал для Arria GX... Непосредственно 800МГц мне не нужно. Мне нужно подстраивать фазу выходного сигнала с шагом 1.25нс.

-

Питание 1.8В. HR Клок заведен как дифф. пара на GCLK.

-

У меня здесь немного другая проблема. SERDES работает на выход и используется для грубой подстройки фазы выходного сигнала. Точную подстройку я делаю через ODELAY. Проблема с Pulse Width именно со стороны выскочастотного клока заходящего на SERDES. Именно на него ругается Timing Analyzer. Клоки для SERDES: IBUFDS #( .DQS_BIAS("FALSE") // (FALSE, TRUE) ) ibufds_clk_800MHz ( .I (clk_800MHz_p), .IB (clk_800MHz_n), .O (clk_800MHz) ) ; BUFGCE_DIV #( .BUFGCE_DIVIDE (4), .IS_CE_INVERTED (1'b0), .IS_CLR_INVERTED (1'b0), .IS_I_INVERTED (1'b0) ) bufg_clk_sys ( .I (clk_800MHz), .CE (1'b1), .CLR (1'b0), .O (clk_sys) ) ; BUFGCE_DIV #( .BUFGCE_DIVIDE (1), .IS_CE_INVERTED (1'b0), .IS_CLR_INVERTED (1'b0), .IS_I_INVERTED (1'b0) ) bufg_clk_io ( .I (clk_800MHz), .CE (1'b1), .CLR (1'b0), .O (clk_io) ) ;

-

Я здесь пытаюсь использовать OSERDESE3. Он может работать 4x или 8x.

-

Немного странно, т.к. даже на Cyclone IV я без проблем получал 800МГц без всяких ухищрений. А здесь намного более шустрый чип. Под динамической подстройкой Вы имели ввиду фазовые соотношения между низкочастотным и высокочастотным клоком?

-

Kintex UltraScale SERDES

BSACPLD опубликовал тема в Работаем с ПЛИС, области применения, выбор

Коллеги, пытаюсь запустить SERDES на 800МГц, но никак не могу победить разваливающиеся времянки. Тактирование SERDES сделал от внешнего клока. И выскочастотный и низкочастотный клоки получаю посредством примитивов BUFGCE_DIV. В документации Xilinx вроде именно так и рекомендуют делать. Частоты вроде небольшие, но чтобы я ни пробовал писать в констрейнах, все время получаю ругань на Pulse Width. Прошу совета у товарицей имеющих опыт запуска этих SERDES на подобные или более высокие частоты. -

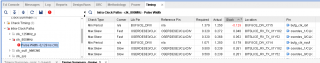

Стр. 36 табл. 33. ds892_kintex_ultrascale_data_sheet.pdf

-

В datasheet написано от 200 до 800МГц. Я могу завести туда и 200 и 400 и 800, поэтому и возник вопрос о том, какое значение лучше выставить.

-

Kintex UltraScale ODELAY3

BSACPLD опубликовал тема в Работаем с ПЛИС, области применения, выбор

Коллеги, подскажите, пожалуйста, исходя из каких соображений нужно выбирать опорную частоту для ODELAY3? Просто чтобы была кратна системной частоте или есть какие-либо нюансы? -

Спасибо. Буду разбираться :)

-

Т.е. просто выбрать полином с наиболее длинным периодом повторения ПСП и этого будет достаточно? Можно хотя бы пару примеров специализированной литературы?

-

Поиск полинома. Допустим я хочу сделать скремблер длиной 23 бита. Вопрос какой полином для него взять.

-

Аддитивный скремблер на ПЛИС

BSACPLD опубликовал тема в Работаем с ПЛИС, области применения, выбор

Добрый вечер, коллеги! Подскажите, пожалуйста, что лучше почитать про синтез полиномов для аддитивного скремблера. -

Assigments->Assigment Editor->в Assigment Name выбираем Virtual Pin и назначаем для него сигналы, в поле value ставим on.

-

Пины для моделирования нужно назначать как Virtual Pin, тогда Quartus их подключать не будет. Не в обиду Вам будет сказано, но за не подключенные пины нужно бить по рукам. Собственно Quartus это и сделал.

-

Решил наконец проблему :) Дело было в буфере. Пока сделал следующим образом: 1. Клок завел в виде дифф. сигнала без всякого буфера на 24 и 25 пины указав там LVDS и подав смещение VCCIO/2 через резисторный делитель (у меня там AC coupling). Правда при этом пришлось немного обмануть Quartus указав питание для данного банка 2.5В, но это не так страшно, т.к. плата все равно будет переделываться. 2. Буфер для данных распаял на макетке и соединил соплями с нужными падами на плате. Сопли конечно получились порядка 1.5см, но вроде работает. Для макетного варианта сойдет.

-

Перерезал дорожку от буфера к ПЛИС. Вход данных соплей закоротил на соседний пин (там статический сигнал). Ситуация улучшилась, но иногда все равно происходит срыв захвата ФАПЧ.

-

Да. Указывал. Никак не ругается. PLL запитана от отдельного LDO. На каждый пин стоит пара 0,1мкФ и 0,01мкФ. Пока не включаю 200Мбит/с PLL прекрасно работает при том, что в проекте есть 20, 48, 100 и 400МГц. Даже если забить ПЛИС на 50% проблем нет. Проблемы начинаются только при подаче 200Мбит/с. Наверно стоит пожертвовать единственным светодиодом и перекинуть 200Мбит/с на другой пин...

-

Я его не обманывал. Со стороны Quartus не было никакой ругани на размещение данных пинов. Был только Warning по поводу отсутствия на данном пине DDIO буфера. Даже если этот пин не задействовать в проекте, проблема не исчезает. И чем не устраивает 0,1мкФ? На большинстве отладочных плат сделано именно так. И на всех предыдущих проектах я ставил 0,1 или 0,22 и проблем не было.

-

Cyclone IV PLL теряет захват

BSACPLD опубликовал тема в Работаем с ПЛИС, области применения, выбор

Коллеги, сталкивался ли кто-нибудь с такой проблемой: Есть два сигнала проходящих через сдвоенный LVDS->LVTTL буфер и заходящих на соседние клоковые пины (24 и 25 пины EP4CE22E22I7). Один из них клок 100МГц, второй - последовательные данные 200Мбит/с DDR. Расстояние от буфера до ПЛИС всего 0.5 см. Сигнал locked с PLL выведен на светодиод. Когда на линии данных ничего нет, сигнал locked в норме (светодиод горит непрерывно). Как только на линии данных появляется активность (для простоты я просто даю туда меандр 100МГц), сигнал locked начинает моргать или вообще исчезает. Причем проблема только с этим единственным сигналом. Остальные сигналы приходящие на ПЛИС никак не влияют на работоспособность PLL. Конденсаторы по питанию проверил - как и должно быть 0,1мкФ на каждый пин. 1мкФ по питанию буфера. Источник питания стоит на 2А (TPS82084). По идее должно хватить с запасом, тем более что ПЛИС заполнена всего на несколько процентов. По началу я грешил на LVDS->LVTTL буфер, но сигнал на выходе совершенно чистый. Все что можно уже проверил. Уже не знаю что и думать... В первый раз такое... Может ли быть, что если на два соседних клоковых пина заходят довольно высокочастотные сигналы, один сигнал очень сильно наводится на другой внутри самой ПЛИС? -

Собственно говоря вопрос как можно оперативно сбрасывать счетчик каналов АЦП в scan mode? Нужно для того, чтобы оцифровка по первому внешнему импульсу запуска АЦП начиналась именно с нулевого канала. Пробовал делать следующим образом: AD1CON2CLR = (1<<_AD1CON2_CSCNA_POSITION) ; AD1CON2SET = (1<<_AD1CON2_CSCNA_POSITION) ; но такой вариант не работает. Вариант через бит ON слишком долгий, т.к. данный бит полностью снимает питание с АЦП.

-

Решил наконец проблему :) МК PIC32MX575F256H. Дело было в том, что функции через которые я настраивал DMA почему-то не устанавливали бит ON в регистре DMACON. Проблема решилась ручной установкой данного бита. Вот какая в итоге получилась процедура инициализации: AD1CSSL = (1<<_AD1CSSL_CSSL9_POSITION) | (1<<_AD1CSSL_CSSL8_POSITION) | (1<<_AD1CSSL_CSSL7_POSITION) | (1<<_AD1CSSL_CSSL6_POSITION) | (1<<_AD1CSSL_CSSL5_POSITION) | (1<<_AD1CSSL_CSSL4_POSITION) | (1<<_AD1CSSL_CSSL3_POSITION) | (1<<_AD1CSSL_CSSL2_POSITION) | (1<<_AD1CSSL_CSSL0_POSITION); AD1CON3 = (0<<_AD1CON3_ADRC_POSITION) | (2<<_AD1CON3_SAMC_POSITION) | (2<<_AD1CON3_ADCS_POSITION) ; AD1CON2 = (0<<_AD1CON2_VCFG_POSITION) | (0<<_AD1CON2_OFFCAL_POSITION) | (1<<_AD1CON2_CSCNA_POSITION) | (8<<_AD1CON2_SMPI_POSITION) | (0<<_AD1CON2_BUFM_POSITION) | (0<<_AD1CON2_ALTS_POSITION) ; AD1CON1 = (1<<_AD1CON1_ON_POSITION) | (0<<_AD1CON1_SIDL_POSITION) | (0<<_AD1CON1_FORM_POSITION) | (1<<_AD1CON1_SSRC_POSITION) | (0<<_AD1CON1_CLRASAM_POSITION) | (1<<_AD1CON1_ASAM_POSITION) | (0<<_AD1CON1_SAMP_POSITION) ; IPC0 = (5<<_IPC0_INT0IP_POSITION) | (0<<_IPC0_INT0IS_POSITION); IPC6 = (6<<_IPC6_AD1IP_POSITION) | (0<<_IPC6_AD1IS_POSITION) ; IPC5 = (7<<_IPC5_T5IP_POSITION) | (0<<_IPC5_T5IS_POSITION) ; IFS0CLR = (1<<_IFS0_T5IF_POSITION) | (1<<_IFS0_INT0IF_POSITION); IFS1CLR = (1<<_IFS1_AD1IF_POSITION) | (1<<_IFS1_DMA0IF_POSITION); IEC0 = (1<<_IEC0_T5IE_POSITION) | (0<<_IEC0_INT0IE_POSITION); IEC1 = (0<<_IEC1_AD1IE_POSITION) | (0<<_IEC1_DMA0IE_POSITION); INTCONSET = (1<<_INTCON_INT0EP_POSITION); DMACONbits.ON = 1; DmaChnConfigure (DMA_CHANNEL0, DMA_CHN_PRI3, DMA_CONFIG_AUTO); DmaChnSetTxfer (DMA_CHANNEL0, (void*)(&ADC1BUF0), (void*)ADC_BUF, 16*9, 16*9*128, 16*9); DmaChnSetEventControl (DMA_CHANNEL0, DMA_EV_START_IRQ_EN | DMA_EV_START_IRQ(_ADC_IRQ)); DmaChnSetEvEnableFlags (DMA_CHANNEL0, DMA_EV_CELL_DONE); DmaChnSetIntPriority (DMA_CHANNEL0, INT_PRIORITY_LEVEL_4, INT_SUB_PRIORITY_LEVEL_0); DmaChnClrIntFlag (DMA_CHANNEL0); INTEnableSystemMultiVectoredInt (); DmaChnIntEnable (DMA_CHANNEL0); DmaChnEnable (DMA_CHANNEL0);

-

Коллеги, помогите, пожалуйста, понять в чем причина неработоспособности следующего кода: Инициализация: AD1CSSL = (1<<_AD1CSSL_CSSL9_POSITION) | (1<<_AD1CSSL_CSSL8_POSITION) | (1<<_AD1CSSL_CSSL7_POSITION) | (1<<_AD1CSSL_CSSL6_POSITION) | (1<<_AD1CSSL_CSSL5_POSITION) | (1<<_AD1CSSL_CSSL4_POSITION) | (1<<_AD1CSSL_CSSL3_POSITION) | (1<<_AD1CSSL_CSSL2_POSITION) | (1<<_AD1CSSL_CSSL0_POSITION); AD1CON3 = (0<<_AD1CON3_ADRC_POSITION) | (2<<_AD1CON3_SAMC_POSITION) | (2<<_AD1CON3_ADCS_POSITION) ; AD1CON2 = (0<<_AD1CON2_VCFG_POSITION) | (0<<_AD1CON2_OFFCAL_POSITION) | (1<<_AD1CON2_CSCNA_POSITION) | (8<<_AD1CON2_SMPI_POSITION) | (0<<_AD1CON2_BUFM_POSITION) | (0<<_AD1CON2_ALTS_POSITION) ; AD1CON1 = (1<<_AD1CON1_ON_POSITION) | (0<<_AD1CON1_SIDL_POSITION) | (0<<_AD1CON1_FORM_POSITION) | (1<<_AD1CON1_SSRC_POSITION) | (1<<_AD1CON1_CLRASAM_POSITION) | (1<<_AD1CON1_ASAM_POSITION) | (0<<_AD1CON1_SAMP_POSITION) ; IPC0 = (5<<_IPC0_INT0IP_POSITION) | (0<<_IPC0_INT0IS_POSITION); IPC6 = (6<<_IPC6_AD1IP_POSITION) | (0<<_IPC6_AD1IS_POSITION) ; IPC5 = (7<<_IPC5_T5IP_POSITION) | (0<<_IPC5_T5IS_POSITION) ; IFS0CLR = (1<<_IFS0_T5IF_POSITION) | (1<<_IFS0_INT0IF_POSITION); IFS1CLR = (1<<_IFS1_AD1IF_POSITION); IEC0 = (1<<_IEC0_T5IE_POSITION) | (0<<_IEC0_INT0IE_POSITION); IEC1 = (0<<_IEC1_AD1IE_POSITION); INTCONSET = (1<<_INTCON_INT0EP_POSITION); int chn = 1; DmaChnConfigure (chn, DMA_CHN_PRI2, DMA_CONFIG_DEFAULT); DmaChnSetEventControl (chn, DMA_EV_START_IRQ_EN | DMA_EV_START_IRQ(_ADC_IRQ)); DmaChnSetTxfer (chn, (void*)&ADC1BUF0, (void*)ADC_DATA, 2, 18, 2); DmaChnSetEvEnableFlags (chn, DMA_EV_BLOCK_DONE); INTEnableSystemMultiVectoredInt (); DmaChnSetIntPriority (chn, INT_PRIORITY_LEVEL_4, INT_SUB_PRIORITY_LEVEL_0); DmaChnIntEnable (chn); DmaChnEnable (chn); Обработчики: void __ISR(_DMA_1_VECTOR, IPL4AUTO) DMA1_ISR (void) { IFS1CLR = (1<<_IFS1_DMA1IF_POSITION); LATDINV = (1<<_LATD_LATD11_POSITION); } //------------------------------------------------------------------- void __ISR(_EXTERNAL_0_VECTOR, IPL5AUTO) INT0_ISR (void) { IFS0CLR = (1<<_IFS0_INT0IF_POSITION); LATDINV = (1<<_LATD_LATD11_POSITION); } //------------------------------------------------------------------- void __ISR(_ADC_VECTOR, IPL6AUTO) ADC_ISR (void) { ADC_DATA[0] = ADC1BUF0; ADC_DATA[1] = ADC1BUF1; ADC_DATA[2] = ADC1BUF2; ADC_DATA[3] = ADC1BUF3; ADC_DATA[4] = ADC1BUF4; ADC_DATA[5] = ADC1BUF5; ADC_DATA[6] = ADC1BUF6; ADC_DATA[7] = ADC1BUF7; ADC_DATA[8] = ADC1BUF8; IFS1CLR = (1<<_IFS1_AD1IF_POSITION); AD1CON1SET = (1<<_AD1CON1_ASAM_POSITION); LATDINV = (1<<_LATD_LATD11_POSITION); } Если разрешить INT0IE или AD1IE, то соответствующие прерывания срабатывают, но вот когда пытаюсь поймать прерывание от DMA запускаемого от ADC, то ничего не происходит. Похоже на косяк в инициализации DMA, но только я никак не могу понять где именно :(

-

Коллеги, помогите решить следующую проблему. Установил на новый компьютер Windows 7 x64, MPLAB 8.92 и Pickit3 Programmer. Pickit3 видится и нормально работает через Pickit3 Programmer, но не видится в MPLAB. MPLAB пишет "Pickit3 not found". Тот же самый Pickit3 нормально видится и через MPLAB и через Pickit3 Programmer на старом компьютере. Подскажите в чем может быть проблема. UPD. В safe mode нормально коннектится. Похоже дело в настройках винды. UPD2. Решил проблему :) Дело было в параметрах контроля учетных записей. Я отключал контроль учетных записей чтобы установить IAR 5.50, а обратно включить забыл. Как оказалось, MPLAB зачем-то нужно чтобы контроль учетных записей был включен для нормальной работы с Pickit3.