aT-DeviLru

Свой-

Постов

105 -

Зарегистрирован

-

Посещение

Весь контент aT-DeviLru

-

Некоторые спрашивают расшифровку на форуме xilinx: https://support.xilinx.com/s/question/0D54U00007H2baYSAR

-

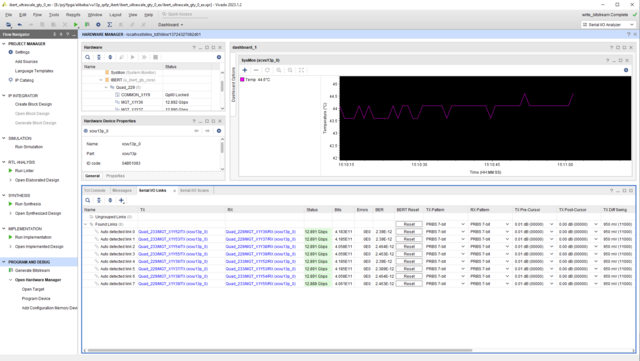

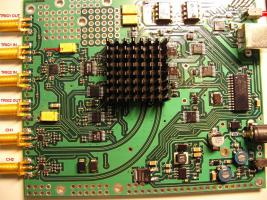

Оставлю отзыв о продавце и платах, приобрёл такой ускоритель с доставкой через СДЭК, к доставке вопросов не было - платы приехали в целостности и довольно быстро (~6 дней), сами платы работоспособные, проверил флешку, XDMA PCIe, 100G QSFP, 4xDDR4. Из нюансов - встроенный программатор на плате не распаян, поэтому его нужно докупать отдельно или использовать внешний программатор, обычный китаец DLC10 с авито или озона подходит. Для питания платы используется разъём 8pin EPS (как для питания процессора), а не 8pin PCIe. Из полезных ссылок: 1. Репозиторий с примерами проектов под эту плату https://github.com/maswx/vu13p разработчик китаец, поэтому код так себе, встречаются упоминания GPT4) 2. Описание платы от китайцев https://zhuanlan.zhihu.com/p/617050950 Ну и нужно понимать, что система охлаждения и питания на этой плате выглядит более простой по сравнению с SQRL BCU1525 и Bittware CVP-13, поэтому загрузить плату на 100% это скорее всего не позволит, но с другой стороны и стоимость этой платы значительно меньше приведённых плат для майнинга.

-

www.eetop.cn

aT-DeviLru ответил Losik тема в Форумы и конференции

Большое спасибо за помощь! -

www.eetop.cn

aT-DeviLru ответил Losik тема в Форумы и конференции

Добрый день, помогите, пожалуйста, скачать PathWave Windows Patcher v1.3.zip https://bbs.eetop.cn/thread-925473-1-1.html -

Под многие камеры Canon можно писать свой софт - https://www.magiclantern.fm/

-

В Vivado начиная с версии 2018.1 добавлено ip-ядро Polar Encoder/Decoder, при желании можно его поизучать.

-

Наверное уже не актуально, но может кому-нибудь ещё пригодиться, на базе питерского политеха имеется мастерская для молодёжи - фаблаб, где можно самостоятельно работать на различном оборудовании, в том числе на 3D-принтере. http://fablab.spbstu.ru/ru_RU/tariffs/

-

Может быть кто-нибудь напишет, как в матлабе решаются следующие вопросы: 1. Можно ли использовать аппаратные блоки ПЛИС и при этом производить симуляцию в simulink? Для оптимального описания, например, высокоскоростных фильтров (рабочие частоты > 450 МГц), как правило, используются прямые вставки примитивов DSP48 с ручной конфигурацией их параметров. 2. Можно ли переходить на разные клоковые домены, например по середине схемы поставить MMCM, перейти на двойной клок, произвести обработку на нём, потом перейти обратно на одинарный клок? 3. Можно ли использовать шифрованные ip-ядра (которых нет в Xilinx System Generator) на языках VHDL/Verilog? 4. Можно ли задавать атрибуты у элементов, например один блок памяти сделать на лутах, другой на блочной памяти, часть сдвиговых регистров сделать на SRL16, часть на FDRE? 5. Можно ли работать с асинхронными клоковыми доменами, например поставить асинхронное фифо? 6. Можно ли размножить какой-нибудь сигнал для уменьшения fanout и улучшения таймингов? 7. Есть ли в simulink (графическое представление) адекватный контроль за изменениями кода (git), чтобы можно было производить удобную коллективную разработку (слияние кода, просмотр изменений, итд)? 8. Есть ли нормальный редактор кода для матлаба, например полноценная интеграция с редактором Sublime Text?

-

Xilinx FIR Compiler в Vivado умеет делать интерполяцию параллельных потоков, поэтому задача интерполяции сигнала в 2 раза с Fд = 250 МГц до 500 МГц на клоке 250 МГц решается очень просто.

-

Посмотрите application note от Xilinx: xapp524,xapp855,xapp856,xapp860,xapp866,xapp585,xapp774,xapp1064,xapp1071, потом можно поискать поиском по форуму по названиям xapp-ов, было уже множество тем с разбором приёма такого типа данных. Даже статья на хабре есть - https://habrahabr.ru/post/313692/

-

Vivado 2016.3

aT-DeviLru ответил Alex77 тема в Среды разработки - обсуждаем САПРы

Сегодня добавили и сам дистрибутив Vivado 2016.3 для скачивания, образ теперь занимает 20.61 ГБ, прошлая версия (2016.2) была существенно легче - 11.17 ГБ. -

Непонятки с VHDL

aT-DeviLru ответил Tausinov тема в Языки проектирования на ПЛИС (FPGA)

Рассмотрим случай когда все 3 мастера ожидают передачи данных, т.е. ireq_tvalid_vect = "111": 1) По ресету инициализируется переменная curr_num := 2; 2) 1-я итерация цикла "stream_fingering_l : for stream_num in 3 downto 1 loop" stream_num = 3; => loop_num = (curr_num + stream_num) mod 3 = (2 + 3) mod 3 = 2 curr_num := loop_num = 2 3) 2-я итерация цикла ... stream_num = 2; => loop_num = (curr_num + stream_num) mod 3 = (2 + 2) mod 3 = 1 curr_num := loop_num = 1 4) 3-я итерация цикла ... stream_num = 1; => loop_num = (curr_num + stream_num) mod 3 = (1 + 1) mod 3 = 2 curr_num := loop_num = 2 В итоге получаем, что на выход арбитра всегда коммутируется 2-ой мастер. Второй пример работает корректно, т.к. перебирает циклически все индексы. -

В квесте есть отдельная документация на многопроцессорную симуляцию: "Questa ® SIM Multi-core Simulation User’s Guide" (смотреть в папке docs\pdfdocs)

-

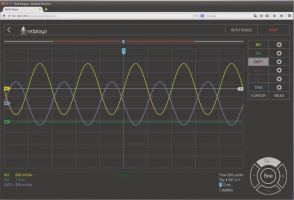

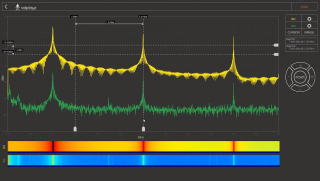

В качестве примера можно посмотреть исходники и документацию открытого проекта Red Pitaya, например, там имеется генератор сигналов, осциллограф и анализатор спектра с веб-интерфейсом, всё это работает под arm linux-ом.

-

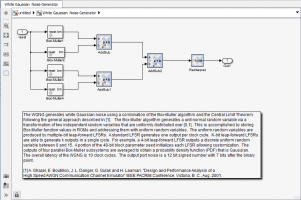

Генератор белого шума есть в примерах Xilinx System Generator, его реализация полностью открыта для пользователя, поэтому при желании можно очень быстро портировать код под любую другую ПЛИС.

-

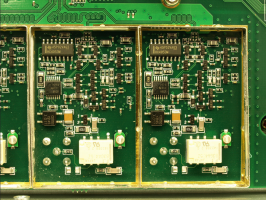

Всё не так и дорого, как и предложил khach можно взять самый дешёвый 8-разрядный АЦП на 1ГГц - Hittite HMCAD1511, стоимость которого составляет 66$ при покупке 1шт в digikey и подключить к дешёвой ПЛИС Xilinx Spartan-6 XC6SLX25 (47$). Все остальные комплектующие уже не так дорого стоят. Данная связка АЦП и ПЛИС успешно используется в осциллографе Rigol DS1054Z, фотографии и схемы которого можно посмотреть на зарубежном форуме: http://www.eevblog.com/forum/blog/eevblog-...1054z-teardown/ http://www.eevblog.com/forum/blog/eevblog-...-rigol-ds1054z/ Прикрепляю несколько фотографий его внутренностей:

-

Пример проекта на кикстартере с осциллографом на 10ГГц на компараторах, заявлена стоимость 300$: https://www.kickstarter.com/projects/185599...sb-oscilloscope Документация на прибор: http://www.fastsampling.com/Products/DS800...800Manual17.pdf Обсуждение проекта на зарубежном форуме: http://www.eevblog.com/forum/testgear/10-g...rwin-sabanovic/ http://www.eevblog.com/forum/crowd-funded-...b-oscilloscope/

-

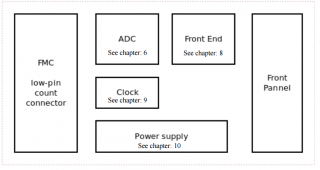

Тема очень интересная, предложу в качестве основы взять открытые проекты от CERN, тогда цифровой осциллограф будет состоять из двух плат: 1. материнская плата, которая содержит: разъём FMC для подключения платы АЦП, ПЛИС для обработки потока с АЦП, Ethernet 1Gb, USB 3.0 или PCI-Express для передачи данных на ПК. В интернете множество открытых примеров реализации данных интерфейсов, поэтому особых проблем быть не должно. Вот пара примеров таких плат от CERN, которые можно взять за основу (проекты полностью открытые – есть исходники схем, печатных плат, ПО для ПЛИС и ПК). Плата Simple PCIe FMC carrier (SPEC) (ссылка на страницу проекта http://www.ohwr.org/projects/spec/wiki) Плата AMC FMC Carrier (AFC) (ссылка на страницу проекта http://www.ohwr.org/projects/afc/wiki) 2. Плата с АЦП на 1-2ГГц, которая содержит: разъём FMC для подключения к материнской плате, аналоговый вход, АЦП, источник клока и источник питания. За основу можно взять проект FMC ADC 1G 10b 2cha (ссылка на страницу проекта http://www.ohwr.org/projects/fmc-adc-1g10b2cha/wiki). Прикрепляю документ где приведено ТЗ, структурная схема проекта, выбор комплектующих, примеры схемотехники аналогового входа, клока и многое другое. CERN_fmc_adc_1g10b2ch.pdf Структурная схема следующая: Пример аналоговой части осциллографа (см. документ http://www.ti.com/lit/ds/symlink/lmh6518.pdf): Пример похожей платы от CERN с 4-я АЦП 250 МГц 16 бит (ссылка на страницу проекта http://www.ohwr.org/projects/fmc-adc-250m-16b-4cha/wiki): На том же сайте есть пример простого РЧ аттенюатора на диапазон напряжений 50 мВ-1000 В с полосой 0-2 ГГц. (ссылка на страницу проекта http://www.ohwr.org/projects/vme-rf-att-4cha/wiki) Разделение проекта осциллографа на две платы в будущем позволит на его основе сделать векторный анализатор цепей, анализатор спектра и другие интересные проекты. Готов принять участие в создании осциллографа (анализатора спектра или векторного анализатора цепей) в качестве разработчика ПЛИС, успешный опыт работы с АЦП >1ГГц в наличии.

-

Идея курсов по реализации алгоритмов ЦОС на ПЛИС отличная, было бы интересно освоить реализацию какого-нибудь телекоммуникационного стандарта таким образом (WI-FI, LTE, DVB-T, и др..), думаю такой формат изучения здорово сэкономит время (с нескольких лет до нескольких месяцев) и позволит узнать много новых идей по реализации блоков ЦОС. Fat Robot, можете поделиться Вашим опытом и идеями по поводу методологии верификации блоков цос? Я в этой области новичок, пока могу выделить два подхода к верификации: 1. В Matlab/Simulink создаётся эталонная модель блока ЦОС с набором тестовых воздействий, на следующем этапе подключается аппаратная реализация блока на языке описания аппаратуры, например, через блок HDL Cosimulation и вычисляется разность между выходом эталонной модели и аппаратной реализации. На следующем этапе можно запустить FPGA-in-the-loop верификацию для проверки алгоритма непосредственно в железе. 2. Из эталонной модели и набора тестовых воздействий, используя Matlab/Simulink HDL Verifier, генерируется SystemC код для подключения к уже существующему верификационному окружению (UVM и др) на языке HDL. 3. Генерация кода непосредственно из эталонной модели Matlab/Simulink/Xilinx System Generator. Может быть есть ещё какие-нибудь способы верификации блоков ЦОС?

-

ZedBoard + FMC адаптер

aT-DeviLru ответил DASM тема в Продам

Готов приобрести плату с самовывозом из Питера, отправил лс. -

Спасибо за информацию про атрибут generator_default, с его помощью можно успешно изменять параметры ядер "на лету" без пересборки в coregen'е. Но данный атрибут работает только в синтезаторе XST, возможно кто-нибудь нашёл способ как реализовать аналогичный функционал в синтезаторах Synopsys Synplify или MG Precision? Пока вижу единственный вариант - это добавить все библиотеки ядер вместе с их зависимостями в исходный проект, а это несколько десятков файлов и библиотек, может быть есть более элегантные варианты решения?

-

plugin к JTAG для Xilinx

aT-DeviLru ответил dsmv тема в Среды разработки - обсуждаем САПРы

1. Есть простой открытый вариант программатора на ftdi, который поддерживает в том числе chipscope, работает используя Xilinx Virtual Cable Daemon. http://debugmo.de/2012/02/xvcd-the-xilinx-...l-cable-daemon/ 2. Посмотрите документ "Digilent Adept JTAG Interface (DJTG) Programmer’s Reference Manual", там описан API для управления контроллером JTAG. -

Данные из чипскопа можно передать в matlab или modelsim для последующего анализа; или требуется потоковая непрерывная передача?

-

В связи с переездом срочно продаю в Санкт-Петербурге накопившуюся технику. 1. Осциллограф С1-65А + генератор сигналов ГНЧР-2. Цена: 1200 руб. - Продано В комплекте пара щупов, осциллограф и кабель питания. 2. Источник питания Б5-47. Цена: 250 руб. - Продано При покупке осциллографа, генератора и источника питания вместе - цена 1300 руб за всё. 3. Мультиметр fluke 87. Цена: 1000 руб. - Продано Покупал в таком паршивом состоянии, предыдущий владелец встроил ещё один выключатель, вместо оригинального предохранителя стоит дешёвая замена, крепление дисплея тоже отремонировано. Сам дисплей подсел, если смотреть на дисплей под углом больше 90 гр (сверху), то дисплей "выцветает" - плохо читаем. 4. Усилитель ЗЧ WP2006 mk II v1.2, цена: 10 000 руб. 5. Усилитель ЗЧ Stonecold, цена: 1200 руб. 6. Плеер из журнала Vogue. Цена: 300 руб. (см. http://www.vogeeky.org и http://habrahabr.ru/post/108921/) 7. Свитч 16 портовый 100 Мбит/сек, Level One FSW-1602TX, цена: 400 руб. Работает на удивление отлично, в своё время раздавал интернет на пол блока в общежитии, зависаний и иных проблем никогда не было. 8. Примерно пол бухты витой пары категории 5E. Цена: 400 руб. Осмотр и покупка территориально метро пл. Мужества или Академическая. Телефон для связи: +7-921-7632579, можно звонить с 09.00 до 01.00.

-

RED PITAYA

aT-DeviLru ответил Ar-han тема в Работаем с ПЛИС, области применения, выбор

Джиттер 1пс, генератор TXCBF. Выбор генератора зависит от предъявляемых требований к входным сигналам. В бюджетных изделиях часто применяют генераторы фирм Abracon и Crystek. Примеры можете посмотреть в hdl репозитории AD.