-

Постов

1 611 -

Зарегистрирован

-

Посещение

-

Победитель дней

2

Весь контент juvf

-

Modbus RTU

juvf ответил juvf тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Да я не силен в *HDL. Ну придется попробовать, изучать. Я его не хочу полностью аппаратный. Функции буду обрабатывать программно. Мне от аппратной части нужен блок, в который проц запишит скорость уарта и адрес слэйва. В ответ получит прерывание, если пришел пакет для этого слэйва, без ошибок и crc совпал. По прерыванию проц дожен считать с блока по какойнить шине SDRAM данные, обработать их, загрузить ответ в блок и дёрнуть у этого блока сигнал "Start Transmit". как-то так... Меня пугает, что в этом блоке придется писать что-то типа своего UART FIFO. Хотя на opencores есть такой блок, но разбираться с ним и дорабатывать его до модбуса - тоже перспектива не радостная. -

в квартусе 10.0 и 10.1 я добавлял "DDR2 SDRAM Controller with ALTMEMPHY". работает нормально. операционка вин7-32. может квартус на 10-ый поменять?

-

Modbus RTU

juvf опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Нашел на opencores, но там проект пустой. Есть у кого-нибудь аппараптый Modbus RTU? Или ссылка, где его можно взять? -

Ну наверно любым программатором для msp430. Я вытаскивал программой Olimex MSP Programmer и с помошью MSP430-JTAG-TINY.

-

нашел эту книжку в вашем архиве. сорри.

-

Там ссылка на книгу Семейство микроконтроллеров MSP430: Рекомендации по применению (пер. с англ.) В вашем архиве такую книжку не нашел? Так у вас есть такая книга или нет?

-

я с неё начинал MSP430F1xx_______________2004_rus.pdf

-

Как подружить MSP430-JTAG-TINY и msp430-gdbproxy? Захотел в Eclipse поднять отладку для msp430. Вот статья про это. Но не могу прокси запустить. d:\soft\mspgcc\bin>msp430-gdbproxy --port=3333 msp430 TIUSB Remote proxy for GDB, v0.7.1, Copyright (C) 1999 Quality Quorum Inc. MSP430 adaption Copyright (C) 2002 Chris Liechti and Steve Underwood GDBproxy comes with ABSOLUTELY NO WARRANTY; for details use `--warranty' option. This is Open Source software. You are welcome to redistribute it under certain conditions. Use the '--copying' option for details. debug: MSP430_Initialize() error: msp430: Could not initialize device interface (1) ^C d:\soft\mspgcc\bin> Пробовал тест d:\soft\mspgcc\bin>msp430-gdbproxy msp430 --selftest-usb-fet Remote proxy for GDB, v0.7.1, Copyright (C) 1999 Quality Quorum Inc. MSP430 adaption Copyright (C) 2002 Chris Liechti and Steve Underwood GDBproxy comes with ABSOLUTELY NO WARRANTY; for details use `--warranty' option. This is Open Source software. You are welcome to redistribute it under certain conditions. Use the '--copying' option for details. notice: msp430: TI USB FET self-test requested debug: MSP430_Initialize() error: msp430: Could not initialize device interface (1) debug: MSP430_Initialize() debug: MSP430_Configure() debug: MSP430_VCC(3000) debug: MSP430_Identify() error: msp430: Could not find device (or device not supported) (4) debug: MSP430_VCC(0) debug: MSP430_VCC(3000) debug: MSP430_Reset(ALL_RESETS) debug: MSP430_Close() Assertion failed: !msp430_status.is_open, file target_msp430.c, line 745 This application has requested the Runtime to terminate it in an unusual way. Please contact the application's support team for more information. d:\soft\mspgcc\bin> Обновил firmware - не помогло. Программатор от Olimex и IAR WB работают нормально. А прокси не могу запустить. Кто-нибудь запускал прокси на MSP430-JTAG-TINY? Какие ещё есть способы поднять отладку в Eclipse?

-

Во млин!!! Удалось записать в озу данные, и даже тайминги все правильно расставленны. Пишу с помощю IOWR_16DIRECT(DAC_MEM_BASE, 10, 0x55aa); - кто бы мог подумать, что доступ к внешнему озу..... через IOWR_16DIRECT. Хотя тут же SDRAM стоит, через альтеровский контроллер подключенна: обращяюсь к ней без всяких IOWR_16DIRECT. ps в порты PIO пишу через IOWR_ALTERA_AVALON_PIO_DATA(IOLED_BASE, led);. По идее, если сделать секцию памяти .myPio в BSP и разместить её по адресу IOLED_BASE ..... яже могу потом обращаться без всяких IOWR_ALTERA_AVALON_PIO_DATA , а как-то __attribute__ ((section (".myPio "),used)) unsigned int led; ... //а потом писать в порт led = 0x12; По идее так должно работать?

-

Доброго времени. Подключил к 2-хпортовому озу ниос. вопрос - как из ниоса достучатся до озу? как писать туда? В эклипсе в BSP создал секцию памяти и разместил её на своем Avalon Memory Mapped Tristate Slave. теперь из кода программы пытаюсь записать в озу что-нибудь. пишу так __attribute__ ((section (".dac"),used)) unsigned int dacData[512]; .... while(1) { dacData[16] = 0x55aa; pauseMm(1000); } смотрю сигналТапом сигнал WR- нету. В нуле всегда. на шине данных и шине адреса что-то меняется. а WR - нет. Может я не правильно dacData[512] разместил?

-

В эклипсе должно быть так http://help.eclipse.org/help33/index.jsp?t...tings_steps.htm Но в Eclipse-NIOS IDE нет таких вкладок (см рис). как их добавить? Вроде нужен plug-in какой то. Где его взять и как установить?

-

Как добавить этап сборки в Eclipse?

juvf опубликовал тема в GNU/OpenSource средства разработки

В QtCreator-e в настройках сборки можно добавить свои этапы. например перед началом компиляции выполнить MoyEtap.com -qwe -asd=1234 в папке ../../anyDir. Где такое настраивается в Eclipse? -

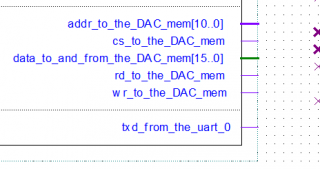

Спасибо, что-то получаться стало. ....... вот мой тсл # TCL File Generated by Component Editor 10.1 # Wed Mar 02 13:46:07 YEKT 2011 # DO NOT MODIFY # +----------------------------------- # | # | DAC_memOut "DAC_memOut" v1.0 # | Anisimov 2011.03.02.13:46:07 # | # | # +----------------------------------- # +----------------------------------- # | request TCL package from ACDS 10.1 # | package require -exact sopc 10.1 # | # +----------------------------------- # +----------------------------------- # | module DAC_memOut # | set_module_property NAME DAC_memOut set_module_property VERSION 1.0 set_module_property INTERNAL false set_module_property OPAQUE_ADDRESS_MAP true set_module_property GROUP "Memories and Memory Controllers/SDRAM" set_module_property AUTHOR Juvf set_module_property DISPLAY_NAME DAC_memOut set_module_property INSTANTIATE_IN_SYSTEM_MODULE false set_module_property EDITABLE true set_module_property ANALYZE_HDL AUTO # | # +----------------------------------- # +----------------------------------- # | files # | # | # +----------------------------------- # +----------------------------------- # | parameters # | # | # +----------------------------------- # +----------------------------------- # | display items # | # | # +----------------------------------- # +----------------------------------- # | connection point avalon_tristate_slave # | add_interface avalon_tristate_slave avalon_tristate end set_interface_property avalon_tristate_slave activeCSThroughReadLatency false set_interface_property avalon_tristate_slave associatedClock clock set_interface_property avalon_tristate_slave explicitAddressSpan 0 set_interface_property avalon_tristate_slave holdTime 0 set_interface_property avalon_tristate_slave isMemoryDevice true set_interface_property avalon_tristate_slave isNonVolatileStorage false set_interface_property avalon_tristate_slave maximumPendingReadTransactions 0 set_interface_property avalon_tristate_slave printableDevice false set_interface_property avalon_tristate_slave readLatency 0 set_interface_property avalon_tristate_slave readWaitStates 0 set_interface_property avalon_tristate_slave readWaitTime 0 set_interface_property avalon_tristate_slave setupTime 0 set_interface_property avalon_tristate_slave timingUnits Cycles set_interface_property avalon_tristate_slave writeWaitTime 0 set_interface_property avalon_tristate_slave ENABLED true add_interface_port avalon_tristate_slave addr address Input 10 add_interface_port avalon_tristate_slave data data Bidir 16 add_interface_port avalon_tristate_slave rd read Input 1 add_interface_port avalon_tristate_slave wr write Input 1 add_interface_port avalon_tristate_slave cs chipselect_n Input 1 # | # +----------------------------------- # +----------------------------------- # | connection point clock # | add_interface clock clock end set_interface_property clock clockRate 0 set_interface_property clock ENABLED true add_interface_port clock clk clk Input 1 # | # +----------------------------------- add_interface_port avalon_tristate_slave addr address Input 10 - десяти разрядная шина адреса. почему в графически ниос показывает 11 разрядную шину? бага? Чем тактировать внеешнее озу? клоками ядра?

-

"интегрировать свой компонент в SOPC" - ну протакую фичу вообще не знал....... Я хочу пока так: писать в 2-х портовую память из ниоса, а читать другим устройством.

-

Ну так когда в BSP редактор заходишь, парсится *.sopcinfo. Если sopcinfo у меня обновлен, то я должен увидеть новые секции и регионы памяти. По крайней мере так было при добавлении епцс и сдрам. Почему то новый контроллер не виден в редакторе. см рисунок. Должен появится регион DacMemOut. Или его в ручную добавлять нужно? Может я в билдере его не так создал? - не нашел ((( На рисунке 2-портовая память. Как такую память подключить к ниосу? Что нужно сделать в SOPC билдере? Мосты, тристэйты, авалоны, от куда брать клок на память? Не могу найти доку по этим вопросам в альтере. была где-то. Не могу найти.

-

Собрал двухпортовую память. Обычную, типа SDRAM. Пытаюсь подключить к ниосу. Не получается. Посмотрел примерный проект, собрал в ниосе новый контроллер памяти на базе Avalon Memory Mapped Tristate Slave, добавил в ниос новый контроллер, новыый контроллер, добавил в ниос tristate_bridge. Вроде в квартусескомпилялся проект. Теперь в эклипсе пытаюсь достучаться до этой ОЗУ. Но как? Попытался создать в BSP секцию памяти и указать на этот контроллер - не получается, нет BSP редакторе в выборе этой памяти. Есть какая нибудь дока по подключению двухпортовых озу или вообще, по созданию параллельной шины Adress/Data в ниосе? Как это делается? Для SRAM, для SDRAM? Для чего нужен Avalon Memory Mapped Tristate Slave и tristate_bridge?

-

шаблон на Си. Это я переименовал исходник в срр. Не работает в си такой for(int i =0;... Преределал на си - теже проблемы. Я сотрю вывод компилятора, вроде по расширению нужный компилятор подхватывается. А про жаву...... нашел на форуме альтеры подобные проблемы. вроде люди от них избавились путем переустановки эклипса. буду пробовать

-

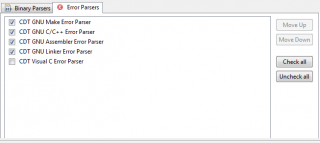

Сделал как доктор прописал. собрал Hallo word! В процессоре только ядро, ончип, джитаг, пио, сисАйДи и таймер. В эклипсе из шаблона сделал хеллоуВорд. Эльф не грузится. Вообще не понятно. При запуске Debug Configurations... в Error Log сипятся ошибки. см рис. потом при запуске дебага опять сыпятся теже ошибки. Когда эльф грузился и дебаг нормально работал - эти ошибки тоже сыпались. А т.к. альтера генерит варненги и рекомендует на них не обращять внимания, то на эти ошибки я тоже не обращял внимания. Работает ведь. Может в этом дело? Что это за ошибки и как от них избавится? CPU master group not set. что за группа и как её установить? CPU architecture type not set. - а это вообще кто? ну и остальные..... ps винда-семёрка. квартус 10.1

-

дак а как проверить память программой из ниоса, если программа в ниос не грузится? Проблема в том, что я не могу скомпелированную программу загрузить и запустить в ниосе.

-

Нашел пример проекта c SDRAM для моей борды, для DE0. Там всего один констрейн - на внешний входной клок и в ниосе есть плл и клоки на озу идут с сдвигами. Сделал у себя так же. Всё рано не грузится elf. Правда в примере какой-то другой плл, в моём SOPC нет такого (10.1). Буду пробовать внешний плл и поиграюсь с фазами. А есть какая-нибудь утилита для проверки SDRAM? Например можно из кансоли дать команду, типа nios2_check_SDRAM и она вернёт ответ по которому можно судить: правильно настроены клоки и работает ли сдрам? А то может сдрам исправно работает и проблема эльфа не в этом скрыта.

-

спасибо за помощь. буду разбираться

-

ступил, действительно 8Мб - это сдрам. чип - Zentel A3V64S40ETP pdf в инклуде A3V64S40ETP_v1.2_Zentel.pdf

-

Ну я сам в проекте ни мапил память. ни каких секций не назначал. все по умолчанию. вот вывод линкера Info: Linking frontEndOS.elf nios2-elf-g++ -T'../frontEndOS_bsp/linker.x' -msys-crt0='../frontEndOS_bsp/obj/HAL/src/crt0.o' -msys-lib=ucosii_bsp -L../frontEndOS_bsp -Wl,-Map=frontEndOS.map -O0 -g -Wall -EL -mno-hw-div -mhw-mul -mno-hw-mulx -o frontEndOS.elf obj/Buffer.o obj/KeeperDevices.o obj/Spi.o obj/devices/Device.o obj/devices/FM25CL64.o obj/devices/Register.o obj/devices/deviceInfo.o obj/init.o obj/main.o obj/timer.o obj/uart.o -lm nios2-elf-insert frontEndOS.elf --thread_model ucosii --cpu_name cpu_0 --simulation_enabled false --id 0 --sidp 0x1004158 --timestamp 1297768557 --stderr_dev uart_0 --stdin_dev uart_0 --stdout_dev terminal --sopc_system_name cpuNew --quartus_project_dir "D:/Work/Quartus/TestBench" --jdi D:/Work/Quartus/TestBench/software/frontEndOS_bsp/../../topLevel.jdi Info: (frontEndOS.elf) 211 KBytes program size (code + initialized data). Info: 7973 KBytes free for stack + heap. Info: Creating frontEndOS.objdump nios2-elf-objdump --disassemble --syms --all-header --source frontEndOS.elf >frontEndOS.objdump [frontEndOS build complete]

-