Uree

Свой-

Постов

5 825 -

Зарегистрирован

-

Посещение

Весь контент Uree

-

Все нормально с софтом, а вот что у вас там происходит это вопрос.

-

Расчет волнового сопротивления

Uree ответил fademike тема в Работаем с трассировкой

-

Расчет волнового сопротивления

Uree ответил fademike тема в Работаем с трассировкой

Он будет стараться собрать то, что мне хочется, на тех материалах, которые у него есть. Нет у них как таковых типовых/ходовых сборок, каждый заказывает как придумает и стэк зависит от задачи. Подходы к задачам могут использоваться типовые, а результаты всегда будут разными. И стэк, заказываемый год назад запросто могут не суметь повторить сейчас, потому что материалы на складе другие, и все равно будут лепить по своему, подстраивать трассы/зазоры и т.д... Четсно говоря не знаю, что там написано, но можно и так и эдак: и Вопрос какая будет степень связности в этих парах. -

Расчет волнового сопротивления

Uree ответил fademike тема в Работаем с трассировкой

С чего вдруг такая математика? Там нет прямой зависимости, особенно в случае диффпар. И что там у резонита - понятия не имею. -

Расчет волнового сопротивления

Uree ответил fademike тема в Работаем с трассировкой

Производитель _всегда_ будет стараться подсунуть то, от чего ему нужно избавиться. Особенно если речь не идет о серии в десятки тыс. плат в неделю и на пять лет вперед. Так что на них всегда нужно давить. -

Расчет волнового сопротивления

Uree ответил fademike тема в Работаем с трассировкой

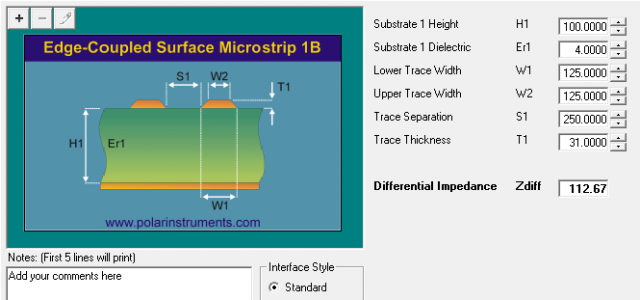

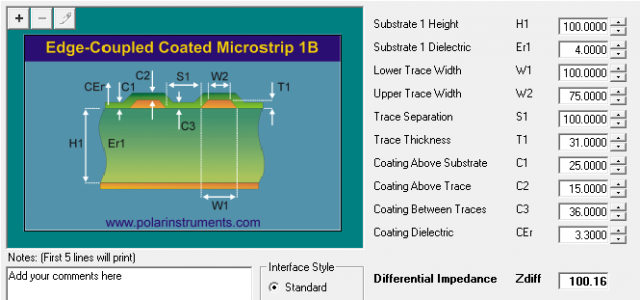

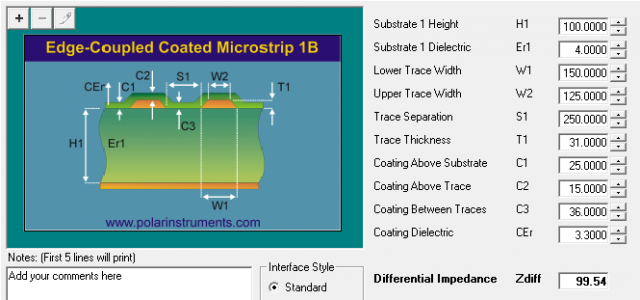

Не самый удачный стэк... Для препрега 51мкм на внешних слоях будет трудно сделать нужную геометрию - слишком узкие трассы будут получаться. Стоит ориентироваться на 65-75мкм. Ну внутренних тоже криво получается - слои питаний ближе к сигнальным, чем слои земли - где возвратные токи будут течь? По питаниям?:) Надо наоборот выбирать ядра потоньше, а препреги потолще. Диэл. проницаемости порядка 3.9/3.3 реальны для хай-спид/РФ диэлектриков на частотах в единицы/десяток ГГц, которые дорогие, слабо доступные и в таком дизайне совершенно не нужные. Реальные цифры порядка 4.2-4.4 для ядер и 4-4.2 для препрегов. Я бы советовал пересмотреть стэк, чтоб был более вменяемым. -

задание свапируемости пинов в символе ПЛИС

Uree ответил PorychikKize тема в Cadence

Насколько я знаю сигналы между секциями свапировать нельзя при каком угодно значении PIN_GROUP. Это просто в корне порушит схему, когда в одной секции будут собраны пины из разных секций. Пинам, которые не нужно свапить, можно просто ничего не задавать в PIN_GROUP. Как и есть по умолчанию. И да, ответ с 18-го года уже можно бы обновить. Тогда я писал имея опыт работы до версии 16.6 и там свап был не самым удобным. В последних версиях уже именно то, что нужно - на плате не нужно искать пины для свапа, достаточно кликать по трассам, к этим пинам подключенным, главное чтобы это была трасса без доп. контактов(типа подтяжки или чего-то подобного). Плюс эта трасса может быть на любом слое, главное чтобы начиналась с пина ПЛИС и была "висящей". А на схеме теперь меняются не только номера пинов, как раньше было, но полностью, номер и имя этого пина. В итоге полностью меняется расположение пинов в секции после свапа, но номера<->функционал(описание) пина сохраняются синхронизированными. В общем могу только порекомендовать пользоваться свапом. Реально упрощает жизнь и ускоряет работу. -

А, тогда проще установить. Причем лицензия не нужна, достаточно самого пакета, из которого альтиум сам использует некоторые модули чтобы вытянуть данные из brd-файла. Вопрос только умеет ли он уже работать с последней версией софта(17.4) или до сих пор интерфейс настроен на старшие версии.

-

Короткая регистрация и скачивайте Free Physical Viewer непосредственно с сайта Cadence. Это будет проще, чем разбираться с целым пакетом, тем более если не проедполагаете в нем работать.

-

Ну так стэка де-факто нет - все приведенные на втором скрине цифры, это параметры слоев по умолчанию, в реальном дизайне так никогда не будет. Так что ищите инфу о стэке референса, на который ориентируетесь.

-

Скрин пригодился бы. Ну и толще... толщина меди имеет значения, равно как и ширина и зазор. Что именно все-таки не совпадает, толщина или ширина? Что с etch-factor? Учтена ли толщина металлизации? Учтена ли солдермаска? Какое Er использовано в расчете?

-

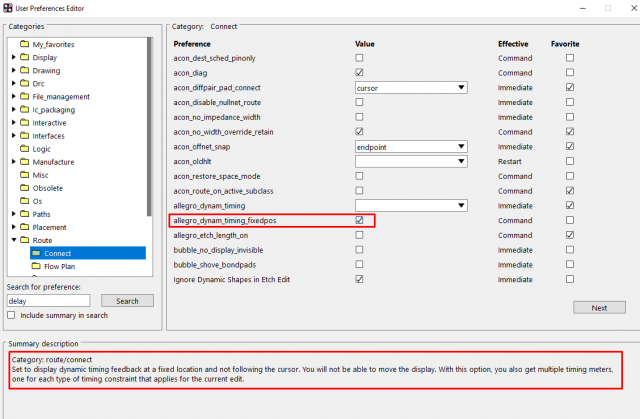

Этот индикатор включается по умолчанию при трассировке/редактированию сигналов с констрейнами длины/времени.

-

Ну вы уточняйте, о чем именно речь... Отображение зазоров? Отображение RDly?

-

??? Разделы СМ не формируются и не задаются, они есть и все. А вот в них уже задаются нужные правила/ограничения дизайна. Ну и вообще намешали понятий - CSet это Constraint Set и его можно создать в каждом из разделв СМ. XNet это eXtended Net и они создаются заданием Espice-модели последовательному компоненту в цепи. Bus - шины - можно создавать как в СМ, так и на схеме, собирая сигналы в шину. Match Group создаются и конфигурятся в разделе Electrical -> Net -> Relative Propagation Delay. Диффпары можно задать уже в схеме и передать в РСВ, а можно в СМ с РСВ.

-

Altium 21.6 и выше

Uree ответил Uladzimir тема в Altium Designer, DXP, Protel

Да не, процес конечно играет свое, но реально быстрее можно в 6 рук плату сделать, чем в две. Просто на самом деле нет никакого усложнения типа разделения зон, проверки кто что сделал, компоновки частей в целое и т.д. На самомо деле просто несколько человек сидят на одной плате и каждый делает что-то свое. Чтобы не мешать друг другу работает динамическая бликоровка зон - вокруг места где я что-то делаю все заблокировано от изменения другими участниками, смотреть на мои действия могут, а что-то менять - нет. Распределение кто, что и где делает исключительно по договоренности, обсудили на уровне "ты слева, я справа, а еще ты в верхней части дизайна" и поехали. Так что не все там там страшно, а ускорение реально есть. Не ровное, конечно, 3 человека не сделают в три раза быстрее, но где-то до момента когда остаются уже глобальные интерконнекты между модулями и глобальные же питания - все ровно разделяется и реально параллельно делается. Если кому интересно, то с программной стороны это реализовано так, что на сервере стартует мастер-дизайн, каждый подключающийся к нему получает локальную временную копию на которой и работает. И в процессе работыидет постоянный обмен сервера с каждым клиентом, данные о локальных изменениях льются на сервер и вносятся в мастер-дизайн, а сервер постоянно апдейтит локальные копии внесенными в него изменениями от остальных участников. Траффик не какой-то космический, но малый пинг важен. -

sigrity powerDC

Uree ответил ed8888 тема в Работаем с трассировкой

Я просто все пытаюсь Вам объяснить, что Вы требуете от софта того, для чего он не предназначен. Этот DCDC не работает на постоянном токе и Сигрити не покажет что и как в нем происходит. Ну что здесь непонятного? Вход DCDC - нагрузка для чего-то, выход - источник VRM для того, что стоит за ним. Что там внутри - это не его епархия, потому что не DC, а импульсный режим. -

sigrity powerDC

Uree ответил ed8888 тема в Работаем с трассировкой

Падения внутри преобразователя не важны, все будет компенсировано ОС. Плотность тока будет смоделирована для постоянного тока, которого до выходного дросселя нет. У меня тот же вопрос - что именно Вы хотите моделировать? Сами преобразователи моделируются SPICE-программами и не в DC-режиме, а в активном. Влияние платы учитывается(если это реально необходимо) в виде паразитных элементов(RLC) в схеме модели. И Sigrity к такому моделированию отношения не имеет. -

Все так, дерево DC можно сделать и даже стОит. Но не преобразователь о котором настойчиво спрашивал ed8888. Он в дереве может быть представлен только как VRM. Я именно это все пытаюсь объяснить...

-

Еще раз - сигрити "не видит" вашу схему, хоть один вывод преобразователя, хоть 15, хоть один элемент, хоть 8 в каком-нибудь мостовом включении. Он моделирует плату, не схему. А конкретно в этом случае выходом DCDC является не чип и не мосфеты, а правый пин силового дросселя с конденсаторами за ним. Именно та точка является источником питания, все что до нее, не является задачей моделирования для сигрити.

-

А сигрити тут вообще не при чем. Это не xSPICE, в котором можно нарисовать схему и посмотреть как она работает. Это 3D солвер, чтобы посмотреть как по плате протекают токи и какие поля возникают. И любой источник в нем источником и должен быть, хоть DCDC, хоть LDO, хоть батарейка. Разнятся только параметры вроде напряжения этого источника, внутреннего сопротивления, выходной индуктивности и т.д. - зависит от уровня детализации модели.

-

Текст выходит за пределы дизайна. Не вставляйте все скопом, по частям, чтобы видеть, что получается. Не так его много, чтоб за пару минут это не сделать.

-

Не, ну доступ-доступом, но откуда у софта вообще берется "желание" удалять свои ключи из реестра? Это же кто-то предусмотрел получается? "Проверить права доступа - если могу - самоудалиться". Ну бред какой-то... Еще могу понять, когда такое делает деинсталлятор, но просто один из программных модулей пакета? Или программисты вообще в код не заглядывают и не знают, что там прописано?:) Как получили его когда-то так и не трогают?

-

Ну это самое не сложное в данном вопросе - только однажды стояла в компе карта от АМД и то, больше потому, что в подарок получил. А так всегда НВидиа и были. А с лицензией подождем-посмотрим. На данный момент то, как работает, в принципе достаточно. Быстрее всегда хорошо, но не сказать, что прям необходимо.