blackfin

-

Постов

4 110 -

Зарегистрирован

-

Победитель дней

3

Сообщения, опубликованные blackfin

-

-

21 minutes ago, dxp said:

Vivado даже в консольном виде загружается очень долго. Тормоз, в общем, и чем дальше, тем больше.

Измерил сейчас время загрузки последней версии Vivado ~11 секунд.

Время, за которое открывается простенький проект ~7 секунд.

Комп: i9, 32GB, SSD, Win10.

-

11 hours ago, Nick_K said:

Увы это немного не то. Это гайд как быстро сделать плату распараллелив работу между отделами.

Это вы, наверное, дальше 2-ой главы не продвинулись:

QuoteChapter 1: Introduction

Chapter 2: Board and Device Planning

Chapter 3: Design Creation with RTL

Chapter 4: Design Constraints

Chapter 5: Design Implementation

Chapter 6: Design Closure

А надо было начинать сразу с 3-ей..

-

-

1 hour ago, Ruslan1 said:

Но я даже не знаю, как правильно назвать микросхему, в которой есть и конфигурируемые ячейки, и железячное ядро в одном флаконе?

Называется SoC:

QuoteZynq-7000S devices feature a single-core ARM Cortex™-A9 processor mated with 28nm Artix®-7 based programmable logic, representing the lowest cost entry point to the scalable Zynq-7000 platform.

-

10 minutes ago, RobFPGA said:

В этом проекте основные частоты 322 и 250 MHz, Speed Grade 2

OK. Спасибо!

-

On 12/1/2021 at 12:03 PM, RobFPGA said:

Внизу пример такой сборки Stratix V.

Если не секрет, на какой частоте работает самая большая DP (т.е., основной функционал) ? И какой Speed Grade у Stratix V ?

-

13 minutes ago, RobFPGA said:

Ага, не получается - на max_depth = 16384 Qu пишет в логах source assignments - "max_depth 16384 Invalid assignment name",

И судя по доками на память в S10 (после внимательного повторного чтения) не зря так пишет -

Вот те и "M20K"

Да, похоже, что M20K не получить. Тоже посмотрел нет-лист в своем проекте, везде блоки по 2048 бит плюс большой MUX.

-

1 hour ago, RobFPGA said:

Первый прикол как всегда с памятью - вместо генерации SDP памяти 16Кx20 из блоков в 16К x 1 бит Qu упорно лепит память из блоков 2к x 20 вставляя на выходе огромны мукс. Который естественно валит времянку. Причем как при описании из RTL так и из IP корки памяти

Есть же атрибуты: (* ramstyle = "M20K", max_depth = 16384 *)

Или с ними тоже не получается?

-

29 minutes ago, Kostochkin said:

Мне надо, чтобы этот файл анализировался только на этапе имплементации.

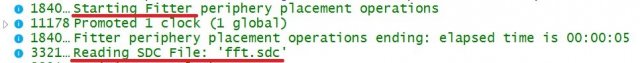

Если почитать логи синтезатора, то видно, что файл *.sdc синтезатор не использует.

Файл *.sdc Quartus загружает только после старта Fitter'а:29 minutes ago, Kostochkin said:Если что-то изменить, то не надо заново делать синтез, а только имплементацию.

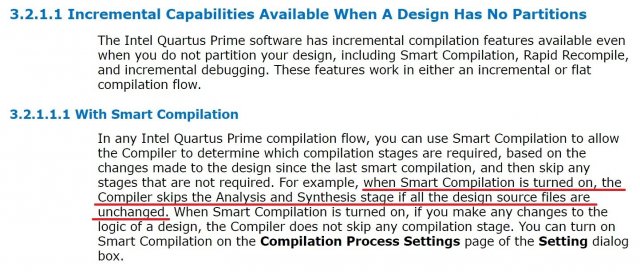

IMHO, чтобы не делать заново синтез, нужно просто включить опцию Smart Compilation (или Incremental Compilation):

-

39 minutes ago, Джоконда said:

А почему ... ?

Может ... ? Может ... ?

Надежность, дублирование, троирование...

ТуамосесДжоконда как всегда в своём репертуаре.. :)Коллеги! Хватит кормить тролля!

-

51 minutes ago, Mad_kvmg said:

... последние релизы CFExpress полностью утилизируют PCIe шину, обеспечивая отличную производительность.

IMHO, если в FPGA есть шина PCIe (или SATA) и есть желание выделить несколько lanes под NVMe, то лучше M.2 2242 SSD

Сейчас разъем под SSD в форм-факторе M.2 есть практически на всех современных мат.платах, так что проблем с покупкой в ближайшие годы не возникнет.

Ну и цена будет падать по причине больших тиражей производства подобных дисков.

-

38 minutes ago, maxics said:

Один вход, два выхода. таких микросхем нужно 30.

Два входа, четыре выхода. Таких микросхем нужно 15.

-

-

28 minutes ago, _sda said:

Около того.

Путаетесь в показаниях.. :)

On 11/20/2021 at 2:11 PM, _sda said:... есть две шины комплексных данных разрядностью 24 бита RE и 24 бита IM в каждой шине.

Две шины комплексных данных по 24 бита, это ~24,5 бит для вещественной огибающей. Так что ДД будет примерно: 24,5*6,02 + 1,76 ≈ 150 дБ.

Видимо, 50 дБ где-то потерялись по дороге.. :)

-

Всё просто:

1. CORDIC'ом преобразуем оба числа в показательную форму:z1 = x1 + y1*i = r1*exp(i*φ1);

z2 = x2 + y2*i = r2*exp(i*φ2);

2. Вычисляем корни обоих чисел:

sqrt(z1) = sqrt(r1)*exp(i*φ1/2);

sqrt(z2) = sqrt(r2)*exp(i*φ2/2);

3. Находим корень произведения:

sqrt(z1*z2) = sqrt(z1)*sqrt(z2) = sqrt(r1)*sqrt(r2)*exp(i*φ1/2+i*φ2/2);

4. При необходимости, CORDIC'ом преобразуем полученный корень произведения в алгебраическую форму:

Re(sqrt(z1*z2)) + i*Im(sqrt(z1*z2)) = sqrt(r1)*sqrt(r2)*[cos(φ1/2+φ2/2) + i*sin(φ1/2+φ2/2)]; -

11 minutes ago, _sda said:

Для извлечения корня из комплексного числа нужно выполнить три извлечения корня из вещественного числа.

Это ещё зачем? "Нормальные герои всегда идут в обход?" ;-)

-

5 minutes ago, _sda said:

... а как на ваш взгляд велика ли будет погрешность?

Странный вопрос.. Сколько бит оставите в вычисленных корнях, столько и будет.

Можете вычислять оба корня SQRT(z1) и SQRT(z2) с 24-х битной точностью в формате с фиксированной запятой: 12 целых + 12 дробных разрядов.

-

14 hours ago, _sda said:

Нужно вычислить SQRT(z1 * z2). Разрядность шин x1,x2,y1,y2 равна 24 бита, если бы было меньше то этот вопрос скорее всего не появился бы.

Так в чем проблема? Алгебра за 11-й класс:

SQRT(z1 * z2) = SQRT(z1) * SQRT(z2).

Оба корня справа будут иметь разрядность: 24/2 = 12 бит

-

26 minutes ago, _sda said:

Не нужен мне "просто модуль комплексного числа", почитайте пожалуйста условие внимательней.

Для начала, перепишите свой первый пост на нормальном языке используемом в алгебре за 11-й класс. А то не понятно, "кто на ком стоял".. ))

Пока что, мне понятно лишь то, что есть два комплексных числа z1 и z2:

z1 = x1 + y1*i;

z2 = x2 + y2*i;

Что вам нужно с ними сделать мне пока не понятно..

-

Можете сами скачать: xapp1151_Param_CAM

-

On 11/16/2021 at 4:04 PM, quato_a said:

ПЛИС XIlinx 7-series. Нужно принимать lvds видео поток и возможно разное разрешение от 640х480 до 1920х1080, а следовательно, разный входной клок от 25 до 148,5 МГц.

У Xilinx'а есть готовая IP Core для приема видео потоков: PG071.

Для приема видео в формате SD (PAL, NTSC) в этой IP Core используется 11 кратная передискретизация входного видео потока:

QuoteThe 270 Mbps bit rate of SD-SDI is too slow for the transceivers in Xilinx FPGAs to receive directly. Therefore, when using a Xilinx transceiver to receive SD-SDI, the transceiver is locked to its reference clock and oversamples the SD-SDI bit stream by a factor of 11X.

-

9 minutes ago, rloc said:

Подумываю, не слишком ли скромно подумал о -170дБн/Гц, может поднять до -175дБн/Гц?

А что это за АЦП с ENOB = 170/6 = 28 бит на 100 МГц ?

-

1 hour ago, rloc said:

Коэффициенты деления 2, 4, 8 ..., чтобы расширить диапазон вниз до единиц кГц. Для тестирования современных АЦП не хватает -170дБн/Гц по ФШ/АШ на 100МГц чтобы достоверно оценить SNR.

HMC988 ?

Quote-170 dbc/Hz floor @ 100 MHz output

-

10 minutes ago, dxp said:

Нельзя говорить "толстым", надо - "бодипозитивным". А то они могут обидеться и указать на отсутствие терпимости.

Про толстых - телосложение.

Про худых - теловычитание.

Vivado уменьшить время компиляции

в Работаем с ПЛИС, области применения, выбор

Опубликовано · Пожаловаться

Проблема, на мой взгляд, в HDD.

У меня на домашнем компе с механическим HDD и Core-i7 Vivado 20.1 загружается за полторы минуты.

Есть еще комп на работе, у которого Win10 установлена на механическом HDD, а Vivado 21.2 на NVMe. И на нем Vivado тоже загружается больше минуты.