blackfin

-

Постов

4 110 -

Зарегистрирован

-

Победитель дней

3

Сообщения, опубликованные blackfin

-

-

А в настройках IP Core PLL входную частоту поправили?

-

On 6/28/2022 at 11:02 PM, Tpeck said:

Или простой - это не примитивный?

Всякий примитивный полином является простым, но не всякий простой полином является примитивным.

См. определение 4.5.5 на стр. 103.

-

-

Опубликовано · Изменено пользователем makc

Переход на личности удалён · Пожаловаться34 минуты назад, Maxim_S сказал:О чем и речь, какая "ассоциация"? нас затащили в 17-й век...

Никто вас никуда не затаскивал. Вы сами себя затащили.. Никто же не мешал вам создать "в гараже" IT-фирму и удивить человечество своими научно-техническими достижениями..

-

On 6/23/2022 at 7:05 AM, byRAM said:

Если речь идёт о стробоскопе, то там и 1 триллион вполне достижим, но АЦП с тактовой 200 ГГц - это бред.

Не нашел по ссылке про стробоскоп. Похоже, честные 256 GSa/s: Infiniium UXR

QuoteWith four channels of simultaneous 110 GHz of bandwidth, each concurrently sampling at a staggering 256 GSa/s, Infiniium UXR delivers the world-leading performance, ultra-low noise and high signal fidelity necessary for engineers and scientists to truly see and understand even the fastest phenomena – enabling you to more quickly develop the next generation of technology and research.

-

On 6/19/2022 at 11:34 AM, baumanets said:

Непередаваемая легкость бизнеса на продажах IP-блоков, создала в РФ схему.

Причём разница между деньгами государства и ценой блока просто колоссальная, она даже перекрывала далеко не один запуск на импортных ФАБах.

Можете озвучить ценник на импортные IP-блоки? Ну, чтобы можно было оценить "перспективы микроэлектроники в России".

-

On 6/17/2022 at 5:46 PM, cdg said:

прошу помощи скачать zip архив исходников для xapp1168

Скачивается без проблем: xapp1168

-

-

8 hours ago, dmitry-tomsk said:

Подскажите, пожалуйста, в 2022.1 эту ошибку исправили или также патч требуется?

Судя по всему, в версии 2022.1 поломали комплексный умножитель - на выходе умножителя нули.

-

17 hours ago, Krys said:

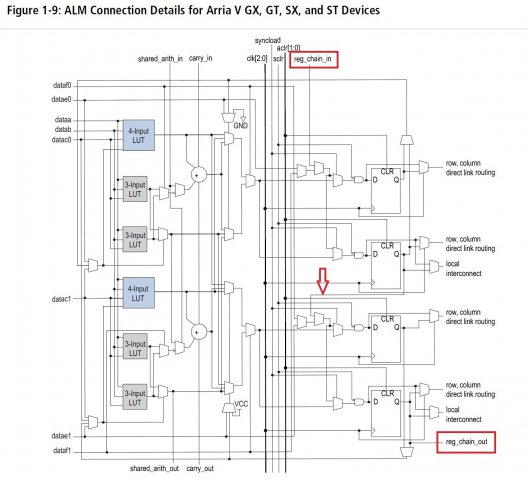

Плисина Ария 5. Не получается синтезатору запихать выходной регистр внутрь DSP-блока.

Была похожая тема:

-

9 minutes ago, seniorandre said:

Ну так вы перечитайте статью, где вы там увидели прямоугольную частотную характеристику. Мы имеем sinc частотную характеристику, которую дает прямоугольное скользящее окно во временной области.

Wiki: Sinc filter

In signal processing, a sinc filter is an idealized filter that removes all frequency components above a given cutoff frequency, without affecting lower frequencies, and has linear phase response. The filter's impulse response is a sinc function in the time domain, and its frequency response is a rectangular function.

The name "sinc filter" is applied also to the filter shape that is rectangular in time and a sinc function in frequency, as opposed to the ideal low-pass sinc filter, which is sinc in time and rectangular in frequency. In case of confusion, one may refer to these as sinc-in-frequency and sinc-in-time, according to which domain the filter is sinc in.

-

1 hour ago, whale said:

Цап на резисторах, 8 ног

На 8-ми выводах можно сделать два 8-ми битных ЦАП'а - R2R + ШИМ: Hybrid PWM/R2R DAC improves on both

-

13 hours ago, amaora said:

Передаётся прошивка объёмом ~100Кб. Нужна устойчивость к потере до ~50% передаваемых данных. Объем передаваемых данных можно увеличить в 2-3 раза.

8 hours ago, amaora said:Вопрос не в этом, хотелось оценить возможность применения избыточного кодирования.

Для кодов БЧХ, если нужна "устойчивость к потере до ~50% передаваемых данных", то объем передаваемых данных нужно увеличить в 4-6 раз.

Вот примеры нескольких кодов БЧХ исправляющих ~50% ошибок:

t = 3: code = (15,5,7)

t = 6: code = (31,6,13)

t = 10: code = (63,18,21)

t = 21: code = (127,29,43)

t = 31: code = (255,55,63)

t = 59: code = (511,112,119)

t = 111: code = (1023,218,223)

t = 215: code = (2047,419,431)

t = 413: code = (4095,826,827)

t = 766: code = (8191,1522,1533)

t = 1495: code = (16383,2978,2991)

t = 2905: code = (32767,5809,5811)

t = 5610: code = (65535,11211,11221)Где t - количество исправляемых ошибок.

То есть, для кода (65535,11211,11221) длина сообщения равна 11211 бит, а длина кода равна 65535 бит.Это равносильно увеличению объема передаваемых данных в 65535/11211 = 5,85 раза.

-

5 hours ago, iiv said:

как я понимаю, при передаче приходится испускать 10-20 Ватт.

Brand New Starlink Dish To Reduce Power Yet Improve Efficiency & Density:

Quote

QuoteThis stands at 2.44 Watts, almost half of the old terminals' output of 4.03 Watts.

-

6 minutes ago, makc said:

Однако подобного происходящему сейчас мировая история не знала и поэтому все прогнозы стоят сейчас очень мало.

Знала и довольно давно:

QuoteПереход Цезаря через Рубикон — событие, состоявшееся 10 января 49 года до н.э.[1] и явившееся началом гражданской войны между Цезарем и Помпеем в Риме. Река Рубикон служила границей между италийской областью Умбрия и провинцией Цизальпинская Галлия. Галлия была законной провинцией Цезаря, где он имел право распоряжаться войсками, ввод войск на территорию собственно Италии являлся, по римским законам, мятежом. Переход Цезаря с войсками через Рубикон имел не только грандиозное историческое значение, знаменуя падение Римской Республики, но и оставил большой след в культуре, с ним связаны две крылатые фразы: «перейти Рубикон» (означает решительный поступок, прохождение «точки невозврата».)[2] и «Жребий брошен!» (лат. Alea jacta est!,означает: «выбор сделан», либо «рискнуть всем ради великой цели», а также используется, чтобы подчеркнуть необратимость происходящего.).

-

32 minutes ago, Lmx2315 said:

Где вы увидели в первом сообщении что у них КЧХ, я не вижу. А АЧХ получается как модуль КЧХ , фарш назад не провернуть.

ФЧХ можно легко вычислить, зная АЧХ. Учите мат-часть: Соотноше́ния Кра́мерса — Кро́нига.

PS. Нет, я был не прав..

Зная Re[K(w)] можно вычислить Im[K(w)] и наоборот. С модулем K(w) такой фокус, кажется, не пройдет.

PPS. Но в любом случае, судя по графику из первого поста, ФЧХ известна.

-

10 minutes ago, Lmx2315 said:

имхо по одной АЧХ нельзя, нужно ещё ФЧХ.

Можно. Функция КЧХ является аналитической. Ваш, КО.

-

-

7 minutes ago, RobFPGA said:

Результат очень красноречивый

OK.

Вот MTBF в пустом проекте на K3UP-2-i:

+----------------+-----------------+----------------+ | Structure Type | Total in Design | MTBF | +----------------+-----------------+----------------+ | Synchronizers | 16 | 2.96e+03 years | | FIFOs | 0 | --- | | Overall | 16 | --- | +----------------+-----------------+----------------+ +----------+----------------+------------------------+-----------------------+-------------------------+----------------+------------------+---------------+-------------------+ | CDC Path | MTBF | Data Toggle Rate(Mtrs) | Data Sample Rate(Mhz) | Total Settling Time(ns) | Sending Domain | Receiving Domain | Number Stages | CDC Net Name | +----------+----------------+------------------------+-----------------------+-------------------------+----------------+------------------+---------------+-------------------+ | 1 | 1.65e+08 years | 3.36 | 690 | 1.81 | s_axis_aclk | m_axis_aclk | 2 | p_0_in1_in__0[0] | | 2 | 7.55e+03 years | 3.4 | 690 | 1.38 | s_axis_aclk | m_axis_aclk | 2 | p_0_in1_in__2[0] | | 3 | 4.01e+04 years | 3.64 | 690 | 1.46 | s_axis_aclk | m_axis_aclk | 2 | p_0_in1_in__4[0] | | 4 | 1.55e+06 years | 2.84 | 690 | 1.57 | s_axis_aclk | m_axis_aclk | 2 | p_0_in1_in__6[0] | | 5 | 3.9e+04 years | 2.45 | 690 | 1.46 | s_axis_aclk | m_axis_aclk | 2 | p_0_in1_in__8[0] | | 6 | 1.51e+06 years | 2.54 | 690 | 1.55 | s_axis_aclk | m_axis_aclk | 2 | p_0_in1_in__10[0] | | 7 | 2.01e+08 years | 3.64 | 690 | 1.79 | s_axis_aclk | m_axis_aclk | 2 | p_0_in1_in__12[0] | | 8 | 6.5e+03 years | 3.81 | 690 | 1.34 | s_axis_aclk | m_axis_aclk | 2 | p_0_in1_in__14[0] | | 9 | UNDEFINED | ZERO* | 714 | 1.54 | m_axis_aclk | s_axis_aclk | 2 | p_0_in1_in__15[0] | | 10 | UNDEFINED | ZERO* | 714 | 1.76 | m_axis_aclk | s_axis_aclk | 2 | p_0_in1_in__1[0] | | 11 | UNDEFINED | ZERO* | 714 | 1.63 | m_axis_aclk | s_axis_aclk | 2 | p_0_in1_in__3[0] | | 12 | UNDEFINED | ZERO* | 714 | 1.63 | m_axis_aclk | s_axis_aclk | 2 | p_0_in1_in__5[0] | | 13 | UNDEFINED | ZERO* | 714 | 1.62 | m_axis_aclk | s_axis_aclk | 2 | p_0_in1_in__7[0] | | 14 | UNDEFINED | ZERO* | 714 | 1.79 | m_axis_aclk | s_axis_aclk | 2 | p_0_in1_in__9[0] | | 15 | UNDEFINED | ZERO* | 714 | 1.75 | m_axis_aclk | s_axis_aclk | 2 | p_0_in1_in__11[0] | | 16 | UNDEFINED | ZERO* | 714 | 1.61 | m_axis_aclk | s_axis_aclk | 2 | p_0_in1_in__13[0] | +----------+----------------+------------------------+-----------------------+-------------------------+----------------+------------------+---------------+-------------------+ * Summary: Overall Synchronizer MTBF:2.96e+03 years

Только не понял, почему для m_axis_* -> s_axis_* Toggle Rate равны ZERO*.

-

1 hour ago, TRILLER said:

Надеюсь, что Вы по большей части работали не с xilinx.

Зря надеетесь.. :)

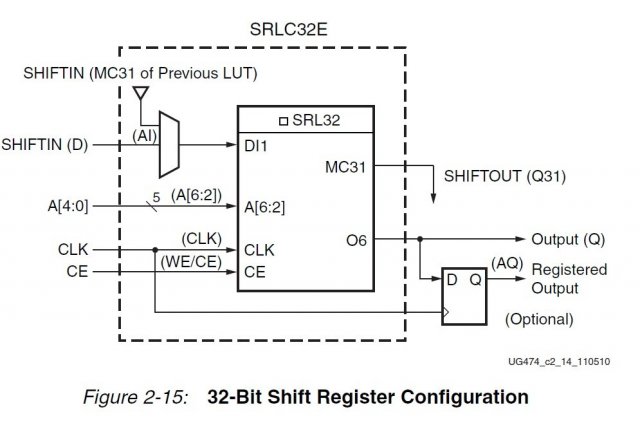

1 hour ago, TRILLER said:На моей памяти никогда не было "внутреннего" интерконнекта между триггерами у них.

Да, всё так. Хотя на мой взгляд, логичнее было бы сделать на SRLC32E:

Но Виваде, конечно, виднее.. :)

----------------------------------

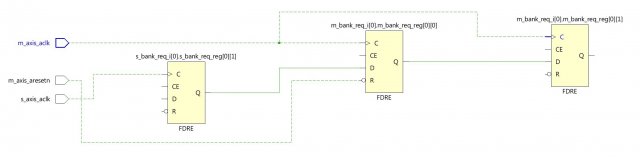

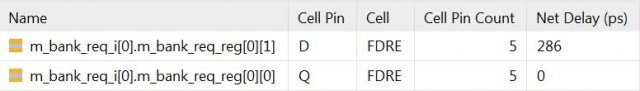

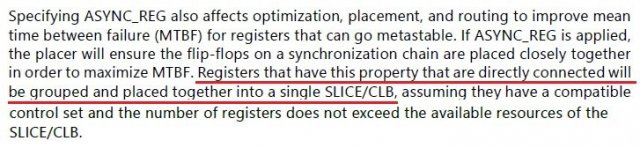

Посмотрел в рабочем проекте как соединены триггера с атрибутом ASYNC_REG:

Да, регистры соединены через интерконнект:

Но задержка всего 286 ps:

-

34 minutes ago, Nick_K said:

Проблема вылазит позже, так как разные выходы/входы Слайса подключены к матрице интерконнекта по разному и там задержки могут быть и по 100-200 ps запросто.

Задержки на выходе цепочки ASYNC регистров к CDC отношения уже не имеют, а потому на величину MTBF никак не влияют.

А разговор сейчас именно про влияние задержки между регистрами в схеме CDC на величину MTBF.

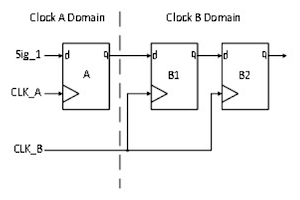

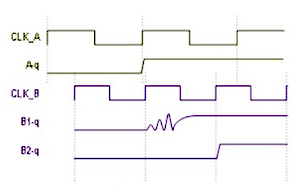

Вот схема:

А вот диаграмма:

Если провод с выхода B1-q будет длинным (с большой задержкой), то колебания на выходе B1-q сместятся вправо на величину этой задержки.

При этом, вероятность того, что триггер B2 тоже окажется в метастабильном состоянии увеличится, так как на входе d триггера B2 будет нестабильное значение.

-

Just now, RobFPGA said:

Это понятно, но задержки все равно гуляют, матрица роутинга не резиновая

Хм.. Я всегда считал, что роутинг реализован между SLICE'ами. Внутри SLICE/CLB всё жестко соединено проводами и задержки внутри одного SLICE/CLB не больше сотни пс.

-

-

13 hours ago, Мур said:

Замучила метастабильность по данным?

Готовых решений полно на edn:

Synchronizer techniques for multi-clock domain SoCs & FPGAs10 design issues to avoid during clock domain crossing

Get those clock domains in sync

И в конце каждой статьи есть ещё ссылки на похожие статьи по этой же теме.

Непонятка с описанием клока в Квартусе

в Работаем с ПЛИС, области применения, выбор

Опубликовано · Пожаловаться

Можно попробовать удалить IP Core PLL из проекта (не меняя самого кода проекта), и создать новую PLL с чистого листа, с тем же именем и с теми же параметрами..