blackfin

-

Постов

4 110 -

Зарегистрирован

-

Победитель дней

3

Сообщения, опубликованные blackfin

-

-

28 minutes ago, Nick_K said:

А при чём тут инициализация?

Кстати, да. При чем тут инициализация? До вас о ней тут никто не упоминал. Речь, напомню, шла про отсутствие дефолтных кейсов. Про инициализацию вы запели чтобы увести разговор в сторону и заболтать вопрос. Впрочем, это ваша обычная манера.. :)

-

3 hours ago, Nick_K said:

Да я точно пишу RTL.

Серьёзно? Ну, тогда Synopsys пишет, видимо, на чем-то другом.. :):):)

-

12 minutes ago, syoma said:

Например? Что вас конкретно интересует?

Да хотя бы FFT.. :)

Сможет Матлаб-hdl "из коробки" посчитать FFT на 4096 точек на каком-нить XCVU3P за 1,5 мкс? -

On 7/28/2021 at 5:03 PM, Grizzly said:

У ЛЧМ АКФ будет sinc - 13.5 дБ первый боковой лепесток.

Только нужно определиться с тем, что мы понимаем под термином "первый боковой лепесток". :)

После умножения функции sinc(γTt/2) на функцию cos(ω0t) (из учебника на стр. 72-73) главный лепесток функции sinc() распадется на несколько лепестков имеющих большую амплитуду и меньшую ширину.

Например, при соотношении частот Fhi = 2*Flo главный лепесток функции sinc() превратится в семь более узких лепестков.

-

9 minutes ago, Мур said:

FFT на такое количество точек это монстр!

Нее.. Монстры вот тут:

:)

-

14 hours ago, Мур said:

Все сделаю на 200!!!

200 MHz на CYCLONE V EX С8 ???

Да вы оптимист!.. :)

Вот результат синтеза FFT на 64k точек для 5CEFA9F23C7:

+-----------------------------------------------------------------------------------+ ; Fitter Summary ; +---------------------------------+-------------------------------------------------+ ; Fitter Status ; Successful - Tue Jul 27 19:53:33 2021 ; ; Top-level Entity Name ; fft ; ; Family ; Cyclone V ; ; Device ; 5CEFA9F23C7 ; ; Timing Models ; Final ; ; Logic utilization (in ALMs) ; 1,801 / 113,560 ( 2 % ) ; ; Total registers ; 4314 ; ; Total block memory bits ; 2,713,752 / 12,492,800 ( 22 % ) ; ; Total RAM Blocks ; 337 / 1,220 ( 28 % ) ; ; Total DSP Blocks ; 6 / 342 ( 2 % ) ; ; Total PLLs ; 1 / 8 ( 13 % ) ; +---------------------------------+-------------------------------------------------+ +----------------------------------------------------------------------------------------------------------------+ ; Slow 1100mV 0C Model Fmax Summary ; +------------+-----------------+--------------------------------------------------------------------------+------+ ; Fmax ; Restricted Fmax ; Clock Name ; Note ; +------------+-----------------+--------------------------------------------------------------------------+------+ ; 202.18 MHz ; 202.18 MHz ; pll_inst|pll_inst|altera_pll_i|general[0].gpll~PLL_OUTPUT_COUNTER|divclk ; ; +------------+-----------------+--------------------------------------------------------------------------+------+

-

2 minutes ago, my504 said:

Ошибочность формулировки принимается.

... что Вы можете сказать относительно вопроса №2?

Скажу, что он тоже сформулирован с ошибками.. :)

-

4 minutes ago, my504 said:

Я в каком то месте утверждал, что мне требуется медианное значение модулей?

Вот тут:

21 hours ago, my504 said:Нужно найти медианное значение амплитуды.

21 hours ago, my504 said:... для этого достаточно найти ... и из них получить искомую амплитуду (модуль)?

-

4 minutes ago, my504 said:

Я не сомневаюсь в результате математических вычислений.

Тогда не употребляйте слово Медиа́на.. Ищите то, что вам нужно, а не то, что красиво звучит.. :)

-

7 hours ago, my504 said:

А откуда берется утверждение, что 3,01085 - верно, а 1 - нет?

Это результат вычислений:

1. Вычисляем значения модулей для всех векторов и сохраняем их в массиве.2. Сортируем массив по возрастанию.

3. Находим медианное значение в массиве модулей.

Вот отсортированный массив модулей всех девяти векторов:

1.4142 2.0616 2.0616 3.0185 3.0185 4.0078 4.0078 5.0040 5.0040

Wiki:

QuoteМедиа́на набора чисел — число, которое находится в середине этого набора, если его упорядочить по возрастанию ...

-

1 minute ago, my504 said:

Откуда взято это условие? Или это просто пример, когда я неправ?

Да, это просто пример.

-

21 hours ago, my504 said:

Простой вопрос №1.

Имеется некий массив двумерных векторов (окно комплексных значений сигнала). Нужно найти медианное значение амплитуды.

Правильно ли я понимаю, что для этого достаточно найти медианные значения Re и Im компонент и из них получить искомую амплитуду (модуль)?

Нет, не правильно.

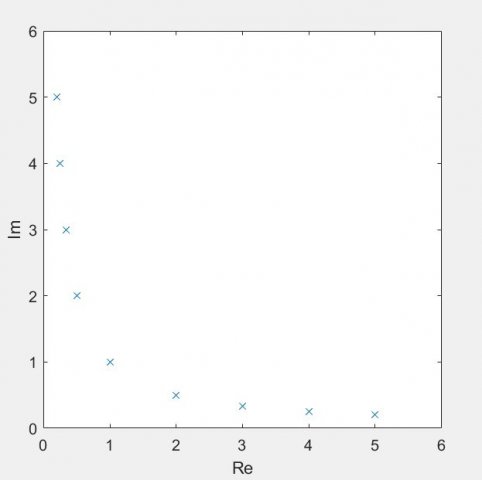

Чтобы в этом убедиться, достаточно рассмотреть массив из девяти векторов симметрично расположенных относительно прямой Im = Re, причем, вершины этих векторов лежат на кривой, заданной уравнением гиперболы: Im = 1/Re.

Вот график вершин этих векторов на комплексной плоскости:

Очевидно, что значение медианы по обеим координатам Im и Re равно 1,0.

Также очевидно, что значение медианы для модуля, равное 3.0185, не совпадает со значением модуля для медианы, равного abs(1+j) = 1.4142.

-

4 minutes ago, Мур said:

Поставил конвейер из 2х регистров(200МГц) на шину адреса BRAM.

Так поставьте ещё два регистра на выходе q_b.

И включите защелки по выходу:

48 minutes ago, Мур said:Убраны защелки по выходам и вижу выход данных с задержкой в 1 тик.

-

2 minutes ago, Мур said:

... латентность в 1 тик 100МГц

Для RAM размером 192k нужна латентность чтения ~3-5 тактов.

-

22 minutes ago, Мур said:

Но та же хрень! 85.14МГц

А для самой BRAM-памяти какая задана латентность?

-

52 minutes ago, Мур said:

Я заблуждаюсь?

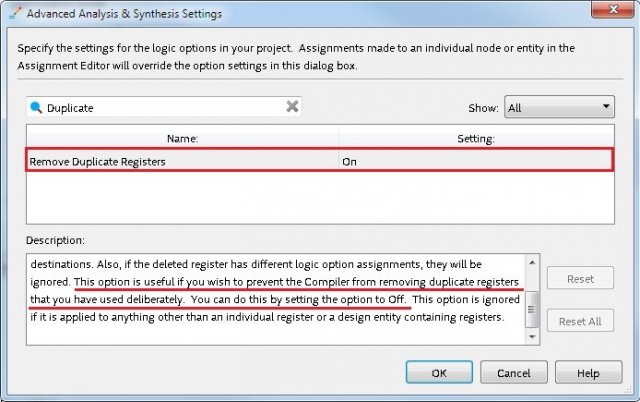

Перевожу с языка оригинала:

Remove Duplicate Registers ? = Off !!!.

Удалять дубликаты регистров ? = Нет !!!

-

3 minutes ago, Мур said:

По умолчанию уже активно!...

Вы что, читать не умеете? :)

Чтобы Quartus не удалял продублированные регистры, эту опцию нужно выключить: Remove Duplicate Registers = Off.

-

-

2 minutes ago, Мур said:

Я так трактовал вашу подсказку выше

Это была никакая не подсказка. У меня в проекте модуль счетчика вообще никуда не был подключен. Это было нужно, чтобы оценить частоту самого счетчика.

-

20 minutes ago, Мур said:

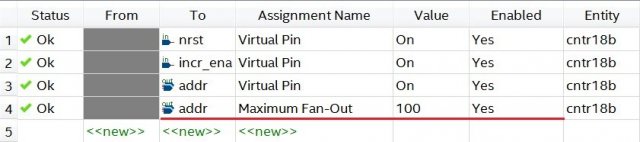

С 10го захода QII таки запомнил мою просьбу!

А почему addr_mem_b объявлены виртуальными? Они что, вообще никуда не подключены??? :)

Виртуальными обычно назначают пины модуля, когда хотят оценить частоту работы модуля без учета влияния пинов IO.

Это же не ваш случай.

22 minutes ago, Мур said:Обычно тупо все сбрасывала.

Нужно было нажать иконку с дискетой.

-

-

1 hour ago, Мур said:

CYCLONE V EX С8 86МГц.

Что-то не так в консерватории.

Вот отчет STA для 18-ти битного счетчика со сбросом и сигналом разрешения счета:Flow Summary report for cntr18b +-----------------------------------------------------------------------------------+ ; Flow Summary ; +---------------------------------+-------------------------------------------------+ ; Flow Status ; Successful - Sun Jul 25 19:12:00 2021 ; ; Top-level Entity Name ; cntr18b ; ; Family ; Cyclone V ; ; Device ; 5CEBA5U19C8 ; ; Timing Models ; Final ; ; Logic utilization (in ALMs) ; 20 / 29,080 ( < 1 % ) ; ; Total registers ; 18 ; ; Total pins ; 1 / 224 ( < 1 % ) ; ; Total virtual pins ; 20 ; +---------------------------------+-------------------------------------------------+ +--------------------------------------------------+ ; Slow 1100mV 0C Model Fmax Summary ; +------------+-----------------+------------+------+ ; Fmax ; Restricted Fmax ; Clock Name ; Note ; +------------+-----------------+------------+------+ ; 318.78 MHz ; 318.78 MHz ; clk ; ; +------------+-----------------+------------+------+

-

1 hour ago, Мур said:

Писал, как обычно, очередной автомат чтения памяти с 18-ти разрядной шиной адреса и после функциональной отладки и сборки TQ оценил недостаточность резвости.

Как обычно, не хватает подробностей. :)

1. Что за кристалл?

2. Какой у него Speed Grade?3. Какая в итоге получилась частота?

4. Что за память?

5. Почему её нельзя читать burst'ами? -

14 hours ago, gosha-z said:

По сравнению латтисом- CSI-2 TX бесплатно

FYI: Бесплатный доступ к IP-ядрам MIPI CSI2 в обновлённой версии Vivado от Xilinx

Как исправить код? Или что добавить?

в Языки проектирования на ПЛИС (FPGA)

Опубликовано · Пожаловаться

Ну меня повеселили вот эти ваши откровения:

И это при том, что в мануале на DC на стр. 82 сам Synopsys приводит пример использования default в операторе case и дает пояснения по синтезу latches.

PS. Уж не знаю, какой вы разработчик ASIC'ов, но в элементарных вещах вы явно плаваете.. :)