blackfin

-

Постов

4 126 -

Зарегистрирован

-

Победитель дней

3

Сообщения, опубликованные blackfin

-

-

39 minutes ago, Джоконда said:

А почему ... ?

Может ... ? Может ... ?

Надежность, дублирование, троирование...

ТуамосесДжоконда как всегда в своём репертуаре.. :)Коллеги! Хватит кормить тролля!

-

51 minutes ago, Mad_kvmg said:

... последние релизы CFExpress полностью утилизируют PCIe шину, обеспечивая отличную производительность.

IMHO, если в FPGA есть шина PCIe (или SATA) и есть желание выделить несколько lanes под NVMe, то лучше M.2 2242 SSD

Сейчас разъем под SSD в форм-факторе M.2 есть практически на всех современных мат.платах, так что проблем с покупкой в ближайшие годы не возникнет.

Ну и цена будет падать по причине больших тиражей производства подобных дисков.

-

38 minutes ago, maxics said:

Один вход, два выхода. таких микросхем нужно 30.

Два входа, четыре выхода. Таких микросхем нужно 15.

-

-

28 minutes ago, _sda said:

Около того.

Путаетесь в показаниях.. :)

On 11/20/2021 at 2:11 PM, _sda said:... есть две шины комплексных данных разрядностью 24 бита RE и 24 бита IM в каждой шине.

Две шины комплексных данных по 24 бита, это ~24,5 бит для вещественной огибающей. Так что ДД будет примерно: 24,5*6,02 + 1,76 ≈ 150 дБ.

Видимо, 50 дБ где-то потерялись по дороге.. :)

-

Всё просто:

1. CORDIC'ом преобразуем оба числа в показательную форму:z1 = x1 + y1*i = r1*exp(i*φ1);

z2 = x2 + y2*i = r2*exp(i*φ2);

2. Вычисляем корни обоих чисел:

sqrt(z1) = sqrt(r1)*exp(i*φ1/2);

sqrt(z2) = sqrt(r2)*exp(i*φ2/2);

3. Находим корень произведения:

sqrt(z1*z2) = sqrt(z1)*sqrt(z2) = sqrt(r1)*sqrt(r2)*exp(i*φ1/2+i*φ2/2);

4. При необходимости, CORDIC'ом преобразуем полученный корень произведения в алгебраическую форму:

Re(sqrt(z1*z2)) + i*Im(sqrt(z1*z2)) = sqrt(r1)*sqrt(r2)*[cos(φ1/2+φ2/2) + i*sin(φ1/2+φ2/2)]; -

11 minutes ago, _sda said:

Для извлечения корня из комплексного числа нужно выполнить три извлечения корня из вещественного числа.

Это ещё зачем? "Нормальные герои всегда идут в обход?" ;-)

-

5 minutes ago, _sda said:

... а как на ваш взгляд велика ли будет погрешность?

Странный вопрос.. Сколько бит оставите в вычисленных корнях, столько и будет.

Можете вычислять оба корня SQRT(z1) и SQRT(z2) с 24-х битной точностью в формате с фиксированной запятой: 12 целых + 12 дробных разрядов.

-

14 hours ago, _sda said:

Нужно вычислить SQRT(z1 * z2). Разрядность шин x1,x2,y1,y2 равна 24 бита, если бы было меньше то этот вопрос скорее всего не появился бы.

Так в чем проблема? Алгебра за 11-й класс:

SQRT(z1 * z2) = SQRT(z1) * SQRT(z2).

Оба корня справа будут иметь разрядность: 24/2 = 12 бит

-

26 minutes ago, _sda said:

Не нужен мне "просто модуль комплексного числа", почитайте пожалуйста условие внимательней.

Для начала, перепишите свой первый пост на нормальном языке используемом в алгебре за 11-й класс. А то не понятно, "кто на ком стоял".. ))

Пока что, мне понятно лишь то, что есть два комплексных числа z1 и z2:

z1 = x1 + y1*i;

z2 = x2 + y2*i;

Что вам нужно с ними сделать мне пока не понятно..

-

Можете сами скачать: xapp1151_Param_CAM

-

On 11/16/2021 at 4:04 PM, quato_a said:

ПЛИС XIlinx 7-series. Нужно принимать lvds видео поток и возможно разное разрешение от 640х480 до 1920х1080, а следовательно, разный входной клок от 25 до 148,5 МГц.

У Xilinx'а есть готовая IP Core для приема видео потоков: PG071.

Для приема видео в формате SD (PAL, NTSC) в этой IP Core используется 11 кратная передискретизация входного видео потока:

QuoteThe 270 Mbps bit rate of SD-SDI is too slow for the transceivers in Xilinx FPGAs to receive directly. Therefore, when using a Xilinx transceiver to receive SD-SDI, the transceiver is locked to its reference clock and oversamples the SD-SDI bit stream by a factor of 11X.

-

9 minutes ago, rloc said:

Подумываю, не слишком ли скромно подумал о -170дБн/Гц, может поднять до -175дБн/Гц?

А что это за АЦП с ENOB = 170/6 = 28 бит на 100 МГц ?

-

1 hour ago, rloc said:

Коэффициенты деления 2, 4, 8 ..., чтобы расширить диапазон вниз до единиц кГц. Для тестирования современных АЦП не хватает -170дБн/Гц по ФШ/АШ на 100МГц чтобы достоверно оценить SNR.

HMC988 ?

Quote-170 dbc/Hz floor @ 100 MHz output

-

10 minutes ago, dxp said:

Нельзя говорить "толстым", надо - "бодипозитивным". А то они могут обидеться и указать на отсутствие терпимости.

Про толстых - телосложение.

Про худых - теловычитание.

-

11 hours ago, Volkov said:

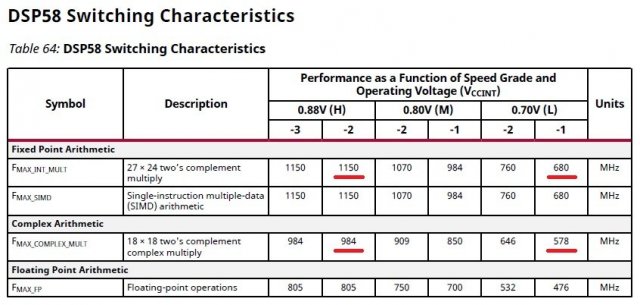

В общем за 2000 долларов (VM1102) 464 умножителя. И все это с ддр4, и вряд ли оно там на гигагерце будет работать.

Versal VC1902 сливает по частоте даже US+ Kintex'ам: Performance and Resource Utilization for Fast Fourier Transform

VC1902 - 1024pts @ 560 MHz

KU13P - 1024pts @ 642 MHz

PS. Похоже, всё дело в Speed Grade 1LP:

-

1 hour ago, genseq said:

..., но для начала нужно найти хороших схемотехников, сделать гаджет для считывания сырых сигналов с ячеек секвенатора, получить эти сырые данные, и уже потом напрягать спецов ...

Для начала, вам нужно переформулировать вашу задачу, чтобы она была понятна "хорошим схемотехникам".

Для этого нужно просто указать, электрические параметры этих "сырых сигналов".

То есть нужно указать:

- полосу частот сигналов (Гц);

- максимальную и минимальную амплитуду сигналов (Вольт);

- точность, с которой нужно измерять сигналы (соотношение - сигнал/шум);

- выходное сопротивление источника сигналов (Ом);

- количество источников сигналов (шт).

-

11 hours ago, bvlbond said:

Нужна схема преобразования сигнала - 0 -10 вольт положительной полярности в сигнал 0-24 положительной полярности.

Нужно управлять клапаном в диапазоне 0-24 вольта, ток потребления 0,8А при напряжении 24 вольта.

-

25 minutes ago, Halfback said:

Не поделитесь ссылкой или как в гугле поискать?

Adder Trees, page 17: Advanced Synthesis Cookbook

-

19 minutes ago, yes said:

вопрос с копированием решается тем, что ПЛИС с прошитым ключом скопировать нельзя.

то есть зашифрованная прошивка не будет работать в "чистой" ПЛИС

В 7-ой серии Xilinx'а этот вопрос уже давно решен и всё легко копируется: A Full Break of the Bitstream Encryption of Xilinx 7-Series FPGAs

-

9 minutes ago, Dr.Alex said:

Но почему вы всё-таки решили что это ЛЧМ?

Потому, что уже была похожая тема на форуме:

-

1 hour ago, aaarrr said:

Да, и отброшенные - это rejected, а не dropped.

drop:

comp. удалить; скинуть (drop a file on a USB stick VLZ_58) comp., MS удалить (To remove an association or connection) construct. понижать (о давлении, температуре); понижаться (о давлении, температуре) econ. падать (о ценах) electr.eng. уменьшать energ.ind. отбрасывать (например, члены уравнения) math. отбрасывать (члены); выбросить; исключить; отбросить; откинуть; отставать; отстать; снижаться (off); снизиться (off); спасть; убрать; отказываться от mech. опустить пропускать (в формуле и т.п.); падать о переменной, физической величине; опускать пропускать (в формуле и т.п.)

-

49 minutes ago, fguy said:

Xilinx наконец то осознал, что аппаратный ддр контроллер лучше синтезируемого в плис ...

А аппаратная HBM и того лучше:

Total Bandwidth Block RAM - 539 Tb/s Total Bandwidth Ultra RAM - 205 Tb/s Total Bandwidth HBM2e DRAM - 820 GB/s Total Bandwidth LPDDR4 - 136 GB/s

-

50 minutes ago, RobFPGA said:

Ну так (* multstyle = "dsp" *)

Это для умножения.. А как для сложения? )))

quartus 17.1 файл sdc

в Среды разработки - обсуждаем САПРы

Опубликовано · Пожаловаться

Если почитать логи синтезатора, то видно, что файл *.sdc синтезатор не использует.

Файл *.sdc Quartus загружает только после старта Fitter'а:

IMHO, чтобы не делать заново синтез, нужно просто включить опцию Smart Compilation (или Incremental Compilation):