blackfin

-

Постов

4 126 -

Зарегистрирован

-

Победитель дней

3

Сообщения, опубликованные blackfin

-

-

On 7/11/2023 at 10:26 PM, UART said:

по себе других не судят...

Ой! Ну, еще расскажите нам, какую строчку вы занимаете в рейтинге Forbes? 🙂

On 7/11/2023 at 10:30 PM, Vasil_Riabko said:Для меня достаточно и сайта на английском.

Тогда зачем все эти дурацкие вопросы про китайский язык?

-

On 7/11/2023 at 10:09 PM, Vasil_Riabko said:

Уровень потребления продукции.

И что мешало вам поднять "Уровень потребления продукции" Xilinx до уровня Японии за 17 уже прошедших лет? 🙂 Езыг? 🙂

On 7/11/2023 at 10:11 PM, UART said:Для всех Китай это большой рынок.

Не для всех. Не льстите себе.. 😉

Для вас Китай это не рынок. И вы для Китая - пустое место.. 🙂

-

1

1

-

-

On 7/11/2023 at 9:48 PM, Vasil_Riabko said:

В те времена китайской версии сайта не было.

Учите латынь: «Времена меняются и мы меняемся вместе с ними».. 🙂

-

On 7/11/2023 at 9:37 PM, Vasil_Riabko said:

Надеялся на исключительную эрудицию участников. Ну не знаете извините .

Про Intel не знаю, а у Xilinx'а есть сайт на китайском: https://china.xilinx.com/products/silicon-devices/fpga.html

Можете там спросить.. прямо на китайском.. 🙂

-

On 7/11/2023 at 9:21 PM, Vasil_Riabko said:

Звісно вивчив ще в Університеті.

Тогда и спрашивайте у Intel напрямую. Чего тут на форуме вопросы не по адресу задавать?

-

On 7/11/2023 at 8:49 PM, Vasil_Riabko said:

Интересно в Intel, TI ... есть в штате переводчики или они тоже ждут и надеятся?

Так если "интересно", то и спросите сами у Intel'а и TI.. Язык же, английский, уже выучили? 🙂

On 7/11/2023 at 9:04 PM, Vasil_Riabko said:У них берут в штат переводчиков или им это не надо по причине :

- они знают язык например китайский, русский ...;- им это не надо по причине бесполезности информации на китайскиом, русском ...

И спросите, знают ли инженеры из Intel украинский?

... или им это не надо по причине бесполезности информации на украинском? 🙂

-

-

On 6/23/2023 at 9:41 PM, RobFPGA said:

тоже самое справедливо и для схемы stream, Поэтому я взял одинаковое число в N тактов для ввода данных для обоих случаев

Да, справедливо. Поэтому Pipelined, Streaming I/O считает быстрее, чем Burst I/O, но для одинаковых Radix.

Сейчас же речь о том, что Radix64 Burst I/O считает быстрее, чем Radix2 Pipelined, Streaming I/O.

-

On 6/23/2023 at 9:27 PM, RobFPGA said:

Как то хитро вы в наперстки играете ...

Ваша ошибка в том, что вы пытаетесь загрузить входные данные в БПФ за N тактов.

А это не так.. Данные в БПФ можно загрузить за N/Radix тактов..

То же самое справедливо и для выгрузки данных из БПФ..

Но это не Xilinx, это другое.. 🙂

-

On 6/23/2023 at 6:16 PM, _4afc_ said:

Для FFT8 конечно. Он же потоковый, последовательный.

На вход запихиваем символы во времени, на выходе они по частоте.

Надо больше - цепляй дальше ещё...

Скорость проекта то уже не упадёт, если добавлять такие же "Radix8 на логике" и BRAM/DSP... (если везде не более 18 бит конечно).

Разговор глухого с немым..

Спрошу по-другому.

Сколько времени требуется "потоковому Radix8 на логике в GW2A" для вычисления БПФ от массива комплексных данных длиной 32768 точек ?

Назовите время между загрузкой в модуль БПФ последнего семпла под номером 32767 и временем появления на выходе модуля первого семпла вычисленного спектра.

Для вычисления первого семпла спектра по схеме Radix32 Burst I/O модулю БПФ требуется 6,55 микросекунды при условии, что сам модуль БПФ работает на частоте 500 МГц.

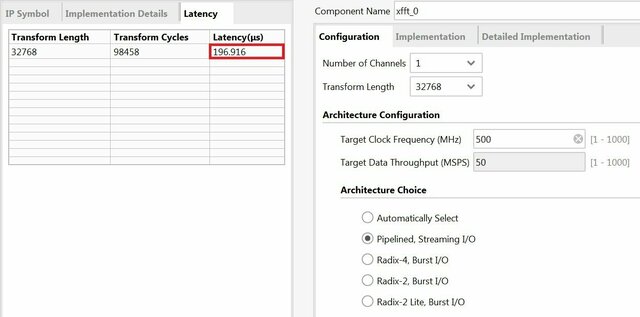

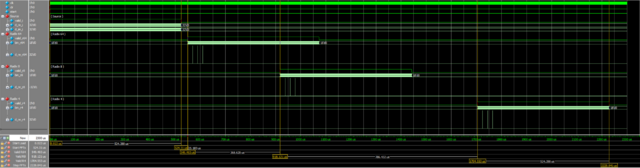

Упоминавшаяся тут "быстрая" схема Pipelined, Streaming I/O Xilinx'а вычисляет спектр при прочих равных условиях за 197 микросекунд:

-

On 6/23/2023 at 3:02 PM, _4afc_ said:

Всего 50MSPS на DSP у таких крутых камней :(

Потоковый Radix8 на логике в GW2A даёт 150MSPS при R(840) LUT(518) ALU(834) DSP(0) BSRAM(0) SSRAM(8)

А для какой длины FFT этот "Radix8 на логике" дает 150 MSPS ?

-

On 6/23/2023 at 11:33 AM, RobFPGA said:

Больше только умножителей и сопутствующей логики, а вот памяти (в зависимости от варианта схемы) может даже и меньше.

"Может, дождик.. Может, снег.. Может, будет.. Может, нет.."

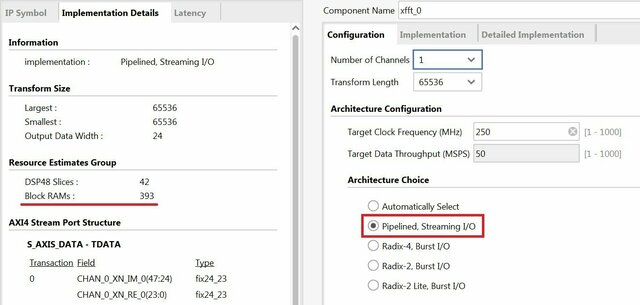

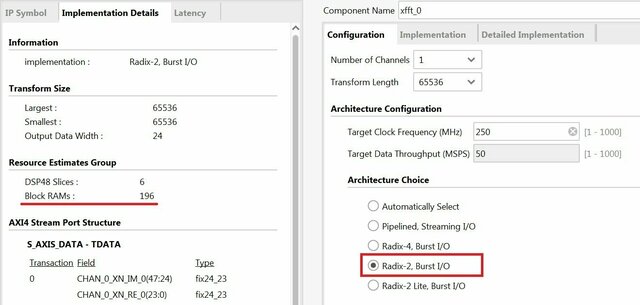

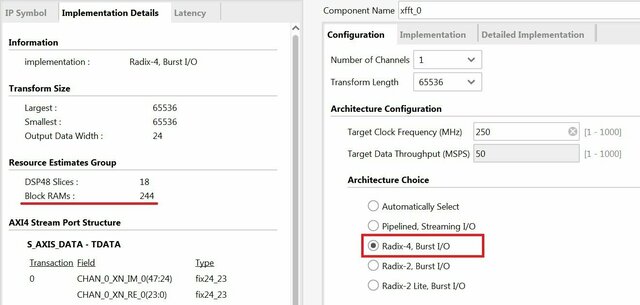

"Разнообразная жизнь" IP Catalog'а наглядно показывает, что для схемы Pipelined, Streaming I/O требуется существенно больше BRAM памяти, нежели для схемы Radix-4, Burst_I/O и уж тем более, для схемы Radix-2, Burst I/O:

-

On 6/23/2023 at 12:26 AM, RobFPGA said:

Минимальное latency счета имеют стримовые схемы при которых расчет FFT идет в процессе ввода/вывода. При этом можно и на памяти сэкономить, так как разрядность требуeмых буферов нарастает.

Да, pipelined_streaming считает быстрее, чем burst_io, спору нет.

Но и ресурсов pipelined_streaming требует в несколько раз больше, чем burst_io.

Фактически, модуль pipelined_streaming представляет собой конвейер из нескольких burst_io соединенных последовательно в одну цепочку.

Поэтому для FFT длиной больше 65536 схема burst_io является единственно возможной для реализации на одном чипе FPGA.

-

On 6/22/2023 at 4:25 PM, _4afc_ said:

Интересно, а как решается вопрос с нормировкой и переполнением при FFT262144 на Radix64?

Старшие 18 разрядов при белом шуме - такие же как "знак" или обрезаются? Сколько разрядов на входе\выходе FFT?

Есть два режима:

- с ограничением при переполнении разрядной сетки;

- со сдвигом на log2(Radix) разрядов после каждой "бабочки".

Собс-но, это почти так же как у Xilinx'а.

При этом кол-во разрядов на выходе равно кол-ву разрядов на входе.

On 6/22/2023 at 4:34 PM, RobFPGA said:Все же остается вопрос зачем Radix64?

Да еще для такой схемы FFT, и для такого чипа FPGA?Так Latency..

При прочих равных условиях и при больших N:

- Radix8 считает в 3 раза быстрее, чем Radix4;

- Radix16 считает в 8 раз быстрее, чем Radix4;

- Radix32 считает в 20 раз быстрее, чем Radix4;

- Radix64 считает в 48 раз быстрее, чем Radix4;

Есть много приложений, в которых важно время вычисления FFT:

- радиолокация быстрых целей;- передача видео в формате DVB-T2 на соревнованиях по гонкам на квадракоптерах;

- связь 5G с использованием OFDM;

- спектроанализаторы на АЦП с частотой дискретизации 20 ГГц (напр., AD9084);

- да мало ли, где ещё.. 🙂

Опять же, если ставить впараллель несколько FFT, то с точки зрения BRAM, экономнее параллелить FFT с Radix32 или Radix64.

Что касается чипа, то Radix64 на 4096 точек легко умещается в KU5P (12% по BRAM, 64% по DSP)..

Так же легко Radix32 на 32768 точек умещается в тот же KU5P (37% по BRAM, 26% по DSP)..

-

On 6/22/2023 at 10:58 AM, tankist said:

Может еще какой-нибудь совет дадите на базе того, что имеется на сегоднящний день?

digital-predistortion-for-rf-communication.pdf

PS. И в конце статьи ссылка на IEEE.

-

On 6/16/2023 at 5:12 PM, _4afc_ said:

В вашем Radix64 DataRAM какой длины и на чём?

На URAM. Длина всегда N/Radix.

-

On 6/16/2023 at 4:57 PM, _4afc_ said:

Я не понял что значит Radix-64 на 2**18 комплексных семплов. Задача FFT64 или FFT262144?

Тогда на что расходуются BRAM в VU13P?

Длина БПФ равна 262144. Основание БПФ (кол-во ветвей в "бабочке") равно 64.

То есть, в каждом такте БПФ вычисляются 64 новых комплексных семпла.

BRAM'ы в основном для констант.

PS. Кстати, в новых Versal'ях под константы можно использовать URAM. А их по объему больше, чем BRAM. 🙂

-

On 6/16/2023 at 4:41 PM, _4afc_ said:

У вас FFT262144 на R64-R64-R64 для которых приходится иметь 3-4 комплексных линий задержки длиной 131072?

Не совсем понял вопрос. У меня архитектура FFT аналогична архитектуре "burst_io" у Xilinx'а. То есть, все вычисления "in_place". Нет никаких "комплексных линий задержки".

-

On 6/16/2023 at 3:46 PM, _4afc_ said:

Ваш вариант Radix64 под ПЛИС? Умножители используете или только сложения и сдвиги?

Да, для ПЛИС. Используются умножители из DSP48, но Radix-64 на 2**18 комплексных семплов с 32-х битной точностью не влазит в VU13P по BRAM. 🙂

Так что это пока всего лишь "игры разума".. 🙂

-

On 6/16/2023 at 1:40 PM, _4afc_ said:

Где посмотреть на исходники/формулы для Radix больше 16?

а то я кроме трудов nussbaumer ничего пока не видел, а там только до Radix-16.

Я делал по книге: Рабинер Л., Гоулд Б., "Теория и применение цифровой обработки сигналов", Мир, 1978.

Но и там максимальный Radix равен 8. Всё что выше - просто по аналогии.

-

-

On 6/6/2023 at 3:38 PM, Zversky said:

... застопорить процесс в сторону Xilinx, либо продолжать смотреть в их сторону?

-

On 5/19/2023 at 11:39 AM, Plain said:

Вы о чём? Автор непосредственно расход измеряет, объём за время.

Прежде, чем измерять "объём за время", нужно бы учесть растворимость углекислого газа в воде.

Потому как растворимость эта довольно велика (Вики: 1,48 г на 100 мл) и сильно зависит от температуры и от состава воды, которой поливают растения.

Если поливать водой, в которой уже растворен углекислый газ, то расход будет один, а если поливать водой, в которой углекислого газа ещё нет, то расход будет другой.. 🙂

-

On 5/16/2023 at 9:16 AM, repstosw said:

Да и разнос можно сделать в несколько МГц. Но даже и там, я не помню, чтобы была работа рядом с занятым каналом. Обычно уходят намного дальше, чем +/-1 канал.

Никто никуда не уходит.. :)

Обычное эфирное ТВ выделяет для каждого ТВ канала полосу 8 МГц - Частоты и номера каналов эфирного и кабельного телевидения:

QuoteИз этой таблицы видно, что ширина полосы частот каждого канала (или мультиплекса) составляет 8 МГц, и эти полосы идут подряд. Защитные полосы (guard band = 250 kHz) включены в основную ширину полосы частот канала.

В формате DVB-T2 частотный спектр каждого канала выглядит так:

Возврат к брендам после отмены санкций

в Все остальные микроконтроллеры

Опубликовано · Пожаловаться

Откуда такие сведения? Я много раз общался на английском (не в переписке, а в живой беседе) с японскими инженерами из фирмы Panasonic и не заметил какой-либо слабости..

Может, вы сами не вполне сильны в английском? 🙂