-

Постов

4 838 -

Зарегистрирован

-

Победитель дней

2

Весь контент Xenia

-

Вопросик по I2C

Xenia ответил okela тема в Форумы по интерфейсам

Согласна с вами ... наполовину 🙂, действительно проверка в режиме gpio в режиме pulldown должна определить наличие внешней подтяжки. Причем проверка в режиме pullup для этой цели не требуется. Одно только плохо - для такого рода теста пришлось бы постоянно отключать I2C и переходить в режим обычного GPIO_MODE_INPUT, а после проведения теста вновь инициировать режим I2C. Это было бы не страшно, если делать этот тест только перед началом работы, но сильно обременительно, если обрыв линии возможен в процессе работы (сильно замедлило бы как чтение, так и запись по шине). Тем более что при переходе из режима I2C в GPIO и обратно требуется выдерживать какие-то таймауты. Тем не менее существует функция: HAL_StatusTypeDef HAL_I2C_IsDeviceReady(I2C_HandleTypeDef *hi2c, uint16_t DevAddress, uint32_t Trials, uint32_t Timeout) которая не виснет при отсутствии подтяжек и при разрыве I2C-шины, возвращая значение HAL_BUSY. И этот ответ, по-видимому, правильный, т.к. низкий уровень шины действительно следует рассматривать так признак ее занятости. Между тем, эта функция не выходит из режима I2C, а стало быть принципиально возможно определить низкий уровень I2C-шины, не прибегая к переходу в режим GPIO_MODE_INPUT. Спрашивается, как этой функция это удается? Я уже лазила в сорцы. Там для HAL_I2C_IsDeviceReady довольно запутанный код, однако выяснила, что информацию она берет через функцию __HAL_I2C_GET_FLAG(...), которая определена как дефайн: #define __HAL_I2C_GET_FLAG(__HANDLE__, __FLAG__) ((((uint8_t)((__FLAG__) >> 16U)) == 0x01U) ? \ (((((__HANDLE__)->Instance->SR1) & ((__FLAG__) & I2C_FLAG_MASK)) == ((__FLAG__) & I2C_FLAG_MASK)) ? SET : RESET) : \ (((((__HANDLE__)->Instance->SR2) & ((__FLAG__) & I2C_FLAG_MASK)) == ((__FLAG__) & I2C_FLAG_MASK)) ? SET : RESET)) Глубоко не разбираясь в коде, здесь уже видно, что информация вытягивается из флагов регистров SR1 и SR1. Отсюда и следующий вопрос - какие флаги для моей цели годятся? Описание всех флагов, содержащихся в этих регистрах, я уже смотрела, но почти ничего не поняла. Наиболее перспективными (по названию) мне показались флаги (комментарий к ним чужой): SR1->TIMEOUT (Timeout or Tlow error) — возникает если линия SCL прижата к земле. Для master 10mS, для slave 25mS. SR2->BUSY(Bus busy) — флаг занятости. В моих интересах провести тест, не покидая режима I2C, тем более что проверка флага - очень быстрая процедура, которую я могла бы с случае успеха такого теста проводить перед каждой транзакцией, не теряя в скорости передачи. Можно ли что-то подсказать мне по этому поводу? Этот флаг тоже смотрела, но ясности у меня не прибавилось. Вот что про него написано: SR1->ARLO (Arbitration lost (master mode) ) — устанавливается при потере арбитража. Для сброса нужно записать 0. На его фоне флаги SR1->TIMEOUT и SR2->BUSY выглядят в моих глазах более перспективными. -

Вопросик по I2C

Xenia ответил okela тема в Форумы по интерфейсам

У меня возник еще один животрепещущий вопрос. Контроллер (у меня это STM32F103C8T6) намертво виснет (оживает только по WatchDog'у) при выполнении функций: HAL_StatusTypeDef HAL_I2C_Mem_Write(I2C_HandleTypeDef *hi2c, uint16_t DevAddress, uint16_t MemAddress, uint16_t MemAddSize, uint8_t *pData, uint16_t Size, uint32_t Timeout); HAL_StatusTypeDef HAL_I2C_Mem_Read(I2C_HandleTypeDef *hi2c, uint16_t DevAddress, uint16_t MemAddress, uint16_t MemAddSize, uint8_t *pData, uint16_t Size, uint32_t Timeout); когда линии SDA и SCL не подтянуты к питанию, вне зависимости от того, какой задаешь Timeout. Т.е. зависает на этой процедуре и по Timeout'у из нее не выходит. Я отлично понимаю, что случай, когда линии I2C не потянуты к питанию резисторами - аномальная ситуация, в которой нельзя требовать от шины нормальной работы. Однако мне сильно хочется, чтобы обрыв в шины (а резисторы подтяжки находятся на слейве, т.к. этот контролер не умеет такую подтяжку создавать сам, а на плате она не предусмотрена) не приводил к зависанию, чтобы контроллер мог бы выдать по этому поводу вразумительное сообщение об ошибке. Типа: "Шина I2C оборвана". Уже пробовала определять уровень на пинах SDA и SCL, но получаю результат такой, что оба пина имеют высокий потенциал, как и должно быть. Вопрос: есть ли какой-то способ проверить наличие подтяжки на линиях SDA и SCL, а еще лучше сделать так, чтобы контролер при операциях чтения и записи по шине I2C не зависал, если на ней нет подтяжки? -

Сообщаю для своих: 🙂 На FTP в директории /pub/DSP/TI - Code Composer Studio/ есть вcе версии CCS (сама долгое время их собирала).

-

https://wiki.iarduino.ru/page/power-key-4p-a-i2c/ https://wiki.iarduino.ru/page/power-key-4n-a-i2c/

-

STM32F405 или STM32F407 легко эту частоту вытянет, если, конечно, меандр нужен правильный со скважностью 50%. У этих чипов тактовая частота до168 МГц, а если ее понизить до 128 МГц, то будет в самый раз для меандра на 64 МГц. Я сама недавно на Aliexpress вот такую плату заказала и уже почтой ее получила: https://aliexpress.ru/item/1005004064401634.html 1000 руб без доставки, конечно, дороговато, то не слишком, если нужно для дела.

-

Как же я его выломаю, если там монтаж печатный? Могу просто ничего к нему не присоединять, если для прошивки он не нужен. А стабилизатор на этой плате есть, а точнее - LDO, которое из 5V делает 3.3V для питания контроллера, т.к. сам модуль питается от внешнего источника 5V. Возможно, что этот разъем был сделан в расчете не на J-Link, а на ST-Link.

-

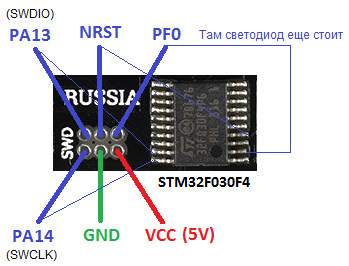

Российский SWD? Дело было так. Купила я себе (для проекта) отечественное изделие (на нем так и написано "RUSSIA") - силовой ключ под управлением контроллера STM32F030F4 и решила его перепрограммировать под свою специфическую задачу. Однако столкнулась с трудностью прошивки из-за того, что у этого модуля SWD-разъем (а точнее - только дырочки вместо него) размером 3x2 пина (итого пинов 6), а расстояния между ними малы - 1.27 мм. В начале рассчитывала спаять переходник с этого SWD на стандартный разъем J-TAG (10x2 пинов) по схеме, найденной мной в интернете: Но поскольку нумерации пинов на том разъеме не было, то решила прозвоном определить, где у этого разъема земля. Оказалось, что не с краю, а в середине! После этого стала прозванивать всё остальное и вот что выяснила: Распиновка этого SWD оказалась совершенно не той, что на схеме из интернета. Мой вопрос: кто-нибудь встречался с такой распиновкой? И как мне его теперь к J-Link'у подключать? (BOOT0 у этого контроллера в землю впаян, а SWO нет совсем)

-

Насколько они будут коротки? Успеет ли счетный вход таймера их посчитать? И какую конструкцию задержки вы рекомендуете? RC-цепочки будет достаточно?

-

Если оно так, то попробую изменить схему и вопрос. Раз уж нельзя присоединять ресет триггера R к клоку CLK, то что будет, если присоединить его к ~Q (буквы Q с верхней палочкой не нашла, а потому вынуждена изображать инвертированный выход триггера как "~Q"). Задумка моя такая: у исходного/сброшенного триггера Q=0 и ~Q=1. Высокий уровень с ~Q поступит на ресет R, но ничего не произойдет, т.к. триггер сбрасывается низким уровнем на R. Теперь подаем на клок CLK меандр, от восходящего фронта которого триггер должен сработать и перекопировать высокий уровень D на Q. От этого и ~Q должен изменить свой потенциал - стать низким. Этим низким потенциалом на R триггер будет сброшен (т.к. по схеме R=~Q). От этого Q снова станет низким, ~Q - высоким и триггер с ресета снимется. Вопрос: получу ли я таким способом иглообразные импульсы на выходе Q после каждой положительной фазы меандра?

-

На тех же D-триггерах идея реализована, а усложнение из-за того, что совпадения и несовпадения считают отдельно. А если считать только совпадения (как оно мне надо), то эта схема упростится до моего решения, тем более простого, если сброс триггера (R) можно тактировать от того же сигнала, который поступает на вход клока. Результаты симуляции на Протеусе на этот счет вдохновляют:

-

Может быть приоритет на это прерывание мал, из-за чего системный таймер его иногда перебивает. Отсюда то одна задержка, то другая.

-

Фазовые детекторы обычно используют на аналоговых сигналах (или чтобы хотя бы один из них был аналоговый), где фактически происходит их перемножение. Тогда как у меня оба сигнала цифровые, а в этом случае было бы вредной практикой работать и ними, как с аналоговыми напряжениями, а уж тем более использовать ГУН (VCO), как в микросхеме CD4046B из вашего примера. Лично я убеждена, что задачи с цифровыми/бинарными (двухуровневыми) сигналами имеют решение на том же цифровом уровне, не прибегая к их превращению в напряжения.

- 61 ответ

-

- 1

-

-

От элемента XOR ровно столько же толку, как от элемента AND - оба для моих целей не годятся. Вот если бы на выходе таких элементов у меня стоял не счетчик, а интегратор, суммирующий время, в течение которого сигнал на его входе бывает высоким/положительным, то величину корреляции этим способом я могла бы измерить. Но когда у меня на выходе счетчик импульсов, то он одинаково прибавит единичку, как в том случае, когда после схемы AND верхние полочки обоих меандров частично перекрываются, так и в случае, когда после схемы XOR они частично не перекрываются. Т.е. счетчик суммирует не ширину импульсов, а только их количество. Тогда как элементы AND или XOR выдадут импульсы почти в любом случае, поскольку ЧАСТИЧНОЕ перекрывание имеет место почти всегда, а при частичном перекрывании всегда есть как совпадающая, так и несовпадающая области. На этот счет у меня была даже идея-фикс - подать первый меандр на клок SCLK шины SPI, а второй меандр на MISO той же шины, чтобы потом посчитать число нулей и единичек в полученных байтах. Но к сожалению, интерфейс SPI между приемами разных байтов на какое время "слепнет", из-за чего будет пропускать такты. Т.е. на триггере оно было бы и надежнее, и быстрее.

-

Смысл моих действий в том, что я хочу оценить степень корреляции двух генераторов меандров. А именно настроена на то, что меандр от 1-го генератора я буду подавать на входы CLK+R триггера, а на его вход D подавать меандр от 2-го генератора. Задумка такая: в случае, когда в момент восходящего фронта 1-го генератора меандр 2-го генератора находится в высокой/положительной фазе, то на выходе триггера я получу импульс близкий к тому, какой подавала на CLK+R. А если в этот момент меандр 2-го генератора находится в нулевой/низкой фазе, то никакого импульса я не получу. Отсюда следует, что считая одним счетчиком импульсы от 1-го генератора, а вторым счетчиком импульсы с выхода триггера, можно получить как общее число импульсов (по 1-му счетчику), так и число совпадений (по 2-му счетчику). В случае отсутствия корреляции между генераторами второе число ожидается равным половине от первого, тогда как значительное отклонение его от 50% свидетельствовало бы о наличии корреляции.

-

Ответьте мне кто-нибудь: что случится, если D-вход D-триггера (такого как ТМ2) присоединить к плюсу питания, а CLK и R соединить вместе? Будет ли в этом случае на выходе такого триггера получен меандр, если таковой я буду подавать на CLK и R сразу? Могу иначе сформулировать тот же вопрос: успеет ли триггер защелкнуть уровень D (он в этой схеме всегда высокий), если этот триггер сняли с ресета одновременно с началом восходящего фронта на клоке?

-

вопрос по AD7741

Xenia ответил yung тема в Вопросы аналоговой техники

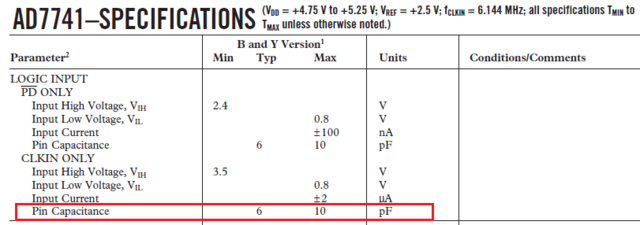

В даташите на AD7741 пишут, что у нее ёмкость входа CLKIN составляет 6-10 пФ. Т.е. можно считать, что какая-то ёмкость там уже есть, что по идее не должно позволить победить 5-ой гармонике. Тем более что выводы у моего кварцевого резонатора довольно длинные (какую-то индуктивность они должны бы давать). К тому же это не часовой кварц, а кварц на довольно высокую частоту 6 МГц, у которого высшие гармоники совсем высоки. Может быть для их подавления и 10 пФ будет достаточно? Тем более когда инвертор у нее не столь быстр по времени переключения. P.S. Возможно не по делу, но у меня возникла сильная ассоциация с когда-то собранной мною схемой генератора частоты, состоящего из 3-х логических инверторов состыкованных в кольцо. А если быть более точной, то использовалась микросхема с 4-мя элементами 2И-НЕ (на подобие отечественной ЛА3), где 3 элемента работали в кольце в качестве инверторов, а 4-ый элемент выводил частоту из кольца на выход. Так вот мне так и не удалось получить этим способом частоту 45 МГц, как я ни старалась подобрать микросхемы. CD4011BE не дотянула даже до 1 МГц, SN74HC00N не дотянула до 10 МГц. Наибольшую частоту 25 МГц выдала SN74AS00N. Но более быстродействующей мне достать не удалось. Эта ассоциация возникла у меня из-за сомнения возможности получать высокие частоты на логических элементах, имеющих ограничение на скорость срабатывания. -

вопрос по AD7741

Xenia ответил yung тема в Вопросы аналоговой техники

А если и его не будет, то что случится? Генератор без него заведётся или нет? -

вопрос по AD7741

Xenia ответил yung тема в Вопросы аналоговой техники

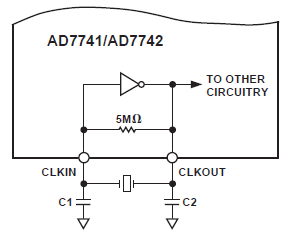

А помимо всех этих расчетов, существует ли какой-нибудь объективный признак того, что емкости конденсаторов недостаточно? Типа, что будет мне за то, если я этих конденсаторов вообще не поставлю? Тем более что у меня их и нету 🙂. Ведь если без этих конденсаторов генератор вообще не заведется, то это одно дело, а если лишняя гармоника появится, то другое. В первом случае действительно пришлось бы заморачиваться, а второй случай могла бы и пережить. В конце концов, эта частота нужна не для какого-то процессора, считающего важные вещи, а для AD7741, которая не "мыслит", а попросту просеивает эту частоту через своё "сито", выдавая остаток наружу (Fout). Ну, и в чем трагедия, если туда чуточки другой гармоники попадет? Тем более когда входная частота 6 МГц, а разрядность по преобразованию не превышает 12 бит (согласно даташита). Скажем, если на CKLOUT я поставлю счетчик импульсов, то смогу ли оценить чИстоту гармоники сравнением числа импульсов на счетчике за 1 сек (тогда число импульсов равно их частоте) с номиналом моего кварца? Или, если потом добавить ёмкость с избытком и посмотреть, как это скажется на счетчике? А если окажется, что ёмкость на частоту не влияет, но и не не мучится с ее расчетом. А копаю я в эту сторону не от природной назойливости :), а только потому, что у меня никаких дорожек нет! Поскольку у меня не печатная плота, а макет. Т.е. я просто приноравливаюсь к тому, чтобы припаять кварцевый резонатор сбоку. А поскольку между выводами кварца 5 мм, а у микросхемы AD7741 между ножками CLKIN и CLKOUT (эти ножки соседние) всего 1.27 мм, то я вознамерилась просто свести выводы кварца ближе друг к другу и прямо к ножкам AD7741 припаять. А то, что он при этом в воздухе висеть будет, меня мало волнует. Как и возможные наводки ВЧ от выводов кварца, укоротить которые не получается. Да и нет рядом с AD7741 ничего такого, чему бы эта ВЧ могла помешать. Ну, и вешать туда еще два конденсатора мне тоже страшно не хочется. Отсюда и мой следующий вопрос: "заведется" ли генерация без конденсаторов? -

вопрос по AD7741

Xenia ответил yung тема в Вопросы аналоговой техники

А если так, то почему всюду стараются сделать эти дорожки короче? Хотя, казалось бы, их, наоборот, следовало бы делать длинными, чтобы на конденсаторах сэкономить :). -

вопрос по AD7741

Xenia ответил yung тема в Вопросы аналоговой техники

-

вопрос по AD7741

Xenia ответил yung тема в Вопросы аналоговой техники

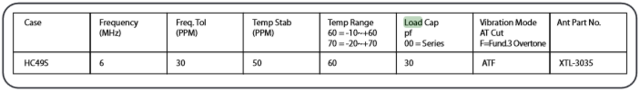

Тема уже стара, но для моего вопроса как раз подходит. А вопрос такой: какого номинала надо ставить конденсаторы возле кварцевого резонатора (в даташите они обозначены, как C1 и C2), если у кварца предельно высокая (но разрешенная даташитом) частота 6 МГц? Причем в самом даташите (он здесь: https://www.analog.com/media/en/technical-documentation/data-sheets/AD7741.pdf) номиналов для этих кондесаторов я не нашла. Или плохо искала? "The values of capacitors will vary depending on the manufacturer’s specifications." -

Вы правы, я переправила в своем посте -5V на -2.5V. Однако эти 2.5V и есть половина шкалы при разнице AVDD-AVSS=5V, что в принципе решает проблему измерения биполярного сигнала без его дополнительного кондиционирования до входа.

-

Хотела бы выяснить мнение аудитории относительно ADS1262/ADS1263 https://www.ti.com/lit/ds/symlink/ads1262.pdf причем не столько по поводу его высокой разрядноcти, сколько по тому, что, согласно даташита, он допускается разницу между аналоговой и цифровой землей в пределе аж до 7-ми вольт! Voltage DVDD to DGND 7V (MAX) Означает ли это, что на аналоговую землю я могу подать -2.5V (минус пять), оставив цифровую землю на той же земле, что и контроллер, и тем самым измерять напряжения в интервале от -2.5V до +2.5V, не пользуясь средствами входного сдвига потенциала?

-

Советую удалить файлы: *.dsw *.mbt *.mrt из вашего проекта. Самому проекту это не повредит. Особливо *.dsw бывает вредоносен, т.к запоминает расположение окон IDE.

-

Оригинал работает на частоте, не превышающей 2.4576 MHz. А если стоит кварц на 4.9152 MHz, то велено устанавливать делитель на 2, чтобы внутри было по-прежнему 2.4576 MHz (это из вашей цитаты следует). Тогда как китайский TN7705 вроде бы способен работать на тактовой частоте 4.9152 MHz без делителя.