-

Постов

317 -

Зарегистрирован

-

Посещение

Весь контент McSava

-

А почему никто не вспоминает, что зазоры выбирают не только их технологических возможностей производства, но еще они зависят от максимального напряжения между двумя проводниками. А ширина дорожек выбирается исходя из максимального тока в цепи. Для МК это несущественно (невысокие напряжения и сравнительно небольшие токи), но все же помнить об это нужно. Из опыта, делать очень малый зазор между всеми проводниками не стоит. Одно дело когда непротрав в одной точке на плате, а другое когда их много и по все длине дорожки. Для ЛУТ 0,2/0,2 мм зазор/дорожка можно делать если будет новый раствор для травления. Хотя по возможности я делаю такое только возле микросхем. 0,3/0,3 делается уже гораздо легче. И без надобности зазор делать меньше 0,3 я бы не стал, раздвигая где возможно проводники.

-

Мы для тактирования своих схем АЦП наиболее часто применяем микросхемы ON Semi. У них есть апноут по применению ECL/PECL разветвителей AND8020 У TexasInstruments в отладочной плате на АЦП используется MC10EP16DT. На 4 странице схемы (33 страница PDF документа) показана схема включения с подключением подтяжек к ножке Vbb и конденсатором на землю. Проверено, такая схема работает. Есть подобные микросхемы и у TI (в разделе Clocks and Timers) и у AD. По поисковому фильтру можно найти тип входа и выхода, а так же количество входов/выходов. Ну и как вариант поставить VCO c 10 МГц опорой. Там и возможностей намудрить будет поболее.

-

Пин Vref DDR2

McSava ответил Art55555 тема в Цифровые схемы, высокоскоростные ЦС

Для DDR(2,3) требуется напряжение питания подтяжки VTT равное половине напряжения питания для подтяжки адресных и управляющих битов. Мы используем регулятор TPS51200 от TI и на ней есть выход Vref. Он у нас подключен. Посмотрите рекомендации производителя по подключению адресной шины и управляющих сигналов. -

Ищу работу

McSava опубликовал тема в Ищу работу

Александр Викторович Савченко 30 лет (16 июля 1981) Днепропетровск Телефон мобильный +380 67 135-98-39 Электронная почта: [email protected] ICQ: 328507429 Skype: savamcsava Инженер-электроник Разработка цифровых устройств разной степени сложности. Полная занятость, Полный день Опыт работы Сентябрь 2006 — по настоящее время ООО "Пульсар" (Днепропетровск, pulsar.co.ua/) — Приборостроение/радиоэлектроника Инженер-электроник Разработка высокоскоростных плат обработки данных АЦП и ЦАП с частотой преобразования от 50 МГц и выше, разрядностью 12-16 бит. Платы до 12 слоев выполненные по 5 классу точности. Проектирование печатных плат в системе Mentor Graphics, работа с продуктами DesignView, Expedition PCB, IODesigner, HyperLynx, HyperLynx Thermal. Согласование проектов для DFM, DFA. Подготовка документации к производству и монтажу, в том числе плат с объединением в панель, ведение внутреннего склада компонентов. Базовые знания работы с FPGA фирмы Xilinx семейств Spartan-3, Spartan-3E, Spartan-6, Virtex-2 pro, Virtex-5, Virtex-6, Kintex-7 в оболочке Xilinx ISE. Работа в System Generator для Xilinx в Matlab + Simulink. Проектирование библиотечных компонентов, схем и печатных плат к ним. Настройка и запуск плат, тестирование и снятие характеристик с плат АЦП, подготовка плат к отправке заказчику. Автоматизация снятия характеристик плат АЦП. Проектирование печатных плат формфактора PCI-express, Eurocard (3U, 6U), VPX. Работа с предприятиями-изготовителями печатных плат Украины, России, Китая и Тайваня. Базовые знания работы в системе AutoCAD. Базовые знания работы в системе AltiumDesigner. Февраль 2003 — сентябрь 2006 ОАО "УкрНИИТМ" (Днепропетровск, www.ukrniitm.dp.ua/index.php?option=com_content&view=article&id=60&lang=ru) — Приборостроение/радиоэлектроника начальник сектора Разработка аппаратуры для неразрушающего контроля (УЗ дефектоскопия, толщинометрия, аналоговые и цифровые узлы), выбор схемных элементов, проектирование печатных плат в системе P-CAD 200x, написание методик поверки и работы для дефектоскопии, толщинометрии. Выбор методов контроля, работа со смежными организациями и поставщиками компонентов. Изготовление пьезоэлектрических преобразователей по существующей документации. Снятие характеристик и паспортизация ПЭП. Работа с дефектоскопами УД2-55 "Ультразонд", УД2-12, УД2-17. Работа с измерительной аппаратурой (осциллограф, генератор, вольтметр и пр). Допуск к работе с напряжением до 1000В. Работа с микроконтроллерами Microchip (C-компилятор). Декабрь 2004 — июль 2005 Украинский государственный химико-технологический университет, научно-исследовательская лаборатория химических источников тока (Днепропетровск, udhtu.com.ua/index.php?p=246) — Химическое производство/удобрения Лаборант Исследование химических источников тока ультразвуковыми приборами неразрушающего контроля. Проведение испытаний, документирование измерений. Разработка системы автоматизированного контроля дискретных элементов питания. Апрель 2002 — март 2003 ЧП "Рукис" (Днепропетровск) — Автомобили/запчасти/шины Помощник водителя, продавец. Проведение и контроль погрузочно разгрузочных работ. Слежение за документооборотом. Продвижение товаров в условиях розничного рынка, консультационные услуги. Знание номенклатуры представленных товаров, подбор товара с необходимыми характеристиками. Ключевые навыки Черчение схем, проектирование печатных плат. Чтение и понимание технической документации (в том числе на английском языке), выбор компонентов и схемных решений для решения поставленой задачи. Работа с FPGA фирмы Xilinx семейств Spartan-3, Spartan-3E, Spartan-6, Virtex-2 pro, Virtex-5, Virtex-6, Kintex-7 в оболочке Xilinx ISE. Автоматизация обработки данных в системе MATLAB и Octava. Создание проектов для работы в среде LabView. Знаком с САПР Mentor Graphics, Altium Designer, P-CAD, Dip-Trace, Protel. Базовые навыки работы с языками программирования C, C#. Работа с офисными пакетами Microsoft, OpenOffice. Настройка малых локальных сетей. Образование 2003 Днепропетровский национальный университет Радиофизический факультет, специальность "Радиофзика и электроника", Диплом специалиста 2002 Днепропетровский национальный университет Военная кафедра, ВУС 521100, Инженер по настройке и экплуатации радиорелейных и тропосферных станций., младший лейтенант Знание языков Русский — родной Английский — читаю профессиональную литературу Украинский — могу проходить интервью Повышение квалификации, курсы 2006 Базовый курс введение в VHDL ООО "Пульсар" Подробнее о работах, которые выполнял/принимал участие можно посмотреть на страничке в google sites -

У Xilinx`а есть инструмент ChipScope, его можно подвесить как логический анализатор на шину. Ну и мы обошлись без отдельного прибора. Помимо блоков питания и мультимеров у нас в постоянном обиходе генератор, осциллограф. Частотомер нужен реже.

-

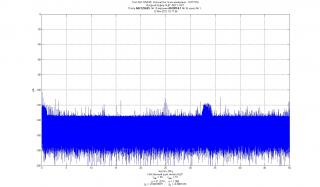

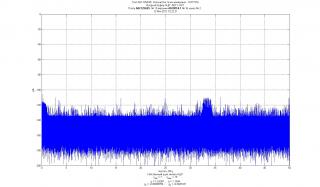

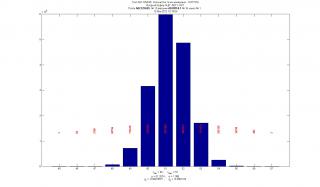

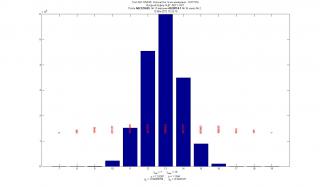

Мы на фирме делали плату на Xilinx Spartan-3 + мост PCIe-PCI от Texas Instruments xio2000a. Драйвер брали старый PCI (до этого плата была PCI). PCI плата была восьмислойной. Такой осталась и PCIe. Для PCIe варианта аналоговую часть вынесли на отдельную плату (6 слоев) с тщательной трассировкой земляных полигонов и питания. На цифровой плате есть 4 буфера памяти по 16Мх16. Для 14 битной 100 МГц платы получили уровень собственных шумов АЦП на уровне 1,13 ЕМР (в документации на микросхему 1,10 ЕМР) и SFDR до 84 дБ. Для 12 битных (до 65 МГц) 8 канальных плат уровень шума на уровне 0,5 ЕМР. Для шестнадцатиканальных плат имело место межканальное влияние на плате (около 45-50 дБ на соседний канал). Плату перепроектировали, но не монтировали. Для плат с работой по PCI проникание на спектре собственного шума сигнала 33 МГц. Нужно как-то лучше фильтровать. Сейчас спроектировали плату на Saprtan-6 без использования моста PCIe-PCI. Разработчик отлаживал PCIe интерфейс на отладочной плате SP605, на ней же поднимал и DDR3 память и режим DMA. Но разработка платы осуществлялась коллективом из трех человек. Я - схема и трассировка, по заданию ведущего инженера, второй человек - программист интерфейсов FPGA и драйверов с Win. И ведущий инженер - раздача задания, пенделей и соединение всего вместе, тонкая настройка проекта внутри ПЛИС.

-

+1 к FabLink, потому что он позволяет быстро переделывать мультипликат при изменении оригинала платы. Причем сам отслеживает изменения в проекте платы. Так же есть возможность создавать общую заготовку для разных проектов.

-

Если не происходит выравнивание длин, то иногда можно поиграться с настройками минимального и максимально возможного изгиба в Editor Control > Dialog > Tuning Patterns. За что отвечают конкретные настройки было описано в тренингах. Еще можно выделить все пары для выравнивания и нажать кнопку F7 Tune. Но опять же такие выравнивание произойдет, только если есть место куда делать "змейку". Иногда подстройка длины может занять всю доступную площадь на слое и одна или несколько цепей останутся не выровняными. Помогает уменьшение значения Maximum Height. Или выравнивание вручную при помощи Manual Tune.

-

Как включить АЦП в common-mode режиме

McSava ответил dysan тема в В помощь начинающему

В даташите есть упрощенная схема включения в Single Ended Mode при помощи трансформатора. Можно для подачи сигнала на АЦП реализовать схему из отладочной платы на это или другое 16-битное АЦП. При трансформаторном включении сигнал подается на первичную обмотку, а АЦП присоединяется к вторичной обмотке со средним выводом. На средний вывод подается напряжение смещения Vcm которое выставляет АЦП. Иногда первичная обмотка развязана конденсаторами от земли и входного сигнала. -

Довести до серии платы Intel Xeon 5500

McSava ответил tAmega тема в Предлагаю работу

Разработками на C2D занимался "СканИнжинирингТелеком" Как они тестирую свои платы - можно поинтересоваться у них. По поводу долгосрочного тестирования, может есть смысл запустить долгосрочное моделирование? У нас когда-то была похожая проблема, в итоге запустили долгое моделирование и на N-транзакции выползла ошибка. Времени этот тест занял пару дней, запускали с остановками и продолжением с остановленого места. Проектировщики цифры потом разобрались откуда ноги растут и исправили. Но изначально тоже рыли в трассировке ПП, тыкались в питание - потому что это было быстрее чем писать/собирать большой тестбенч и первое что мы обычно проверяем. -

DAC/ADC и сигнальный процессор

McSava ответил Domer тема в В помощь начинающему

цап с частотой выхода не менее 200 МГц - High Speed DAC. Sample / Update Rate (MSPS) разрядность кода не менее 8 - Resolution (Bits) > 8. соответственный ацп High Speed ADC По сигнальным процессорам не подскажу, мы используем ПЛИС Xilinx. Для таких скоростей выводы часто делают LVDS. Нужно смотреть на параметры ПЛИС/ЦСП по максимально возможной входной частоте сигнала. Как то так. Причем для данных Величина может подойти, а для клока нет. Например в младших семействах ПЛИС входной тактовый сигнал, приходящий в клоковый домен, мог быть максимум 180 МГц, а данные могут быть 400 МГц. Эти нюансы нужно учитывать. И не только эти. -

Модули сбора данных 10 каналов ЦАП АЦП

McSava ответил Daedal07 тема в В помощь начинающему

Добрый день. Мы разрабатывали многоканальные варианты АЦП. Связки АЦП-ЦАП были двухканальные 100 МГц (2 ЦАП + 2 АЦП). На плате установлена DDR SDRAM память 4 микросхемы 16М отсчетов по 16 бит. PCIe x1. Поддержка DMA режима. Сейчас есть вариант плат 12 битных АЦП 8 и 16 каналов в формфакторе PCIe x1, но частота оцифровки 50 МГц (для 8 каналов) и 25 МГц (для 16). Полоса пропускания микросхем АЦП до 520 МГц, для 8 канальных микросхем и 750 МГц для одноканальных. Аналоговая часть выполнена на мезонинной плате, отдельно от цепей памяти, PCI и прочего. Аналоговые цепи разделены DC-DC преобразователями. За счет этого удалось получить приемлемые уровни шумов и SFDR (согласно возможностям микросхем). Это так же позволяет разрабатывать несколько типов плат АЦП не изменяя цифровую часть. Рассматривали вариант более высокочастотных плат, но в производство не пустили, так как не было реального заказчика. Если интересно, то контакты есть на сайте. -

АЦП AD9643

McSava ответил Kranov тема в Схемотехника

На сайте Analo Devices есть все необходимое. В документации на микросхему есть примеры подключения для вариантов с ОУ или трансформатором на входе. Для трансформаторной версии даны варианты фильтрующей цепочки. Указаны рекомендуемые компоненты для тактирования и питания. В разделе отладочные платы есть схема отладочной платы для 96хх/66хх АЦП. -

Пользовательские регистры JTAG

McSava ответил scorp тема в В помощь начинающему

У Xilinx есть ChipScope Analizer. Можно настроить доступ к регистрам. Мы при отладке АЦП на BRAM делали память для на 1024 отсчета. Как это делается у Synopsys, к сожалению, подсказать не могу. -

что припаивать к земле С или L

McSava ответил CRADLE тема в В помощь начинающему

Для кварцевого фильтра значения не имеет, но при фильтрации питания и передачи постоянных уровней напряжения вариант с подключением индуктивности на землю и последовательном конденсаторе не пройдет. Ну а дальше, если нет разницы, то рисуют как привыкли. -

Вышел EE7.9.2

McSava ответил fill тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

В 7.9.1 такое тоже наблюдал. Решил, что намудрил где-то с настройками, ввел изменения "поштучно". -

Организация питания на PCIe плате.

McSava ответил Eastern тема в ISA/PCI/PCI-X/PCI Express

На напряжения +3,3В и 12В есть отграничения по току и по суммарной емкости нагрузки. Внимательно почитатйе их (PCI EXPRESS CARD ELECTROMECHANICAL SPECIFICATION, REV 2.0, Chapter 4. ELECTRICAL REQUIREMENTS). Если у вас x1 слот, то 12В не хватит даже при использовании DC-DC, не говоря уже про линейные стабилизаторы. Мы 5В заводили отдельным кабелем, типа для FDD или HDD. -

Амплитуда сигнала на выходе генратора

McSava ответил McSava тема в В помощь начинающему

Спасибо за ответы. Руководство читал, упоминания о действующем значении не нашел. -

Мы у Гальванотехники заказывали ПП на своем материале (Roger). Так что можно самим купить материал и отдать им. Сделали отлично.

-

Амплитуда сигнала на выходе генратора

McSava ответил McSava тема в В помощь начинающему

Но я могу подключить к выходу генератора 50 Омную нагрузку и смотреть амплитуду 1МОмным осциллографом на нагрузке, до 100 МГц полоса позволяет. -

Амплитуда сигнала на выходе генратора

McSava опубликовал тема в В помощь начинающему

На генераторе Г4-164 есть возможность выставления амплитуды в "дБ" или в "мВ". При выставлении амплитуды в "мВ" какое значение имеется ввиду - действующее или амплитудное? Другими словами, если к генератору подключить устройство с пятидесятиомным входом, на генераторе выставить амплитуду 500 мВ, то на осциллографе мы должны увидеть сигнал с 500 мВ или 500 мВ*1,41 = 705 мВ? В документации к Г4-164 не встретил упоминания о, том что напряжение выставляемой по индикатору является действующим. -

Высокоскоростной счетчик

McSava ответил A_MIKE тема в Цифровые схемы, высокоскоростные ЦС

У ACAM, есть несколько типов микросхем. Когда то использовали TDC-GP1. Программируемые, куча вариантов измерений. Цены не космические, но и не такие как на рассыпную логику. Были ветки и на этом форуме про них, пощите. -

Раздатчик клока

McSava ответил cerg19 тема в Цифровые схемы, высокоскоростные ЦС

У ОnSemi есть подобные разветвители. И у Texas Instruments. Какие у вас АЦП? Какие у них требования к фазовым шумам и джиттеру. -

очень может быть, что новички не имеют возможности публиковать подпись. Появится после 10 сообщений и перевода в группу участник. Так что писать некуда.

-

Мы используем. Подводные камни - очень кривая документация пока что (NXP). Для правильной нужно писать информацию в регистры которые не представлены в даташите. Это было видно из отладочных комплектов и мы сделали по образу и подобию написав не понятно что незнамо куда - заработало. Причем это касается как АЦП так и ЦАП. Но служба тех поддержки у NXP работает отлично, просто достает переписка по чайной ложке. Причем как нас так и их. P.S. У Linear есть такие микросхемы.