-

Постов

1 220 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные PCBtech

-

-

Часто вообще возникает ощущение, что графические принципиальные схемы - пережиток прошлого, и давно пора бы перейти на HDL-описания. Но, видимо, инерция в отрасли достаточно сильна.

HDL-описания хороши для цифровых схем.

ПЛИСы и процессоры с памятью прекрасно описываются. Фильтрующие конденсаторы по питанию - вообще песня.

Но аналоговая часть в HDL-виде, пожалуй, будет нечитаема и неудобна для наладки.

А ЕСКД позволяет схемы в виде текстового описания предоставлять?

-

Здравствуйте.

Появился интересный вопрос. Можно ли в orcad pcb professional использовать footprint уже трассированной платы?

Опишу точнее. Имеется pcb файл разведенной платы. Есть новая принципиальная схема на базе старой. Что там изменилось, допустим, я не знаю(например очень большая схема). В pcb файле footprint элементов, которых у меня отчасти нет. Можно ли как то вытащить эти элементы,чтобы не создавать самому эти .dra файлы недостающих элементов?

В OrCAD Capture есть очень хороший механизм сравнения схем. Можно увидеть отличия и в графическом виде, и в виде отчета.

-

Пробовал там сегодня - не получилось. В одном дизайне пишет, что не может открыть .psm файл и предлагает пройтись по нему DBDoctor-ом(с файлом, естественно, все в порядке). В другом дизайне сообщает, что компонент на плате является logic defined (или что-то в этом духе) и менять футпринт отказывается... Дальше пробовать не стал.

Так что какие-то подводные камни там точно есть и с этими действиями нужно сидеть и тщательно разбираться, как и что именно там можно сделать.

Не знаю, у меня получилось. Только там надо сразу менять и футпринт, и девайс файл.

-

Можно, если включена опция Groups. А как только ее выключить то двигать можно каждый элемент модуля отдельно и весьма просто зацепить что-то из состава модуля и передвинуть случайно. А потом плату хоть выбрасывай...

Да, для этого есть операция фиксации, Fix/Unfix.

-

Небольшая статья:

Новые возможности OrCAD Allegro QIR6 2018

-

Смысл очевидный - создать в одном целом механику модуля(разъемы, крепежные отверстия, зоны запрета размещения компонентов, зоны ограничения высоты компонентов, возможно еще что-то).

Subdrawing не поможет ничем, просто ту же конструкцию нужно будет создать в отдельном файле, вставить в основной, а что дальше, когда нужно будет ее передвинуть немного? Собственно только для удобства работы как с целым создание футпринта здесь и нужно.

Нет, понятно, что можно и другими способами решить, но не вижу в таких решениях преимуществ, кроме как отдельные компоненты в ВОМе.

Нет, я не про subdrawing, а про модуль MDD.

Его можно держать в библиотеке и ставить на плату при необходимости.

И передвигать можно как единое целое, если я не ошибаюсь.

-

Спасибо, сам отвечу. Косяки в символьном редакторе в Capture не исправили...

P.S. Такая эта ситуация уже становится неприличной.

А можете перечислить эти косяки?

-

День добрый.

Есть проект платы в Allegro 16.6 , нет схемы

Необходимо заменить микросхему (поменять посадочное место). Тонкость в том, что в плате несколько микросхем в одном корпусе, а поменять надо только часть.

Как у всех сразу поменять я понимаю (через Place->Updated symbols и т.д.).

Но как сделать замену только у части микросхем?

Заранее благодарен за помощь.

Logic - PartLogic

там можно индивидуально менять назначенный футпринт и девайс для любого рефдеса, с помощью кнопки Modify.

-

Если это Allegro PCB Editor, то меню Logic / Net Logic / выбрать цепь в окне опций и Rename

Плату сконвертировал из Altium, схема от нее в в pdf.Надо цепь с невнятным именем (типа NET00065) в приличное имя переименовать.

Не рисовать же всю схему в Capture.

Есть ли такая возможность?

Я попробовал сделать

File->Export-> Netlist w/Properties в файл, там ручками цепь переименовал,

затем

File->Import->Logic->Other-> файл,

так программа стала ругаться, что такие компоненты есть уже на плате

и цепи такие есть уже на плате.

Спасибо.

-

Тоже можно, но форма перерастет содержимое.

А в чем может быть смысл совмещения двух компонентов в один футпринт? Зачем это вообще может быть нужно?

Если именно для того, чтобы обеспечить заданное расстояние между ними - то это идеально решается именно через subdrawing,

или через "размножение фрагментов", где фрагментом является совокупность двух размещенных футпринтов на нужном расстоянии.

-

Спасибо за ответ.

А можно чуть подробнее про студентов?

Доступные онлайн-курсы описаны тут:

https://www.cadence.com/content/cadence-www...rses/85075.html

Для студентов и преподавателей университетов возможно предоставление бесплатного доступа к некоторым курсам.

Присылайте запрос на [email protected]

Certification_Presentation1.pdf

-

Добрый день.

Тоже интересует вопрос установки Cadence на linux.

Могли бы выслать документ?

-

Ааа, интересный случай. Два рефдеза в одном слое даже не приходило в голову делать, поэтому такую ошибку вижу впервые.

В общем ситуация выглядит так - либо использовать два отдельных разъема плюс отдельные крепежные отверстия со всеми вытекающими, либо использовать один компонент модуля, включающий в себя все нужные конструктивные элементы и смириться с повторами рефдезов. Просто создать схемный символ из двух частей - выглядеть будет как два отдельных разъема, а в РСВ войдет одним компонентом.

Эта задача решается не через один футпринт, содержащий два разъема, а через "повторяемый модуль" или "иерархический модуль".

Функционал зависит от того, используется ли OrCAD Professional или Allegro.

-

Спасибо!

Значит это действительно глюк.

Скиньте проект и описание глюка в саппорт Cadence. Может, починят как-нибудь.

Это явно слегка некорректное отображения окружности на экране.

-

Добрый день.

Существет ли (доступна ли) документация по разработке подложек (флип-чип корпусов) в SiP Allegro? Спасибо.

Документация по разработке подложек в SiP/APD Allegro есть.

Кроме того, можем организовать онлайн-курс самостоятельного обучения, но на английском языке.

Через Cadence Internet Learning Services.

Кстати, для студентов и преподавателей университетов это может быть бесплатно, если постараться.

-

Мы подготовили учебник (методичку) для тех, кто осваивает САПР Cadence Allegro PCB Designer (или OrCAD PCB Designer) версии 17.2.

Учебник по схемному редактору OrCAD Capture можно скачать тут:

https://docs.wixstatic.com/ugd/cc9e5f_ef33f...3e12b2818dd.pdf

Учебник по редактору печатных плат PCB Editor скачивается тут:

https://drive.google.com/open?id=1V3QD5mEEb...qA22_W1iA9CvrY4

Саму САПР OrCAD (демо-версию на 30 дней) можно запросить тут:

https://trial.cadence.com/orcad/signup

Либо можно скачать урезанную студенческую версию тут:

https://www.orcad.com/ru/resources/download-orcad-lite

Просим присылать обратную связь на [email protected]

(ошибки, неточности, пожелания, вопросы или дополнения)

-

Уважаемые , где можно посмотреть пошаговую инструкцию для установки Cadence в Ubuntu (ну или просто линукс)?

На сайте саппорта поискать "install allegro linux" - и найдется.

Файл называется Install_SPB_172_Linux.pdf

Могу выслать.

-

Здравствуйте!

Подскажите пожалуйста какая горячая клавиша отвечает за прозрачность и не прозрачность слоев?

Спасибо

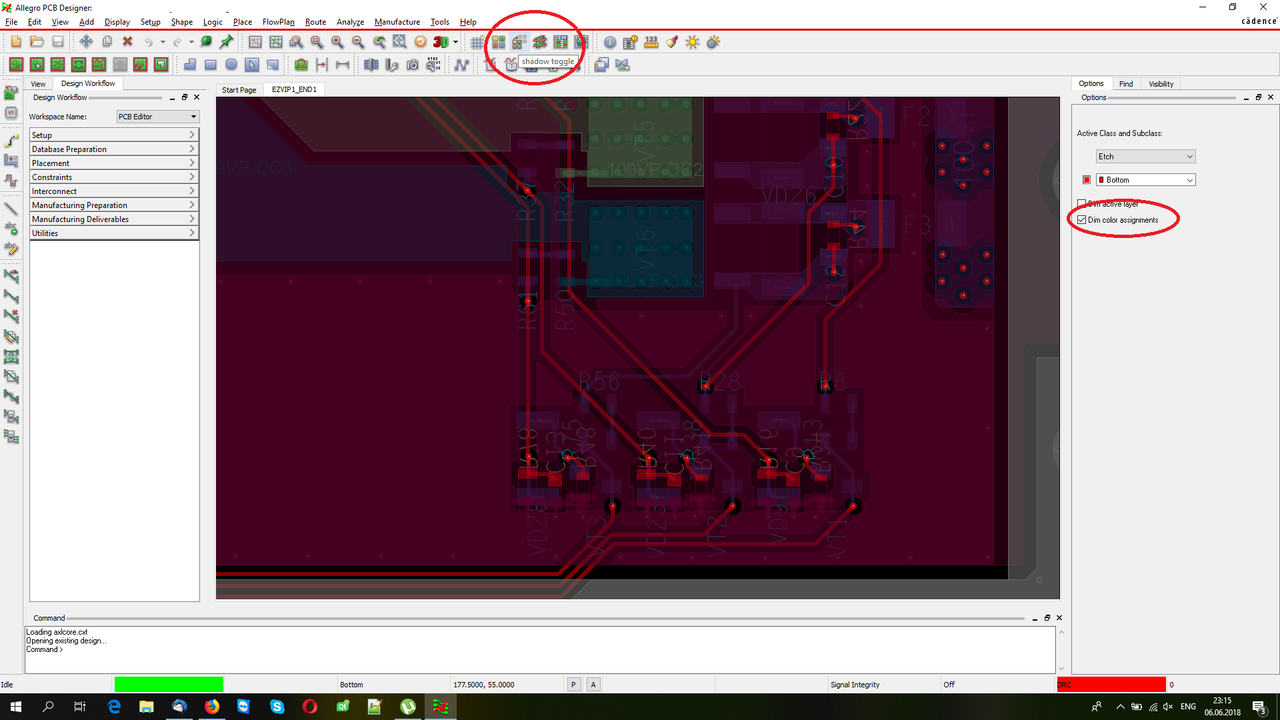

В Allegro 17.2 есть две удобных кнопки - Shadow toggle для снижения яркости и Dim color assignment для затемнения всех слоев, кроме текущего активного:

На них можно назначить и горячие кнопки, если надо - это несложно.

-

В процессе трассировки перепиновку/swap приходится делать неоднократно ( например при трассировке DDR) и удобнее делать это в brd и потом уже окончательный результат передавать swp файлом разработчику и грузить его в схему. Как в схеме можно предугадать куда мне удобнее перекинуть эту цепь? и что значит " свап на схеме"? И как-то этот вариант еще можно реализовать, если разработчик сам и разводит плату, но если это разные люди, то к разработчику не набегаешься....

Allegro FPGA System Planner вам в помощь.

-

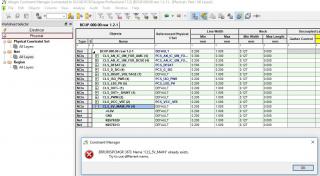

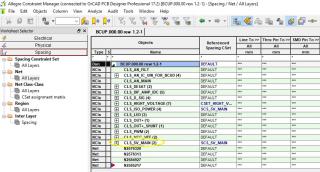

Может быть кто нибудь сталкивался с такой проблемой:

Пытаюсь переименовать Класс в Physical CM, допустим CLS_5V_MAIN_PH в CLS_5V_MAIN при этом выдается ошибка что класс с таким именем уже существует. Хотя на самом деле в списке классов Physical его нет(см.рис 1).

Однако этот класс есть в списке в списке классов Spacing(см.рис 2).

Как такое может быть, ведь наборы Классов для ограничений Physical и Spacing должны быть общие? Т.е. как я понимаю я должен видеть одни и те же Классы как в ограничениях для Physical, так и для Spacing, а в моем случае, получается что в Physical одни Классы, а в Spacin другие...

Помогите разобраться.

Рис.1

Рис.2

Когда вы создаете класс, вы можете указать, будет ли он общим для всех разделов, или будет существовать только в этом разделе.

-

НИУ МИЭТ и компания Cadence Design Systems приглашают Вас принять участие в работе научно-методического семинара по современным средствам проектирования электронных устройств.

Наименование семинара:

Проектирование систем в корпусе и печатных плат: платформы Virtuoso и Allegro с технологией 3D электромагнитного моделирования (Sigrity™)

Семинар организован НИУ МИЭТ при поддержке компании Cadence Design Systems (www.cadence.com).

Формат проведения семинара МИЭТ-Cadence 2018: Один день, презентация + вопросы и ответы.

Дата проведения семинара: 17 апреля 2018.

Цель Семинара – познакомить участников с новыми продуктами компании Cadence в области проектирования корпусов ИС, систем в корпусе и печатных плат, а также с методами расчета и анализа гетерогенных систем.

Темы семинара:

1. Моделирование печатных плат и корпусов ИС при помощи инструментов Cadence Sigrity.

Srdjan Djordjevic, ~ 2 часа. Язык доклада – английский (уточняется - возможно, русский).

Моделирование в режиме DC, совместный анализ токовых нагрузок и теплового состояния электронного модуля. Моделирование в режиме AC – извлечение полного импеданса в цепях питание–«земля». Частотный анализ цепей питания с поиском резонансов. Извлечение S-параметров (АЧХ) сигналов интерфейса DDR. Моделирование устройств типа Serializer/Deserializer (SerDes).

2. Технология 3D электромагнитного моделирования пассивных компонентов ИС. Martin Biehl,

20 мин. Язык доклада – английский.

Интеграция технологии 3D-электромагнитного анализа (Sigrity™) с Virtuoso® Layout Suite, для качественного извлечения моделей S-параметров цепей с пассивными компонентами на чипе и межсоединений, которые могут быть легко учтены при моделировании схемы в среде Virtuoso.

Для разработки пассивных компонентов на кристалле (например, спиральных индуктивностей, трансформаторов, симметрирующих трансформаторов) применяемых в радиочастотных интегральных схемах требуется высокоточный электромагнитный полевой анализ, который нужен для экстракции S-параметров с целью моделировании схем. Для достижения требуемой точности предпочтительным является метод конечных элементов (3D Finite Element Method FEM), однако часто требуется ручное вмешательство на этапе подготовки топологических данных ИС для моделирования. Интегрированный маршрут Cadence Virtuoso-3DEM позволяет разработчику ИС настраивать и моделировать пассивные компоненты и межсоединения непосредственно из среды Virtuoso с использованием технологии Sigrity 3DEM, что упрощает оптимизацию производительности радиочастотных компонентов.

3. От интегральной схемы к корпусу – особенности моделирования гетерогенных систем.

Martin Biehl, 30 мин. Язык доклада – английский.

Многие из современных аналоговых, радиочастотных и смешанных устройств обработки сигналов требуют интеграции нескольких ИС с различными технологиями изготовления для достижения требуемых целей в области производительности и т.п. Интеграция гетерогенных устройств (кристаллов) позволяет разработчикам достичь результатов, которые не могут быть легко получены с использованием монолитного подхода к проектированию ИС (SOC). В то же время гетерогенная интеграция ставит целый ряд новых задач для современных дизайнеров.

Узнайте, как Cadence использует платформу Virtuoso, среду Allegro и технологию Sigrity для создания оптимизированного маршрута, который автоматизирует многие этапы проектирования и верификации систем в корпусе с несколькими кристаллами, смешанными и RF сигналами. Демонстрация будет сосредоточена на применении этого метода для автоматизации процесса создания тестопригодных схем в Virtuoso непосредственно из топологии модуля или корпуса и извлеченных S-параметров на основе технологии Sigrity.

4. Обзор технологий корпусирования интегральных схем. Martin Biehl, 40 мин. Язык доклада – английский.

Введение и обзор современных технологий корпусирования ИС. Типы корпусов, такие как Lead-Frame (QFN) или BGA / LGA. Технология, при которой различные кристаллы монтируются на «флипчип» или с помощью проволочной разварки. Технологии Wafer Level Packages (WLP), Chip Scale Packages (CSP), Multi Chip Modules (MCM) или система в корпусе (SiP).

5. Платформа Allegro: трассировка и 3D-редактор. Компания PCBsoft. 3 часа. Язык доклада – русский.

Возможности и преимущества САПР Cadence Allegro для эффективной разработки сложных многослойных печатных плат. Allegro Venture PCB Designer: High Speed, Miniaturization, Analog/RF, Design Planning. Авто-выравнивание длин для групп сигналов. Авто-интерактивная трассировка. Авто-оптимизация схемы связей ПЛИС для ускорения трассировки.

Семинар состоится в НИУ МИЭТ 17 апреля 2018 года. Начало в 9-30. ауд 3103.

Проезд к месту проведения семинара: http://www.miet.ru/content/s/196

О Вашем решении и составе участников (компания, должность, ФИО, email) просим сообщить

до 14 апреля по электронному адресу:

[email protected] (в теме письма обязательно указать «семинар МИЭТ-Cadence 2018»).

Программа семинара:

09:30 – 09:45 Регистрация.

09:45 – 11:40 Тема 1; ~2 часа.

11:40 – 12:00 Тема 2; 20 минут.

12:00 – 13:00 Обед. 1 час.

13:00 – 13:30 Тема 3; 30 минут.

13:30 – 14:10 Тема 4; 40 минут.

14:10 – 14:30 Кофе – брейк, 20 минут.

14:30 – 16:00 Тема 5; 1,5 часа.

16:00 – 16:20 Кофе – брейк, 20 минут.

16:20 – 17:50 Тема 5; 1,5 часа.

17:50 – 18:00 Подведение итогов, обсуждение.

-

Все просто оказалось

1.Надо скачать

https://www.torproject.org/projects/torbrowser.html#windows

2. На arrow.com залогиниться (я на gmail.com почту использовал)

3. Ипользовать этот login в ORCAD cloud

3. Делаем проект в облаке

Только невозможно его на PC сохранить (я пока не знаю как)

Лучше логиниться через https://www.ultralibrarian.com/

вот тут

https://www.ultralibrarian.com/solutions/ca...d-capture-cloud

тогда, во-первых, есть доступ к библиотеке,

а во-вторых, оттуда можно получить 50% скидку на десктопную годовую лицензию OrCAD Standard,

и еще 3 месяца бесплатного UltraLibrarian.

Там же и скачать проект можно будет.

-

А в поддержку Cadence не обращались?

Уважаемые господа! Кто-нибудь работает с pdv.exe в 17.2 ?При открытии компонента графическое окошко, которое было в 16.2-16.6 не открывается по умолчанию.

Открыть его можно только тыкнув в graphic_editor/zoom/pan/full_screen

pdv.exe назойливо просит редактировать УГО в новодобавленной в 17.х приблуде

...\SPB_17.2\tools\bin\symboleditor.exe которую он норовит вызвать по любому поводу.

Редактировать в старом черном окошке практически не возможно.

При вводе в таблицу параметров, или нажатии на стрелочки "move" pdv.exe падает после 5-и

минут работы.

Это проявляется и на 10-й и на 7-й винде.

Кто-нибудь сталкивался с такой проблемой?

ЗЫ

пробовал на 17.2.30 и на 17.2.33 эффект одинаковый.

Только не говорите мне рисовать квадратики в "концепте" или переплывать под оркад.

:crying:

-

Нужна консультация по работе с инструментарием, поскольку разводил в каденс только 2-х слойные платы с USB

Кандидатов прошу писать в личку.

Спасибо!

В московском учебном классе PCB SOFT два раза в месяц проходят тренинги. Запись:

https://www.pcbsoft.ru/uslugi-vnedrenie

Подключение механических пинов к электрическому полигону

в Cadence

Опубликовано · Пожаловаться

У вас какая версия Cadence - 16.6 или 17.2?