-

Постов

1 220 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные PCBtech

-

-

Принципиальные схемы рисую в Orcad Capture 16.3, развожу в Orcad Layout 16.2

Очередная плата оказалась с очень большим количеством элементов и цепей.

При попытке создания платы в Layout процесс слетает явно из-за большого количества.

Пошел в обход - разбил плату на несколько частей. Каждая из этих частей создалась нормально, но при попытке склеить воедино (через merge) тот же результат, процесс вылетает.

В чем может быть проблема? Нехватка памяти? Компьютер Windows 7, оперативной памяти 4 Гига. Но Layout и жрет вроде немного.

Что посоветуете?

Купить OrCAD Standard 16,6/17.2 за 35 тыс.р. в год.

-

Во-первых, никак. Этот мастер просто позволяет посмотреть, как правильно должен называться пад.

Во-вторых, не насилуйте труп. Поищите новый PCB Libraries.

Или OrCAD Library Builder.

-

Добрый день. Есть вопрос по схемному редактору OrCAD Capture

Можно ли в схеме присваивать цепи своё имя, но при этом "гасить" красные названия этих цепей, чтобы не нагромождали схему? Просто к примеру есть дифпара, которая идёт вначале на резисторы, потом на дроссели а затем на защитную диодную сборку и как-то с одной стороны некуда эти надписи этих цепей там втулить, а с другой- по названию в CМ будет потом проще дифпары находить

Покрасить текст названия цепи в белый цвет.

-

Пришло письмо в почту, что Ultra Librarian теперь поддерживает

OrCAD Capture Cloud.

Вопрос: Как попасть в OrCAD Capture Cloud?

По всем ссылкам пишут Error 403 Forbinden.

Может кто-либо подскажет?

Может, через VPN?

-

Все включено

Все STEP-модели должны присутствовать в "пути" редактора, т.е. недостаточно, чтобы они были внутрь проекта подтянуты.

Проверьте, что пути не сбились.

Также рекомендуем настраивать ориентацию и точку привязки STEP-моделей "в ноль" относительно точки привязки футпринта.

Для этого можно пользоваться бесплатными 3D-редакторами, есть инструкция, как это удобно можно делать.

-

Спасибо за ответ. Изменение яркости и перекрас всех остальных цепей кроме нужной в темный цвет более-менее позволяет получить нужный результат.

Цепь уже разведена. Суть как раз в том, чтобы посмотреть как идет определенная цепь (или две-три дорожки) для анализа неисправности. Кажется это полезная функция была бы. Странно, что ее нет.

Ну как же "нет". Все есть. Вам же пояснили, как надо сделать.

1. Настраиваете "в минимум" движок Shadow mode:

2. Делаете поиск Find by Name для цепей, в панели Find:

3. Для погашения ненужных цепей ставите галочку Use selected objects for deselection:

4. Для отключения режима просто отключаете иконку Shadow Toggle:

Такой вариант работает для ваших целей?

Ну и не забываем нажать кнопку 3D, когда цепь выделена - очень удобно в новом 3D-редакторе ее посмотреть, именно отдельно, без других цепей.

-

В Москве, в учебном классе PCB SOFT, пройдет тренинг по начальному освоению схемного редактора и редактора печатных плат Allegro/OrCAD PCB Designer.

Занятия продлятся 3 дня - с 19 по 21 февраля.

В результате слушатели получат базовые знания о маршруте проектирования печатных плат Allegro - от схемы к топологии и выводу производственных файлов.

В том числе будет освоено задание правил и ограничений в табличном виде через Constraint Manager,

включая скоростные интерфейсы и дифференциальные пары.

Стоимость тренинга обсуждается индивидуально.

Запрос дополнительной информации: [email protected]

-

Компания PCB SOFT (дистрибьютор Cadence) примет участие в выставке «Автоматизация. Электроника-2017» в г.Минск, с 28 февраля по 2 марта.

Также (на случай, если кто-то не видел уведомления в параллельном форуме) PCB SOFT проведет 3 марта (в субботу) в Минске семинар для разработчиков печатных плат.

Сайт выставки:

http://automation.minskexpo.com/

Сайт регистрации на семинар:

https://www.pcbsoft.ru/reg-seminar-sigrity

Номер стенда на выставке - B1. Будем рады видеть вас.

На выставке разработчики печатных плат смогут познакомиться с возможностями САПР печатных плат верхнего уровня Cadence Allegro и ее "облегченной" недорогой версией OrCAD, а также с возможностями по моделированию проектов в системах PSpice и Sigrity.

Также можно будет увидеть работу конвертера проектов из систем P-CAD и Altium в Cadence Allegro PCB Designer.

Применение САПР компании Cadence позволяет разработчикам выйти на новый уровень проектирования печатных плат, с достижением максимального качества и эффективности разработки электронной аппаратуры.

На стенде компании PCB SOFT можно будет получить каталог программных продуктов Cadence, а также проконсультироваться со специалистами по вопросам проектирования и моделирования современных печатных плат.

Источник:

-

Уважаемые коллеги, приглашаем посетить бесплатный семинар по проектированию и моделированию DDR.

Минск, 3 марта (суббота, но рабочий день).

Программа докладов

10:00 Компания PCB SOFT: представление команды специалистов и анонс мероприятий на 2018 год. Краткий обзор услуг группы компаний PCB technology.

10:15 Возможности и преимущества САПР Cadence Allegro и OrCAD для эффективной разработки сложных многослойных плат. Новая сборка Allegro Venture: функции High Speed, Miniaturization, Analog/RF, Design Planning. Возможности управляемой автотрассировки. Авто-выравнивание длин для групп сигналов DDR. Авто-интерактивная трассировка и планирование прокладки шин. Авто-оптимизация схемы связей ПЛИС для ускорения трассировки.

12:00 Перерыв

12:30 Рекомендации по трассировке скоростных интерфейсов на печатных платах. Правила трассировки DDR2/3/4, различные виды топологий, рекомендации по разводке DDR и настройке правил в САПР, на примере Cadence Allegro.

13:30 Обед

14:30 Примеры моделирования на реальных проектах печатных плат со скоростными интерфейсами. Назначение и состав пакетов Cadence Sigrity. Сборки Sigrity. Цены и специальные предложения для Беларуси на приобретение САПР Cadence OrCAD/Allegro/Sigrity.

15:00 Рекомендации по моделированию целостности питания. Совместное моделирование питания по постоянному току и тепла на печатной плате. Анализ проектов печатных плат, присланных слушателями семинара (экспортированных из различных САПР ПП).

16:00 Кофе-брейк

16:30 Рекомендации и примеры моделирования целостности сигналов на печатных платах. Анализ проектов печатных плат, выполненных слушателями семинара в различных САПР.

18:00 Окончание семинара

Стоимость участия в семинаре – БЕСПЛАТНО.

Слушатели семинара могут промоделировать свои проекты и получить рекомендации по их улучшению в рамках семинара, независимо от типа используемых САПР. Для этого необходимо заранее прислать проекты (экспортированные в формат ODB++ или P-CAD ASCII) на электронный адрес: [email protected] Инструкции по экспорту проектов высылаются по запросу.

Обязательная регистрация – на сайте: www.pcbsoft.ru

Количество мест ограничено.

Контактный телефон для уточнения информации 8 (499) 390-14-29 Светлана

Дата проведения семинара: 3 марта 2018 года, суббота.

Адрес места проведения семинара: Конференц-зал гостиницы «Беларусь», г. Минск, ул. Сторожовская, 15

Пакет Cadence Allegro, демонстрируемый в рамках семинара как инструмент для проектирования плат со скоростными интерфейсами, поставляется в конфигурациях разной стоимости (от 2.5 до 35 тыс.USD), в зависимости от функционала:

• OrCAD PCB Designer Standard – схемный редактор и базовый редактор топологии.

• OrCAD PCB Designer Professional – добавлены функции автотрассировки и пред-топологического моделирования.

• Allegro PCB Designer + опции – добавлены функции автоматизации различных действий, позволяющие с максимальной эффективностью трассировать платы.

Пакет Cadence Sigrity, который будет использоваться в качестве инструмента моделирования в рамках семинара, включает в себя несколько приложений, основные из них:

• PowerDC;

• PowerSI;

• OptimizePI;

• SystemSI Serial Link Analysis (SLA);

• SystemSI Parallel Bus Analysis (PBA);

• 3DEM.

-

Добрый день.

Подскажите точные ограничения в Allegro 17.2 Lite

Спасибо!

http://www.orcad.com/resources/library/orc...t-sheet172-2016

-

Всем привет. Решил тоже заглянуть и поприставать к Вам (ко всем) с вопросами по трассировке DDR. Кто ответит - буду весьма признателен.

Вот вопросы:

1. Подскажите, из всех цепей групп адресов, клока, даннх, команд какие цепи должны быть самые длинные? Цепи клока? Если да, то на сколько длиннее самой длинной цепи в пределах одного байта?

2. Слышал что у клока есть требование к определенной длине линий, например 2,25 дюйма (информация с IMX6DQ6SDLHDG.pdf) Хотя это может быть требование именно для клока с применением процессора IMX6DQ6SDLHDG

3. Обязательна ли трассировка всех цепей одного байта в одном слое для DDR3? Или можно в смежных слоях с общим опорным слоем делать и достаточно?

4. Что если в части опорного слоя применить плейн питания, можно так (я по краям плейна 0,01 мкФ конденсаторы по всему плейну постовлю от перепадов напряжения по плейну)

А у вас есть наша презентация с рекомендациями по проектированию плат с DDR?

-

Даа, спасибо. Не совсем это имел ввиду, но помогло)

Своп пинов конечно использовал, но поодиночке, т.е. выбрал пин, подсветил эквивалентные выводы, перекинул.

Интересовала именно автоматическая оптимизация связей с помощью эквивалентных выводов, собственно команда Autoswap, как раз идущая следующим пунктом (почему то прошляпил ее).

Попробовал, работает. Но, насколько я понял, она применима ко всему дизайну или к отдельным комнатам. А как оптимизировать связи только между несколькими выбранными компонентами? Объединить их в комнаты?

Попробуйте Allegro FPGA System Planner.

-

Очень полезный файл, спасибо!

В тексте есть такая фраза "Вы можете скачать из интернета программы на языке skill, которые расширят функционал вашего редактора. Обычно они имеют расширение имени файла *.il".

Подскажите ресурс, где можно найти подобные программы.

В частности интересует возможность автоматического поворота текста "Component Value Top/Bottom".

Например, в папке с установленным OrCAD - куча примеров:

C:\Cadence\SPB_17.2\share\pcb\examples\skill

-

Здравствуйте, форумчане!

Подскажите пожалуйста, кто-нибудь пробовал писать какие то скрипты для оркада на тцл? вопросы буквально начальные, в чем писать, в блокноте++ или может есть более интерактивные/наглядные программы для такой писанины? Может кто то натыкался на учебные видео применительно к оркаду и тцл? вобщем с чего начать то. пока читаю capture tcltk extensions pdf, но надо уже чето пробовать писать, чтоли).

благодарствую за мудрые напутствия.

Notepad++ вполне годится.

В папках с установленным OrCAD есть много готовых скриптов, там можно много полезного найти.

-

Спасибо, буду пробовать. Других вариантов нет.

Вот тут инструкции по освоению:

https://www.pcbsoft.ru/tutorials

Особенно вот эта:

Быстрый старт Allegro/Capture

-

и что теперь делать не знаю. Переходить на новую версию типа Allegro ну никак времени нет, поскольку как я понял придется перерисовывать все футпринты и полностью перерисовывать плату, а это более 1200 соединений и более 750 элементов.

подскажите как решить проблему?

Библиотеки и проекты из Layout по идее должны нормально импортироваться в Allegro 16.6

Может быть, с минимальными корректировками.

-

Вышел OrCAD/Allegro PCB Designer QIR5 (версия 17.2).

Теперь можно экспортировать 3D PDF прямо из OrCAD/Allegro.

При экспорте все STEP-модели, задействованные в проекте, должны присутствовать в библиотеке, на которую указывает путь STEP PATH редактора.

Пример проекта в OrCAD 17.2 и выходного 3D PDF-файла:

https://yadi.sk/d/jeFIWnEM3QXXps

-

рисую путь фрезы и в 3D ничего не видно:

А отступ в полигоне сделан?

-

Наверное, надо по-очереди их апдейтить, не все компоненты сразу.

Если компонент удалить, то дорожка, привязанная только к нему, остается без цепи.

Переходное отверстие тоже. Тогда они присоединяются к полигону, который переходным отверстием протыкается.

В вашем случае GND.

Потом поверх дорожки размещается новый компонент, после апдейта, но уже поздно, цепь уже прицепилась к GND.

Видимо, как-то так все происходит.

Добрый деньПытаюсь в Аллегро 17.2, с последним хотфиксом заменить пару футпринтов на обновленные через Place->Update Symbols. Но возникает проблема: в процессе обновления некоторые цепи, идущие от одного компонента к другому, превращаются из сигнальных в GND.

При этом Shape c именем GND, через которую проходит эта трасса с via на ней, делается незалитой и via оказывается присоединенной к этой цепи. Даже если ее переделать в статическую.

Разумеется, пытался сделать эту net как Fixed, но тогда плата отказывается обновляться - хотя, казалось бы, зачем это обновляемому компоненту...

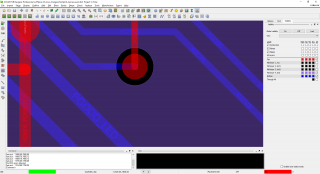

То есть выглядит эта радость как-то вот так (фиолетовый плейн - GND):

До обновления:

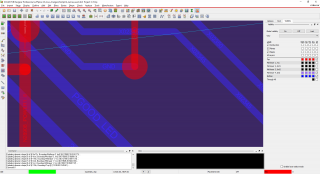

После обновления футпринтов: (резинка сверху - от бывшего соединения падов прежней дорожкой, которая теперь GND и пады потеряли контакт)

Как видно в логе, это обновление футпринтов включает обновление затронутых Shapes. Зачем это обновляемым футпринтам - опять же, не понятно.

Вопроса, на самом деле, два - про причину и про борьбу с последствиями.

1. Откуда это берется и как это устранить?

2. Если непонятно, откуда берется, то что надо попробовать запретить в настройках, чтобы не дать Update Symbols так пакостить?

-

Ну так у него Пикад 2002. Возьмет? В 2006 у него глюки

Да, возьмет.

-

Подскажите лучше, какой тулзой Вы для этого импорта пользуетесь :) Если маршрутом PCAD->Altium->Allegro, или PCAD->PADS->Allegro, то результаты такие же, просто геморроя с маппингом слоев меньше.

У нас свой прямой конвертер из P-CAD 2006 ASCII в OrCAD/Allegro.

Написан на языке SKILL.

-

Обновление:

Огромное спасибо всем за советы. Помогло, как бы это не казалось странным, загрузка проекта в PCAD 2002, как было указано в заголовке файла PCB. 69 ошибок всего осталось, и они мелкие. Проблема решена. *.net файла у меня нет, ну да 69 проводников уже легко ручками дорисовать.

Вторая часть Мерлезонского балета - это попытка втянуть дизайн через PDIF в Аллегро. То есть втягивается-то нормально, но, поскольку в PDIF нет constraints, то не происходит и соединения с полигонами: дефолтная толщина цепи = 0, clearance = 0 и вместо connectivity получается куча ratsnest-ов и DRC ошибок в местах соединения полигонов с проводниками и отверстиями. Это вопрос уже, наверное, в Кейденсовскую конференцию.

Не надо PDIF, сохраните PCAD ASCII и пришлите мне, я вам сделаю BRD файл Allegro.

-

Есть плата в PCAD, не очень-то и простая (DDR2, PCIe - 20 страниц схематики итого). ......

Что посоветуете? Я в Альтиуме-Аллегре больше работаю, может для PCAD есть какие-то стандартные решения...

Есть конвертер из PCAD2006 ASCII в Allegro PCB.

Перекиньте мне плату, я попробую сконвертировать.

Потом в Allegro есть функция в меню "довести трассы до центров площадок", она 99% ваших проблем должна решить.

Ну и корректировать проект с DDR2 в Allegro гораздо проще и приятнее, чем в PCAD/Altium.

-

Сборник русскоязычных статей по Cadence

в Cadence

Опубликовано · Пожаловаться

Пожалуйста:

https://www.pcbsoft.ru/pspice-tutorials