-

Постов

1 220 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные PCBtech

-

-

Присылайте проект на [email protected] и опишите проблему с четким указанием координат - специалисты посмотрят.

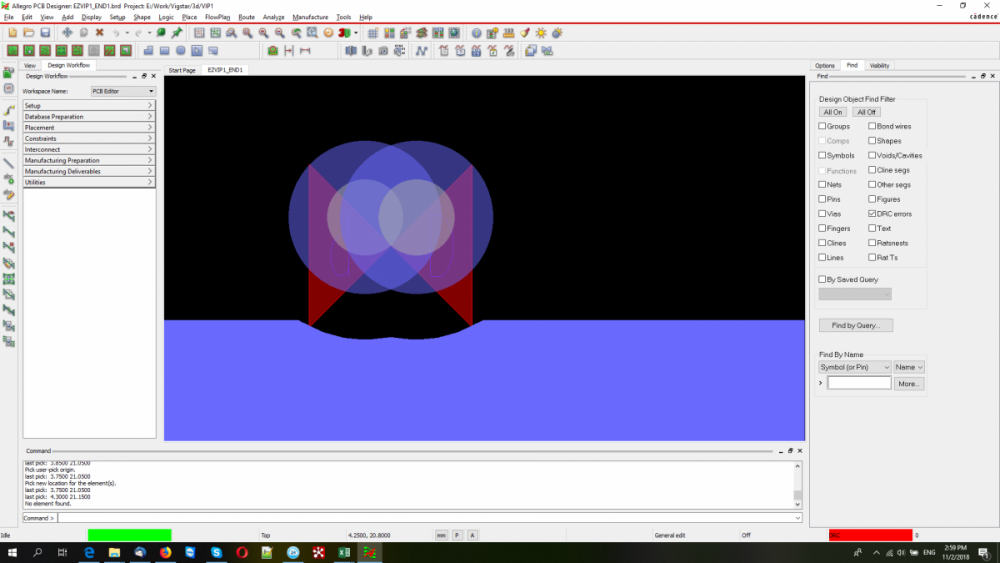

Укажите, чего именно хочется добиться в настройках, т.к. пока это не очень понятно - у вас на картинке много разных ситуаций. -

-

-

А большая - это тоже via или pad?

-

-

-

2 minutes ago, mwuser said:

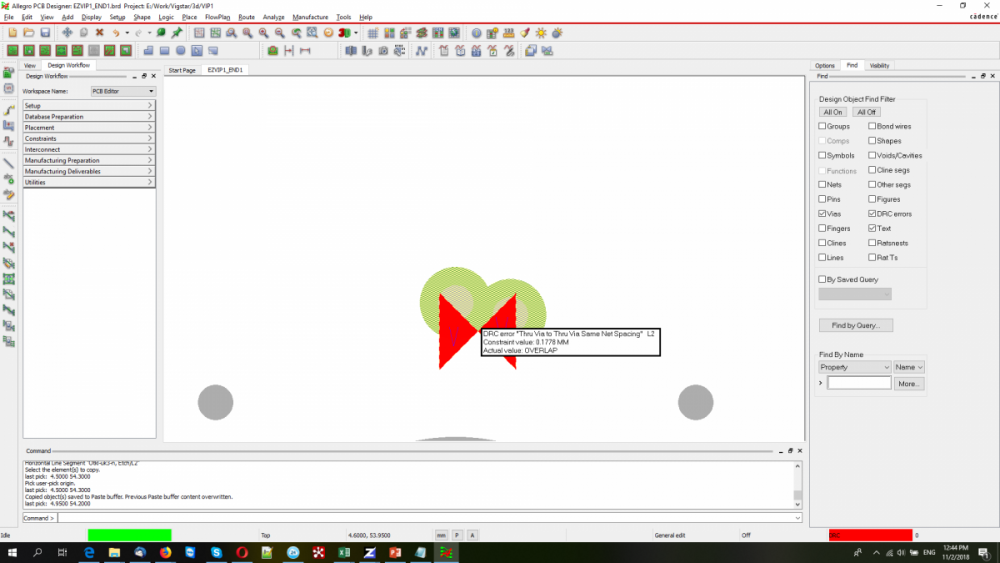

Да, конечно, но по идее DRC должен это показывать

Spacing - это технологическая, в общем-то, проверка, то есть зазоры не должны быть меньше определенного значения, чтобы не возникло проблем на производстве печатных плат или монтаже.

А если via уже контактируют, как это у вас сделано - тут не идет речь про проблемы производства, правильно?

Что именно в данном случае вас волнует, к каким проблемам приводит данное наложение одной via на другую? Почему САПР должна это обнаруживать?

И правильно я понимаю, что тут не via - via, а via наложено на mechanical pad?

-

11 minutes ago, mwuser said:

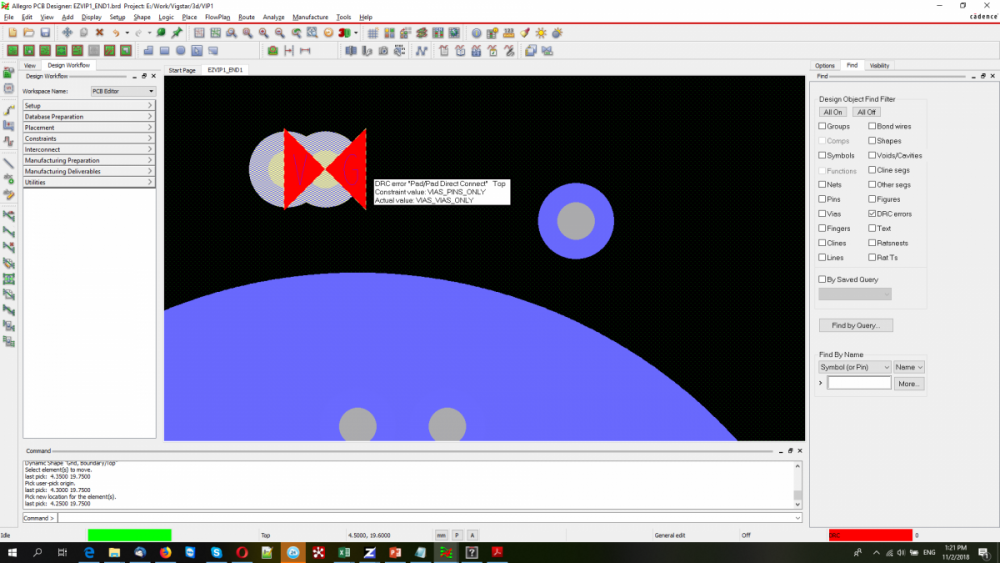

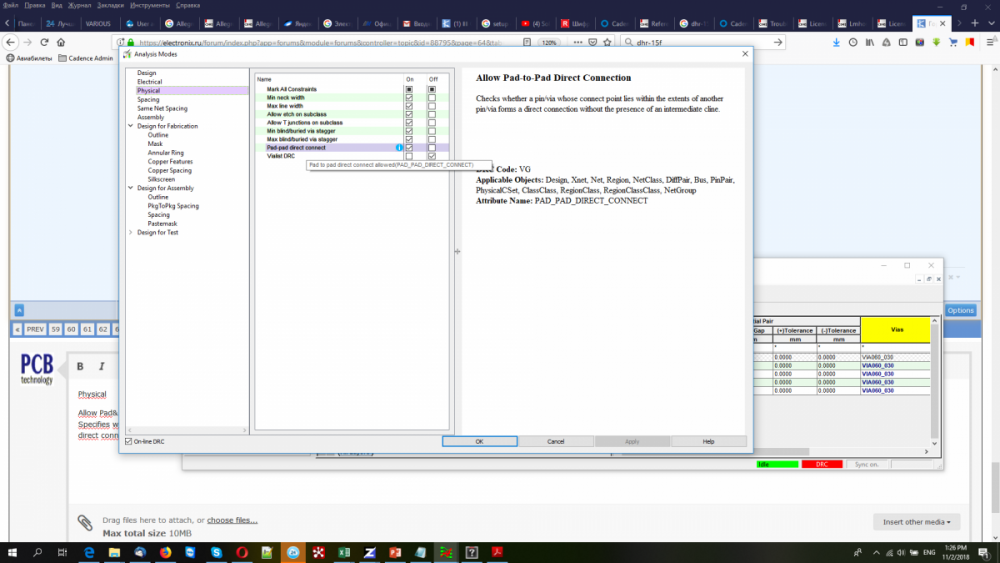

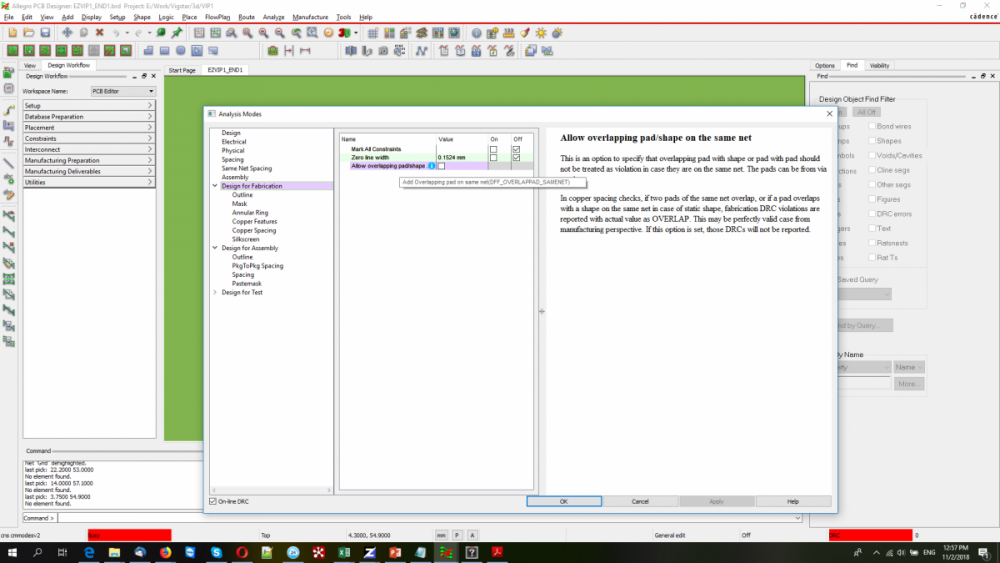

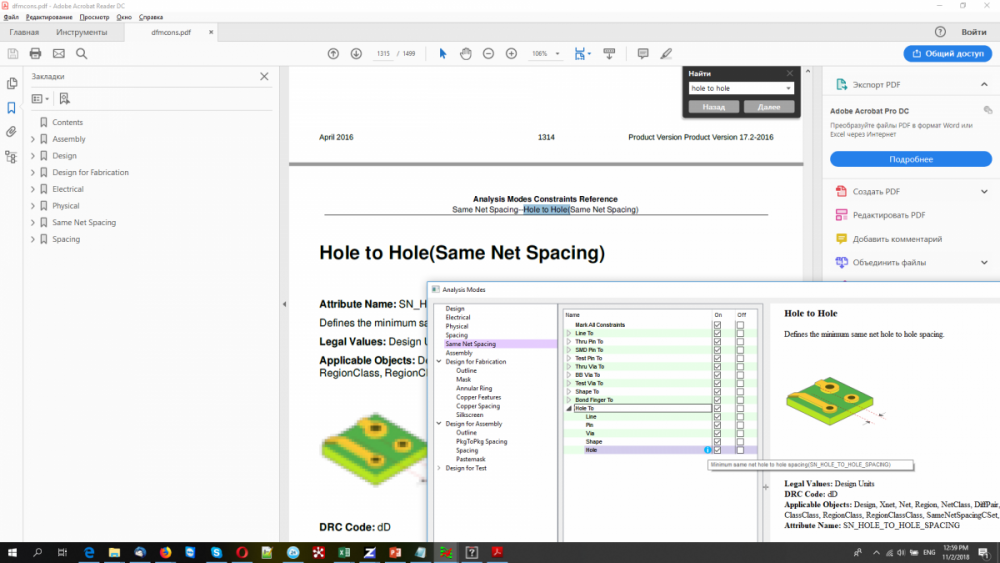

Здравствуйте, не могу понять почему не работает DRC для Constraints - Same Net Spacing для via?

Потому что у вас уже не Spacing, а наложение, правильно?

-

1 hour ago, KAlexn said:

А ларчик просто открывался. Я пытался файл сохранять в папке с документацией, а нужно просто в папке с проектом.

Программисты не допилили?

Может, русское название папки было. Не исключаю, что с этим могут быть проблемы...

-

24 minutes ago, KAlexn said:

3D Canvas выдает конечно красивые картинки, но только вот как их вывести в pdf файл. Иногда монтажникам нужно показать "живую картинку".

File=> Export в PDF 2D ничего не выдает, в PDF 3D выдает ошибку. Через другие форматы не пробовал.

Какая у вас версия и хотфикс? Скриншот не пробовали сделать? Это может помочь для начала. Но вообще экспорт в 2D PDF и в 3D PDF работает неплохо.

Только надо отключить внутренние слои платы, их все равно не видно, а объем файла сокращают.Экспорт в 2D довольно неплохо выводит картинки. Прилагаю пример проекта и PDF-файла:

https://yadi.sk/d/D7diCykKp_Acrw https://yadi.sk/d/D7diCykKp_Acrw

А экспорт в 3D для сложных плат работает медленно (ну, примерно полчаса на ноутбуке у меня уходит на создание файла),

и PDF-файл получается огромный, около 100 Мб, что, в общем-то, понятно - там же каждый проводничок и каждое отверстие сделано в 3D.

Думаю, правильнее в такой ситуации давать монтажникам вьювер Allegro 3D - он бесплатный. Пусть просматривают ваш исходный проект - это работает быстро и удобно.https://www.cadence.com/content/cadence-www/global/en_US/home/tools/allegro-downloads-contact.html

Allegro/OrCAD/SIP/MCM FREE Physical Viewer

Но так, для примера - вот простенький проект, сделанный в OrCAD, и его 3D PDF.

https://yadi.sk/d/OCSw56-C0Gf-lw

https://yadi.sk/i/m1JrGLNHhfKr3g

-

-

Just now, FabulouS said:

Где там? Вот тут?

Где тут задавать настройки?

Да. Во-первых, вам надо поставить ghostscript, чтобы печатать PDF.

Во-вторых, взять у PCBSOFT скорректированный скрипт и подложить его в Cadence Allegro вместо того, который там лежит. -

19 minutes ago, FabulouS said:

В книжке нашел вот что:

"Фактическая толщина линий зависит от принтера и масштаба схемного листа. Чтобы обеспечить более точное соответствие требованиям ГОСТ при печати, можно применить специальный постпроцессор, который заменит ширину линий при выводе в файл формата PostScript на требуемую по ГОСТ."

Есть ли где-то пример работы с постпроцессорами?

Там просто немножко дописали скрипт, который выводит PDF-файл из Capture. Скрипт написан на языке TCL.

-

-

On 10/10/2018 at 9:13 PM, FabulouS said:

Прошу прощения, если создал тему не в том разделе, но только тут увидел явную ветку про Cadence.

Здарова, ребят. Кто может помочь разобраться с OrCAD'ом по-мужски?

1.* Почему я не могу выбрать доп. опции анализа (см. картинку)?

Возможно, мне что-то ещё не доступно, но я об этом пока не знаю...

2. Есть ли русскоязычная книжка по последним версиям OrCAD'а, аналогичная книжке по микрокапу от Амелина М.А и Амелин С.А. (можно и англоязычную, но чтобы доступно было объяснено)?

3. Есть ли возможность добавления для компонента различных УГО? В микрокапе есть такая опция - shapegroup (см. картинку). Если есть, то как это реализовать?

4. Есть ли в оркаде возможность отключать часть схемы, как в микрокапе? Если есть, то как это сделать?

5. Можно ли в микрокапе создать библиотеку из одних УГО (блоки функциональных схем)? Хочу чертить функциональные и структурные схемы по ГОСТу (ГОСТ 2.737-68 ЕСКД. Обозначения условные графические в схемах. Устройства связи)

Примечание:

* - Я бы рад лицензию купить, да денег не хватит на неё. Использую пиратку.

Использую пиратку.

Заранее благодарю за ответы.

1. Возьмите лицензию OrCAD Lite или OrCAD Trial, там есть PSpice AA - почти все функции.

2. Есть - на сайте pcbsoft.ru в разделе "Публикации"

https://www.pcbsoft.ru/uchebnik-allegro-orcad

3. Можно делать как минимум 2 УГО для компонента - обычный и альтернативный.

4. Отключать часть схемы можно при моделировании в OrCAD PSpice - то есть можно выбрать только ту часть схемы, которая подлежит моделированию.

И добавить к ней, например, источники сигнала и все необходимое именно для моделирования.5. В Оркаде можно сделать библиотеку из одних УГО, и вполне по ГОСТу.

Насчет лицензии - сейчас есть спец.предложение на OrCAD Standard - всего 20 тыс.рублей за год работы.

Не могу поверить, что это такие большие деньги для разработчика электроники... -

30 minutes ago, Flood said:

Это и есть DE-HDL, просто обновленный? Или что-то другое?

Странно, но я как-то искал, но не смог найти никаких внятных скриншотов SDA. Было бы интересно посмотреть что там и как оно выглядит.

Если кто-то из пользователей Cadence Allegro хочет потестировать новый схемный редактор SDA, напишите нам на [email protected]

и мы дадим необходимые информационные материалы, и рекомендации о том, как попробовать новый редактор в деле.

-

Интересно, планируется ли обозримом или не очень будущем реализация маршрута Orcad под linux?

Allegro работает под Linux.

Новый схемный редактор SDA вроде тоже.

Вам нужен именно схемный редактор Capture под Линуксом, или цель какая-то другая?

-

Хорошие новости.

Теперь PCB Library Expert поддерживает формат библиотек HKP для Xpedition и PADS Professional.

Для тех, кто пользуется разными САПР ПП на предприятии, например, P-CAD и PADS у разных разработчиков,

теперь есть возможность вести единую библиотеку футпринтов и 3D-моделей, общую для обеих САПР.

Подробности:

https://www.pcbsoft.ru/pcb-library-expert

-

Помогите справиться с ентой бедой

Кто-то съел всю память.

-

Используйте утилиту TDD для оформления по ГОСТ. Она прекрасно берет BOM из Capture.

Вопрос:- можно BOM из Capture генерировать,

тогда надо нужные поля указывать.

- можно BOM из PCB Editor генерировать

И в том, и другом случае не все устраивает,

приходится ручками файл WORD (Перечень элементов)

составлять, ошибки пролезают.

Монтажникам лучше давать BOM condensed, так просят.

Может подскажете, как правильно это делать,

может файл примера BOM выложите.

Спасибо.

-

Приглашаем специалистов по печатным платам посетить наш стенд на выставке Армия 2018 в Кубинке.

Вы сможете обсудить с нашими инженерами насущные задачи и проблемы,

связанные с разработкой сложных многослойных плат,

выбором материалов, гибридных структур, параметров микроотверстий и т.д.

Можно также обсудить вопросы перехода с PCAD на новую версию САПР Cadence Allegro

(особенно для плат с большими ПЛИС, скоростными интерфейсами и DDR-памятью),

трансляцию проектов плат и библиотек, освоение PCB Editor,

а также моделирование ваших схем и плат.

Ждём вас на стенде 4b9-2,

Павильон D, угловой стенд справа, напротив стенда Министерства Обороны.

Вообще на выставке есть на что посмотреть, как в самих павильонах,

так и снаружи. Советую сходить, если кто-то не был.

Выставка продлится до конца этой недели.

Доехать можно на бесплатных автобусах

от станций Голицыно и Кубинка-1.

-

PCB Library expert.

Невозможно получить разные размеры в слоях Paste Mask и Solder Mask падстека !

Прога делает их одинаковыми !

Есть ли решение ?

Режим - Footprint -> Dimensions-> Use manufacturer's recommended dimensions

Обратитесь в поддержку.

Какая версия продукта? Какое обновление скачано? Какие параметры вы вводите и какой тип компонента выбираете?

-

Возможно, но таких матчгрупп 8 штук, половина из них работаю адекватно, половина нет. Попробую их переформировать, спасибо.

Насколько я знаю, в сентябре будет тренинг по проектированию DDR, там подробно рассказывается про то, как настраивать матч-группы.

-

Попробуйте вот эту древнюю инструкцию.

Currently you cannot automatically route tandem differential pairs in Allegro PCB Editor/Router, but this can be accomplished manually. The rules setup in Constraint Manager will not have any effect when routing the differential pair on different layers though.

To route a differential pair on tandem layers follow these steps (assuming the routing will be done on the top layer and layer 2).

1) Pick Net-1 of the differential pair and start the route, right mouse button (RMB) and select "Single Trace Mode".

2) Route the single trace just a small segment on the top layer, left mouse click to add a corner , right mouse click and select done.

3) Select Net-2 of the differential pair, swap the route layer to layer 2, route Net-2 to where you ended Net-1 of the differential pair and add a corner to coincide with the net on the top layer, right mouse click and select done. You should now have the segment on the top layer for Net-1 and the segment for Net-2 on layer 2 exactly on top of each other.

4) Select Net-1 or Net-2, right mouse click and unselect "Single Trace Mode", the differential pair will now route together. Finishing the route works the same way as when beginning the routing of the differential pair on the same layer.

Горячая линия по САПР Cadence Allegro

в Cadence

Опубликовано · Пожаловаться

Интересно, давайте глянем проект. Но это вы смотрите все же VIA-VIA. Попробуйте эту проверку отключить и смотреть HOLE-HOLE, вас же интересует этот параметр в первую очередь, верно?

Кстати, есть еще проверка на дублирование отверстий - т.е. если центры отверстий совпали, будет флажок.

Поэтому:

а) точно укажите, какие ситуации вам надо отловить флажками

б) пришлите проект с этими ситуациями, с указанием координат по каждой ситуации

в) мы посмотрим и дадим рекомендации по настройке DRC