rloc

Модератор-

Постов

3 197 -

Зарегистрирован

-

Победитель дней

12

Весь контент rloc

-

Попробую показать на примере, а Вы сами потом попытаетесь это проверить. Допустим, у нас есть два примитива в *.ucf: INST "A/A1" RLOC = "R0C0" ; INST "B/B1" RLOC = "R0C1" ; или другая, эквивалентная запись: INST "A/A1" HU_SET = "BLOCK1" ; INST "A/A1" RLOC = "R0C0" ; INST "B/B1" HU_SET = "BLOCK1" ; INST "B/B1" RLOC = "R0C1" ; где "/" - иерархический символ В этом случае A1 и B1 будут располагаться, где угодно, потому что принадлежат разным блокам A и B соответственно, даже не смотря на то, что каждому присвоено одинаковое иерархическое имя - "BLOCK1". Теперь немножко изменим запись на INST "A/A1" U_SET = "BLOCK1" ; INST "A/A1" RLOC = "R0C0" ; INST "B/B1" U_SET = "BLOCK1" ; INST "B/B1" RLOC = "R0C1" ; или INST "A" RLOC = "R0C0" ; INST "A/A1" HU_SET = "BLOCK1" ; INST "A/A1" RLOC = "R0C0" ; INST "B" RLOC = "R0C0" ; INST "B/B1" HU_SET = "BLOCK1" ; INST "B/B1" RLOC = "R0C1" ; или INST "A" RLOC = "R0C0" ; INST "A/A1" RLOC = "R0C0" ; INST "B" RLOC = "R0C0" ; INST "B/B1" RLOC = "R0C1" ; Теперь, в первом случае, мы сказали, что A/A1 и B/B1 - это один и тот же блок ("BLOCK1"). Во втором и третьем - просто указали, каким образом скрепить два отдельных блока, в итоге для A/A1 R0C0+R0C0=R0C0, для B/B1 R0C0+R0C1=R0C1. Более подробно читайте в документе "Constraints Guide", в разделе Constraint Types/Placement Constraints Если проблема не в этом, будем разбираться дальше.

-

Другие модули абсолютно не причем. Все зависит от иерархии, выхода здесь два: 1) изначально ищете в опциях синтезатора исключение иерархии и повторяете свой путь заново 2) в уже полученном *.ucf назначаете дополнительно всем инстанциям атрибут U_SET или каждому иерархическому уровню в целом свой отдельный RLOC

-

Работы провел много, молодец. Для относительно небольших проектов вполне допустимо. По своему личному опыту рекомендую в самом проекте применять RLOC'ки. Преимуществ масса: 1) полный контроль над проектом 2) высокая скорость синтеза и компиляции 3) независимость от версий синтезаторов и компиляторов 4) временные ограничения выполняются вне зависимости от занимаемого объема 5) значительно меньшее энергопотребление за счет коротких связей 6) легко сделать свое IP-core в виде *.edn, *.vhd(wrapped), *.ngc

-

Тюнинг DCM Virtex-4

rloc опубликовал тема в Работаем с ПЛИС, области применения, выбор

Как всем известно, DCM в Xilinx Virtex-4 состоит из 2-х отдельных петель ФАПЧ с общим входом и разными выходами: DLL и DFS. Первая из них (DLL) умеет делить входную частоту на разные коэффициенты, умножать на 2 и поворачивать фазу на фиксированные значения, обеспечивая при этом низкий джиттер. Вторая из них (DFS) умеет только умножать на дробный коэффициент (не будем принимать в расчет поворот фазы на 180), обеспечивая при этом хуже джиттер и немного ниже максимальную выходную частоту. Также всем известно, что DCM можно динамически переконфигурировать. Не буду останавливаться на подробностях, а сошлюсь на следующие документы: Dynamic Reconfiguration of Functional Blocks Virtex-4 Configuration Guide Reconfiguration Techniques/Dynamic Reconfiguration of Functional Blocks (DRP)/DRP DCM Implementation Из этих документов, а также из других источников, можно найти информацию о некоторых программируемых регистрах: DFS_MULTIPLY DADDR = 0x50 DI[4:0] = FX_MULTIPLY DFS_DIVIDE DADDR = 0x52 DI[4:0] = FX_DIVIDE DFS_RESET DADDR = 0x3F DI[15:0] = 0x0000 DFS_LOCKED (read) DADDR = 0x30 DI[0] = DFS_LOCKED PHASE_SHIFT DADDR = 0x55 DI[9:0] = PHASE_SHIFT CLKOUT_PHASE_SHIFT DADDR = 0x56 DI[15:0] 0x000D: DIRECT PHASE_SHIFT_KICK_OFF DADDR = 0x11 DI[15:0] = 0x0000 DFS_FREQUENCY_MODE DADDR = 0x41 DI[5] 0: LF (low frequency mode) 1: HF (high frequency mode) DLL_FREQUENCY_MODE DADDR = 0x58 DI[7:6] 00: LF (low frequency mode) 11: HF (high frequency mode) Знание этих регистров поможет вам в большинстве случаев переконфигурировать DCM после прошивки (проверено на практике). Но, к сожалению, для меня этого не достаточно, поэтому обращаюсь к гуру (возможно когда-то общавшихся со службой поддержки) с вопросом о пополнении вышеуказанного списка. В первую очередь интересуют следующие регистры: CLKDV_DIVIDE CLKIN_DIVIDE_BY_2 DCM_PERFORMANCE_MODE CLKOUT_PHASE_SHIFT (за исключением DIRECT) DUTY_CYCLE_CORRECTION FACTORY_JF Возможно есть еще интересные регистры, буду рад любой информации. Предложения по перебору не рассматриваются. -

вычисление SNR и SFDR

rloc ответил stdio тема в Математика и Физика

В общем случае, когда входной сигнал не синусоидальный (прямоугольный, треугольный и т.д.) нужно пропустить оцифрованный сигнал через согласованный фильтр (отделить шум от сигнала) и найти отношение одной мощности к другой. -

вычисление SNR и SFDR

rloc ответил stdio тема в Математика и Физика

1) В самом простом случае необходимо на вход АЦП подать синусоидальный сигнал с частотой F(SIN) = N*F(ADC)/4096, где N - некоторое целое число, 4096 - количество точек дискретного преобразования Фурье, которое Вы собираетесь делать. Тогда SNR считается по следующему алгоритму: а) делаете дискретное преобразование Фурье б) считаете отношение квадрата модуля одной спектральной составляющей (на частоте входного сигнала) к сумме квадратов модулей всех остальных составляющих в) берете десятичный логарифм от б) и умножаете на 10 2) В ином случае последовательность операций следующая: а) перемножаете оцифрованный сигнал на окно Наттолла или любое другое окно, дающее уровень боковых лепестков меньше уровня шума б) делаете дискретное преобразование Фурье в) считаете сумму квадратов модулей нескольких спектральных составляющих, находящихся в районе частоты входного сигнала и превышающих уровень шума г) считаете сумму квадратов модулей всех остальных составляющих д) делите в) на г), берете десятичный логарифм и умножаете на 10 -

Синтезаторы, особенно XST, очень часто врут. Смело делайте PAR и если опять максимальная частота окажется не достаточной, приводите копию "Static Timing Report", точнее того участка, который ограничивает быстродействие. Пока еще не встречал случая, когда DCM ограничивал бы быстродействие, конечно с учетом поправки на увеличение джиттера тактового сигнала.

-

АЦП 120 МГц

rloc ответил zvs тема в Вопросы аналоговой техники

Я писал "почти" и применительно для второй гармоники, конечно на выходе всегда ставят фильтр, причем у БМГ - опционально нн/-20/-30/-40дБ подавление гармоник. Для второй гармоники и опции "нн" (не нормируется) возможно фильтр не ставится. Да все правильно, причем часто вид нелинейного элемента (схемы) зависит от номера получаемой гармоники (четная/нечетная). -

АЦП 120 МГц

rloc ответил zvs тема в Вопросы аналоговой техники

Фирма Agilent, Genesys 2006.04 (ранее принадлежавшая Eagleware), сначала синтез классических вариантов, потом - комбинация и оптимизация, можно даже с учетом топологии ПП. :beer: -

АЦП 120 МГц

rloc ответил zvs тема в Вопросы аналоговой техники

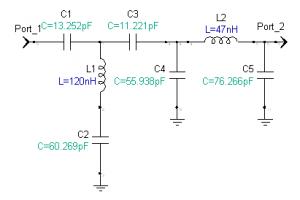

Вы заблуждаетесь, ничего легче чем удвоить нет, классический пример - двухполупериодный выпрямитель. После него почти фильтровать не надо, основная гармоника давится почти на 30дБ, ну и остальные тоже не очень высоки. Взгляните на генераторы ГК87-ТС фирмы Морион (не сочтите за рекламу, никакого отношения к ним я не имею), как Вы думаете каким образом получаются частоты 200, 300, 400 и т.д.? У автора похоже именно классический случай Ничего лучше по шумам умноженного кварцевого генератора еще не придумали, ну разве что генераторы на сапфировых диэлектрических резонаторах при низких температурах :crying: А генератор на ПАВе устроит скорей всего разработчика цифровой логики, но никак не СВЧ схемотехника или разработчика высокочастотных многоразрядных АЦП/ЦАП. В качестве презента дарю автору вопроса синтезированный фильтр, состоящий из комбинации эллиптического ФВЧ 3-его порядка с нулем на 60М и ФНЧ Чебышева 3-его порядка При расчете, добротности индуктивностей и конденсаторов брались 50 и 300 соответственно. Вход и выход - 50Ом. Подбор номиналов конденсаторов в ряду Е24 оставляю автору. Фильтр устойчив к 5-10% разбросу номиналов элементов. Если нет уверенности, то лучше попросить БМГ сделать генератор на 120М без умножения, пусть даже и с худшими шумами. -

АЦП 120 МГц

rloc ответил zvs тема в Вопросы аналоговой техники

Не путайте механические гармоники и умножение частоты (электрические гармоники). 24, 17.14 и более низкие частоты врятли используются, иначе шумы плохие получатся. По этой причине для генерации гиговых частот берут для умножения генераторы на частоты ~100МГц (5 или 7 механические гармоники, выходной сигнал - основная, первая электрическая гармоника). Совет, похоже, правильный. Только лучше порогом компаратора рулить. Для этого нужно добавить ОС по НЧ. В простейшем случае - примерно вот так: Скважность здесь не причем, и не надо изобретать хитроумных схем с обратной связью, еще шумы генератора убьете. :twak: -

АЦП 120 МГц

rloc ответил zvs тема в Вопросы аналоговой техники

Я согласен с kiss, редко когда кварцевые генераторы делают без умножения частоты на частоты более 100МГц, очень сильно увеличиваются шумы. Скорее всего внутри этого БМГ стоит генератор на 60МГц и умножитель на 2. Компаратор никаких субгармоник не уберет, ставьте до компаратора полосовой фильтр на 120МГц, чтобы подавить 60МГц, 60x3, 60x5 и т.д.. -

ADF4118

rloc ответил ivainc1789 тема в Вопросы аналоговой техники

Согласен с предыдущим автором, не понятно почему "до", скорее "от". На помехоустойчивость это никак не повлияет, если резисторы ставить рядом со входами ADF и можно брать достаточно большие значения, главное чтобы они не сильно заваливали фронты сигналов вместе со входной емкостью. На "защелочный" вход тоже желательно резистор повесить, иначе через сигнал управления и входные диоды будет подаваться питание на отключенную микросхему. -

Генератор синуса и косинуса

rloc ответил ikm тема в Вопросы аналоговой техники

Вы написали стабильность 1E-07, а для нее и обычные генераторы подойдут. Смотрите морионовские ГК136, +-5*10E-8 Вам хватит? К сожалению наших генераторов с высокой стабильностью и PECL выходом не нашел. Гармоники по-определению не могут быть ниже. Про узкополосный фильтр забудьте, а про PECL смотрите здесь http://en.wikipedia.org/wiki/Positive_Emitter_Coupled_Logic Эта цифровая логика имеет очень высокое быстродействие и как следствие очень низкие джиттер и фазовые шумы. В итоге схема должна выглядеть следующим образом ГК sin -> ФНЧ -> balun -> компаратор (ADCMP572/573) -> два PECL делителя на 2 (например MC100EP32D) ФНЧ, balun (BALance to UNbalance трансформатор) и компаратор - для того, чтобы из чистого синуса получить хороший меандр и соответственно в итоге разность фаз между sin и cos - 90 град, с высокой точностью. -

Генератор синуса и косинуса

rloc ответил ikm тема в Вопросы аналоговой техники

А как насчет того, чтобы взять генератор на вдвое большую частоту, поделить на PECL триггерах - один по фронту делит (sin), другой - по спаду(cos). Если не нравится большой уровень гармоник, можно поставить ФНЧ. Стабильность, джиттер, фазовые шумы и небольшая перестройка обеспечиваются кварцевым генератором (c PECL выходом). -

ADF4118

rloc ответил ivainc1789 тема в Вопросы аналоговой техники

А что мешает последовательно резисторы поставить >1К на CLOCK, DATA, да и на LE на каждую микросхему в отдельности? Если не ошибаюсь они все на вход работают. -

.bit файл

rloc ответил Putnik тема в Работаем с ПЛИС, области применения, выбор

О формате *.bit файла можно почитать тут: http://fpga-faq.com/FAQ_Pages/0026_Tell_me...t_bit_files.htm -

Spartan-IIe + XCFxxS

rloc ответил Vitёk тема в Работаем с ПЛИС, области применения, выбор

Не ломайте голову, ставьте простейшую микросхему в разрыв типа SN74CB3T3245 8-bit Bus Switch и заводите Done на OE этой микросхемы. У нас года 3 назад случилась неприятная история с Virtex. На стенде все программировалось, а как включали в изделие - не шьется. Оказалось, что на одну ногу ПЛИС из серии "dual-purpose", но не из группы ног для режима "master serial", до подачи питания приходил импульсный сигнал и сбивал процесс программирования. Ситуация немного другая, а решение проблемы - похожее. -

CIC для Virtex4

rloc ответил YuP тема в Среды разработки - обсуждаем САПРы

Если не затруднит, напишите пожалуйста, какие параметры CIC Вам были необходимы: 1) частота входных данных и их разрядность 2) коэффициент децимации/интерполяции (если есть) 3) занимаемый объем -

CIC для Virtex4

rloc ответил YuP тема в Среды разработки - обсуждаем САПРы

С вашим кристаллом, можно и без CIC обойтись. :) -

Ну как сами понимаете щупать можно только в железе. Мне можете верить на слово, опыт достаточный, начиная еще с Xilinx под DOS и уже не помню с каких кристалов. Скоро подготовлю материал для новой темы, добавлю оптимизма и уверенности разработчикам на ПЛИС, чтоб отпали всякие сомнения в запасе по быстродействию.

-

Тогда попробуйте пространственно подвигать память относительно ядра, не всегда P&R это выполняет хорошо. Посмотрите в FPGA редакторе на реальные длины c выхода памяти. Хотя конечно выигрыш будет максимум в 0.1-0.2 нс :(. Могу лишь успокоить тем, что реально всегда есть запас минимум 20-30%

-

Никогда не работал с PicoBlaze, но судя по Static Timing Report's, здесь явно не хватает регистра по выходу этой блочной памяти, все проблемы решатся с большим запасом!

-

Можно взять TigerSHARC TS201 600МГц: 1024 Point Complex FFT (Radix 2) 15.64 µs Я не специалист по сигнальным процессорам, но даже если непрерывно сжимать сигнал блоками по 1024 точки с перекрытием 50%, сигнальный процессор справится с этой задачей за 2*15,64+1,71=33мкс при располагаемом времени 51,2мкс. Ну а если последовательность отсчетов конечна и делать одну свертку, то выигрыш будет еще больше. По стоимости TS201 и Virtex4 нужной мощности будут сравнимы, правда что в сигнальнике памяти 24Мбит, а по времени разработки и отладки ПЛИС явно отстанет. Обычно под реальным временем понимается, что скорость поступления входных данных меньше скорости обработки, ну а задержка на N отсчетов во многих случаях вполне допустима. Интересно какой DDC используете? Случайно не GC5016 или свой на ПЛИС? Будем считать, что симметричный. Количество операций умножения при свертке во времени, как для симметричного FIR-а, сокращается вдвое. Значит все-таки локация :cheers: Ууу, здесь может потребоваться НЧМ Чип - SX35-11, у него ресурсов с избытком хватает на 16 каналов DDC + столько же фильтров сжатия, скорость отсчетов 1,25МГц, длительности от десятка до двух сотен мкс, динамики DSP48 тоже с избытком хватает, фильтр НИП (несинхронная имп. помеха) есть. Все это работает на 160Мгц, больше не рискнул бы, кулер не справится. Опытному разработчику для этого потребуется не менее 2 мес, начинающему думаю не менее 0,5 года. Никакими симуляторами уже не пользуюсь, отлаживаю сразу в реальной плате, быстрее получается.

-

Судя по тематике, я так понимаю, должна быть ПЛИС и другие варианты не рассматриваются? К сожалению условия задачи поставлены не полностью: 1) как правильно отметил RobFPGA, на сколько может быть задержан результат сжатия? 2) входной сигнал комплексный или действительный? 3) если комплексный, то симметричен ли сам ЛЧМ относительно нулевой частоты? 4) последовательность отсчетов конечна? 5) длина сигнала фиксирована? 6) разрядность входных данных? 7) какой динамический диапазон фильтра сжатия устраивает? По максимальной базе видно, что задачка не из легких. У нас все намного проще и решаем в лоб - свертка с копией во времени на Virtex4.