-

Постов

2 052 -

Зарегистрирован

-

Посещение

Весь контент Krys

-

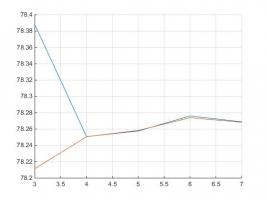

Здравствуйте. Модель шума квантования как равномерное распределение при входном гармоническом сигнале немного не совпадает со случайным сигналом, расхождение порядка 0,5 дБ. Почему? Другими словами: имеем входной сигнал. Имеем 2 способа квантования: просто округление через функцию round и второй способ - добавление равномерного шума с диапазоном плюс-минус половина младшего разряда (это способ не столько квантования, сколько моделирования квантования). Шум определяется как разность результирующего квантованного сигнала и исходного, до квантования. Затем рассчитывается ОСШ. Так вот, если входной сигнал является равномерным случайным распределением, то оба способа квантования дают одинаковый ОСШ, порядка 78 дБ для 13 битов. Это хорошо согласуется с теорией о 6 дБ на бит. Однако, если входной сигнал - комплексная экспонента, то для неё первый способ даёт ОСШ 79,5 дБ, а второй способ - на 0,5 дБ лучше. Хочу понять природу возникновения разницы. Привожу матлабовский код и картинку с результатом: %% numParam.bwChIn = 13; snrQ = []; snrR = []; % range for Ns order of power nSOrdRng = 3 : 7; fs = 1.25e6; % sample rate Ts = 1/fs; % sample period % frequency of input signal f_x = fs/16; T_x = 1/f_x; % % signalType = 'random'; signalType = 'harmonic'; for nSOrd = nSOrdRng Ns = 10^nSOrd; % adjusting Ns to be integer number of input signal periods fRatio = Ns * Ts / T_x; Ns = round(fRatio) * T_x / Ts; % create time scale t = 0 : Ts : (Ns-1)*Ts; % signal generation itself if strcmp(signalType, 'harmonic') x = exp(1i * 2 * pi * t * f_x).'; else x = complex(rand(Ns, 1), rand(Ns, 1)) * 2 - (1 + 1i); end quantNoiseIn = (complex(rand(size(x)), rand(size(x))) - (0.5 + 1i*0.5)) / 2^(numParam.bwChIn-1); xQ = x + quantNoiseIn; xQErr = xQ - x; xPwr = x' * x; xErrPwr = xQErr' * xQErr; snrQ = [snrQ 10*log10(xPwr/xErrPwr)]; xR = round(x*2^(numParam.bwChIn-1)) / 2^(numParam.bwChIn-1); xRErr = xR - x; xErrPwr = xRErr' * xRErr; snrR = [snrR 10*log10(xPwr/xErrPwr)]; end figure; hold on; grid on; plot(nSOrdRng, snrQ, nSOrdRng, snrR); hold off; На картинке красным - первый способ, синим - второй. На левой картинке сигнал - гармонический, на правой - рандомный. В исходнике можно переключить signalType для рандомного и гармонического сигнала. По оси Х отложены степени числа точек выборки сигнала, для которой производился расчёт. Т.е. 7 - это 1е7 точек. По оси Y - ОСШ в дБ. ЗЫ: маленько отредактировал сообщение. Добавил правую картинку для рандомного сигнала. Прошу заметить, что для рандомного и гармонического сигнала отличаются значения ОСШ, полученные даже путём округления round (первый способ): рандомный - 78 дБ, а гармонический - 79,5 дБ. Однако для рандомного сигнала оба способа дают одинаковый результат, а для гармонического - другой результат, да ещё и отличающийся между способами. Мне в первую очередь хочется докопаться, почему есть различие ОСШ между двумя способами для гармонического сигнала. А во вторую очередь - почему отличается ОСШ для способа округления через round для случайного и гармонического сигнала. И ещё: попробовал перейти на чисто вещественные числа. Поведение то же, числа те же.

-

С этим не может быть связано? http://electronix.ru/forum/index.php?showtopic=124651

-

Большое спасибо всем отозвавшимся!

-

А вообще в ЦОС не на ПЛИС сильны? Почему спрашиваю - потому что из дальнейшей дискуссии чувствуется, что Вам может пока и без ПЛИС бы хватило с ЦОС поразбираться. В том же Матлабе. Попробовать различные способы представления чисел, различные разрядности, понять, какие из них Вам сгодятся под конкретную задачу. Это всё с ПЛИС никак не связано и годится при реализации хоть на чём, хоть на процессоре DSP, хоть на обычной PC-шке. Ну а вообще в ПЛИС все операции умножения и сложения по умолчанию в фиксированной запятой с ограниченной разрядностью, поэтому все стараются к этому всё свести. А для плавающей - нужны дополнительные ухищрения. Не такие сложные, но отъедающие много ресурсов.

-

Выложите ещё пожалуйста те доки (или ссылки) по которым удалось разобраться, как это работает.

-

Не знаю, что за имплементатор Вы имеете в виду, но после операции синтез (выполняемой для Xilinx программой xst.exe) создаётся список цепей - тут Вы правы. Но упомянутые цепи соединяют, как раз, те аппаратные примитивы, которые существуют в ПЛИС, которая используется.

-

Вы беспросветный программист ))) (по складу ума)

-

А без циклов наверное в любом случае не получится, если число суммируемых сигналов заранее неизвестно и определяется параметром

-

Зато можно схему смешения, например, сигналов прерываний сделать в явном виде на логике, без монтажного "или".

-

да ещё и если объявление wor где-то далеко

-

Непонятен вопрос. Второй кусок не подлежит автоматической параметризации, поэтому при необходимости регулируемой размерности выбора особого нет... Хотя я бы сказал, что второй кусок нагляднее, не нужно забивать себе голову циклами.

-

В большинстве случаев по именам сигналов и без комментариев всё понятно, так что в случае явно прописанной логической функции лазить скорее всего никуда не придётся.

-

Не тайное. Но и не настолько очевидное, как прямая запись логической функции. Это я должен пробежаться по всему коду, чтобы найти, как же тут что образуется.

-

Golikov A., только одномерный, неуследил начальные условия. Но видимо для 2-мерного случая можно шину переформировать так (транспонировать), чтобы в цикле можно было использовать <=|bus, неуверен, надо подумать. Ну видимо да )) В железе проще и дешевле применить "монтажное ИЛИ", этим всё обосновано. Нагляднее ли это отдельной ЛА7 - вопрос. Но в текстовом описании явная логическая операция наверняка нагляднее "тайных знаний" о возможности "монтажного ИЛИ" у синтезатора )))

-

Golikov A., а в Вашем примере не проще ли так записать: bus = | module_bus; ?

-

Спасибо! Век живи, век учись... ) Но всё же это больше подходит как метод обфускации кода ))) Я бы лучше явным образом описал логику, было бы очевиднее потом анализировать если что.

-

я про инициализацию типа wire test1 = 1'b0. А затем где-нибудь ниже портмаппинг типа .testout(test1). Таким же макаром можно объявить и reg test2 = 1'b0, но затем использовать как комбинаторику через always @* test2 <=... А почему такая инициализация ваиров имеет право на жизнь? Просто как константа? Никогда почему-то не требовалось...

-

Есть ещё такой подводный камень, недавно столкнулись: объявляешь сигнал как reg, делаешь инициализацию, но используешь его как wire. А ещё оказывается можно вайр инициализировать (найдено в индусских исходниках). Синтезатор в ауте от такого, чопопало делает )))

-

Спасибо, тогда понятно, почему мы это не нашли ))) Чип планер не поддерживается в принципе для этого семейства. Как люди раньше без этого всего работали? )))

-

анализ варнингов в ISE

Krys ответил Sobol' тема в Среды разработки - обсуждаем САПРы

Полностью согласен, стараюсь их вычищать по-максимуму, чтобы не мозолили глаза, иначе в куче ворнингов глаз замыливается, и уже какой-то вновь возникший не увидишь. -

мультиедит - это лазить по всему исходнику и кликать мышкой с контролом в нужных местах - гимор, если исходник приличный. Автозамена всё же проще.

-

А обязаны принимать только всё, что по ГОСТ? А если примут VHDL, то в состоянии будут обязательно понять эту "не китайскую грамоту"?

-

Всё равно лишние телодвижения. К тому же перешли Вы только к началу блока описания сигналов, а там ещё всматриваться надо, где нужный вам сигнал. Я прогерский редактор не использую, сижу в notepad++. В любом случае бесполезное отвлечение (которого могло не быть вообще) может стоит вам ошибки из-за переключения внимания (хоть и наненадолго). Условно: я за 36 лет ни разу не болел водянкой. ЧЯДНТ? Это у Вас не аргументы, что вот ни разу, и всё тут. Я же пишу, что может попасться паттерн, что захватит лишние замены. И опять же лишние телодвижения, которых могло не быть вообще. Опять же отвлечение.

-

да, я тоже "сугубо местные" взялся объявлять рядом, поддерживаю предложение. Но, к сожалению, показанный мной пример вполне применим и для достаточно общих цепей, которые используются много где, поэтому и объявлять их лучше в шапке, а то потом объявление тем более замучаетесь искать. И именно с такими достаточно общими цепями и возникают потом проблемы.

-

анализ варнингов в ISE

Krys ответил Sobol' тема в Среды разработки - обсуждаем САПРы

Вобщем да. Но бывает, что по-другому никак. При том бывает, что ворнинги генерит коргеновская корка, так что их оттуда уже не вычистить. Для больших проектов скажем под последние виртексы этих ворнингов столько, что заблудишься. Мы даже сделали фильтр, чтобы искал только ворнинги о наших модулях и не трогал чужие. Фильтрация просто по пути модуля.