Alex77

-

Постов

721 -

Зарегистрирован

-

Посещение

-

Победитель дней

1

Сообщения, опубликованные Alex77

-

-

Беримор, кто это? Это *****, сэр. (с)

Из "чти меня" на 23.3 Intel Quartus Prime Design Suite.

Начинается симпотишно:

The components of the Intel Quartus Prime Design Suite support one or more of

the following operating systems:* Red Hat(*) Enterprise Linux(*) 8.6

* Red Hat Enterprise Linux 8.7

* Red Hat Enterprise Linux 9.0

* Red Hat Enterprise Linux 9.1

* SUSE(*) Linux Enterprise Server 12 SP5

* SUSE Linux Enterprise Server 15 SP3

* Ubuntu(*) 18.04 LTS

* Ubuntu 20.04 LTS

* Ubuntu 22.04 LTS

* Windows(*) 10 Version 1809 (build 17763) or later

* Windows 11 Version 22H2 (build 22621.1105) or later

* Windows Server 2019А вот продолжается:

Notes:

* Only 64-bit operating systems are supported.

* Intel Quartus Prime Pro Edition is supported on all listed operating

systems.

* Nios II EDS Pro Edition is supported only on the following operating

systems:

* SUSE Linux Enterprise Server 12 SP5

* Windows 10 (version 1607 or later)

Requires WSL1. WSL2 is not supported.

* Windows 11

Requires WSL1. WSL2 is not supported.

* Ashling(*) RiscFree(*) IDE for Intel FPGA is supported on all listed

operating systems.

* Questa - Intel FPGA Edition is supported only on the following operating

systems:

* Red Hat Enterprise Linux 8.6

* Red Hat Enterprise Linux 8.7

* Red Hat Enterprise Linux 9.0

* Red Hat Enterprise Linux 9.1

* SUSE Linux Enterprise Server 12 SP5

* SUSE Linux Enterprise Server 15 SP3

* Windows 10 Version 1809 (build 17763) or later

* Intel HLS Compiler Pro Edition is supported only on the following operating

systems:

* SUSE Linux Enterprise Server 12 SP5

* Windows 10 Version 1809 (build 17763) or later

* DSP Builder for Intel FPGAs Pro Edition is supported on all listed operating

systems.

DSP Builder also depends on MathWorks(*) MATLAB(*) operating system

support. Your version of MATLAB might support different operating systems

than those supported by the Intel Quartus Prime Design Suite and DSP

Builder. Check the MathWorks website for MATLAB operating systems

requirements:

https://www.mathworks.com/support/requirements/previous-releases.html

* Intel Quartus Prime Stand-Alone Programmer Pro Edition is supported on all

listed operating systems.

* Intel Advanced Link Analyzer is supported only on Windows operating

systems.Что то работает везде, а что то только в линуксе или только в виндах...

-

вот и я с аналогичным вопросом (в самом конце первого поста):

Ну и на десерт: можно ли (разумно ли) использовать BOOLEAN сигналы для построения "схемы" или у сигналов с типом BOOLEAN удел тестбенчей ?

-

Про функции:

В "IEEE Standard VHDL Language Reference Manual" IEEE Std 1076™-2008 мало что мне понятно. сложно написано.

Посему и интересуюсь почему "так" работает а "эдак" нет. пока лично мне не понятно.

Почему написано "вот так"

FUNCTION rising_bool (SIGNAL x : boolean) RETURN BOOLEAN IS

потому что написано/реализовано по аналогии с

function rising_edge (signal s : std_ulogic) return boolean;

из "стандартов библиотечных" std_logic_1164.vhdl

-

обычно это понимание начинает приходить со школьной лавки, а некоторым и вовсе не дано.

-

Это "проблема" конкретной реализации функции или это "общее свойство" самой идеи функции ? Что по вашему возвращается из функции ? И почему через промежуточное присвоение работает , а на прямую не работает ?

ПС: сегодня я "тёмный человек" ищу путь к свету знаний...

-

3 и 4. Почему не эвивалентно? Можно подробнее ? с моей точки зрения "от перемены мест слагаемых сумма не изменяется" В 3 явно указано промежуточное деяние, а 4 не явное. Всего то.

1 и 2 а здесь то что ? "гугл" весьма загадошные ответы предлагает и "не в тему".

А собственно что возвращает функция ? ведь как бы тип явно указан STD_LOGIC. Разве существуют "нечто" отличное от сигналов с таким типом ?

-

Опубликовано · Изменено пользователем Alex77 · Пожаловаться

Дано вивадо 2023.2

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.NUMERIC_STD.ALL; entity top is Port ( isReady : in boolean; iSig : in STD_LOGIC; oSig : out STD_LOGIC); end top; architecture Behavioral of top is signal fla : std_logic; function to_logic(x: in boolean) return std_logic is begin if x then return ('1'); else return ('0'); end if; end function to_logic; FUNCTION rising_bool (SIGNAL x : boolean) RETURN BOOLEAN IS BEGIN RETURN ((x'event AND x = true ) AND x'LAST_VALUE = false); END; begin process (isReady) begin --fla <= to_logic(isReady); -- 4 вариант --if rising_edge(fla) then -- 4 вариант --if rising_edge(to_logic(isReady)) then -- 3 вариант if rising_bool(isReady) then -- 1 вариант --if (isReady'event AND isReady = true ) AND isReady'LAST_VALUE = false then -- 2 вариант oSig <= iSig; end if; end process; end Behavioral;

1) линтер и elaborated отваливаются

- [Synth 8-26] attribute 'event not implemented ["C:/project_2/project_2.srcs/sources_1/new/top.vhd":26]

синтез и имплемент НЕ проходят.

2) если

if rising_bool(isReady) then

заменит на

if (isReady'event AND isReady = true ) AND isReady'LAST_VALUE = false thenлинтер и elaborated и синтез и имплемент проходят. Тут вопросов особо нет.

3) если применить

if rising_edge(to_logic(isReady)) then

то уже на уровне редактора сразу подчёркивает красным и говорит что

error: signal formal 's' cannot be associated with type conversion of function call at actual

синтез и имплемент НЕ проходят. Вопрос ЭТО глюк ?

4) если применить

fla <= to_logic(isReady);

if rising_edge(fla) thenвообще никаких проблем

Вопрос:

Почему первый не работает, а второй работает ? Аналогично 3 не работает а 4 работает?

Вроде всё эквивалентно, но результат "почему так" мне не понятно.

Докучи: это поведение соответствует стандарту языка или это причуды вивадо ?

ПС: альтера 22 в общем случае как минимум проглатывает 3 вариант

пспс: в свойствах указал что VHDL2019. но это не влияет на результат. Надеюсь я нигде не ошибся в описании "проблемы"...

Ну и на десерт: можно ли (разумно ли) использовать BOOLEAN сигналы для построения "схемы" или у сигналов с типом BOOLEAN удел тестбенчей ?

-

мои познания в HTML закончились на Microsoft FrontPage 1.1

-

-

Опубликовано · Изменено пользователем Alex77 · Пожаловаться

"весит вдвое больше" относительно кого ? 2023.2 даже меньше чем 2023.1. (на размер значительно влияет данные по микросхемам с ИИ)

по vscode - можно не использовать, классический eclipse на месте (пока).

Для переноса проектов - есть методичка там прописаны нюансы (опять же не пробовал).

-

наверно затем чтоб было не возможно проверить контрольную сумму. пс: а что это за исо-образ диска на 107 гб ??? такие диски бывают ?

-

Опубликовано · Изменено пользователем Alex77 · Пожаловаться

не сочтите за грубость... но на исторической родине

-

-

104 GByte

Devices that are production-ready:

- Versal HBM: XCVH1742 and XCVH1782

- Versal Premium: XQVP1502, XQVP1202 and XQVP1402

Meeting Fmax targets

- Increase performance of designs in Versal Premium and Versal HBM devices with automatic place & route of SLR crossings

- Faster device image generation with multi-threaded support

Ease of use enhancements in IPI, DFX, Debug and Simulation

- New GUI window added for address path visualization from source and sink for Versal devices in IPI

- Manually Assigned Address Locking Capability in BDs (IPI)

- Improved visualization for DFX floorplans in Versal devices

- Added support for Tandem+DFX in the same design for Versal Monolithic devices

- Expanded support for Tandem Configuration for Queue DMA IP in UltraScale+ devices

- Vivado Simulator VCD support for SystemC users

-

Вроде достаточно Lite (free) версию - но не все виды плис доступно и не все тулзы.

-

Nios® V processor is the next generation of soft processor for Intel® FPGAs based on the open-source RISC-V Instruction Set Architecture. This processor is available in the Intel® Quartus® Prime Pro Edition Software starting with version 21.3.

-

есть симпотяга

Intel Corporation 1 06/09/2023 PDN2312

Revision 1.0.0

PDN Issue Date: 06/09/2023

PRODUCT DISCONTINUANCE NOTIFICATION

PDN2312

Description

Intel is discontinuing the following IP ordering codes.

Reason for Change

The selected Nios® II IP ordering codes are being discontinued due to product transition

to Nios® V.

Recommendation

Intel recommends that customers migrate to the Nios® V Processor, which is based on

the RISC-V architecture, enables access to a growing ecosystem, removes the need for

Windows Subsystem for Linux, and offers a dedicated development environment with

Ashling RiscFree IDE for Intel FPGAs software. For more information, refer to the Nios® V

Processor - Intel® FPGA web page.Правильно ли я понимаю что:

1) Nios II - накрылся медным тазом

2) в замен ему предлагают Nios V

3) wsl при таком раскладе не требуется.

-

На кой ляд такой изврат ? Quartus умеет работать в виндах напрямую.

-

В 19.09.2023 в 14:41, Yojan сказал:

При входе на сайт говорит Export compliance failed...

Попробую с рутрекера качнуть.

Если вы про "Мою лицензию Xilinx-AMD обнулили" - ну дык не надо путать пиво и сосиски.

Как уже сказали - перекрыли доступ к сайту, а лицензия она "у вас на руках" и её ну ни как невозможно обнулить физически.

Засим всё.

-

это как так "обнулили" ? Она же почти вечная...

-

Опубликовано · Изменено пользователем Alex77 · Пожаловаться

Примерно так должно выглядеть лицензия для RDP

INCREMENT tri_mode_eth_mac xilinxd 2999.99 permanent uncounted \

C5AA77541DA8 VENDOR_STRING=License_Type:Source HOSTID=ANY TS_OKпс: до кучи незабываем про "правильную" настройку сервера лицензий (на сайте xilinx было...)

-

1) в приведённых картинках не от слова совсем лицензии на tri_mode_*_*

2)TS_OK указано только для среды разработки, но не для корок.

пс: может гдето путаю, но мысль направление вот такое...

-

Опубликовано · Изменено пользователем Alex77 · Пожаловаться

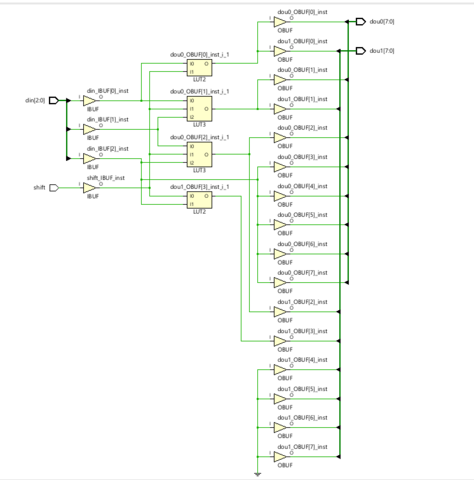

2018.3 / 2019.2 -хрень

2020.2 / 2021.2.1 / 2022.2 / 2023.1 - ОК

module buss (

input wire shift,

input wire [2:0] din,

output logic [7:0] dou0,

output logic [7:0] dou1

);always_comb

begin

dou0 <= signed'(din)<<<shift ; // в страших битах dou0 получается расширенный знак из din[2]

dou1 <= din <<<shift ; // в страших битах dou1 нули

end

endmodule -

ммм... темой не ошиблись ?

может это сюда ?

Часы AHDL

в Решение задач

Опубликовано · Пожаловаться

До зачётной недели ещё далеко, можно успеть прочитать методичку...