Alex77

-

Постов

721 -

Зарегистрирован

-

Посещение

-

Победитель дней

1

Сообщения, опубликованные Alex77

-

-

Опубликовано · Изменено пользователем Alex77 · Пожаловаться

-

Опубликовано · Изменено пользователем Alex77 · Пожаловаться

1) "jtag-usb" + "комп с установленный софт Hardware Server" -> сетка -> "комп с установленный софт полноценный Vivado"

2) jtag-eth -> сетка -> "комп с установленный софт полноценный Vivado"

во 2) до кучи требуется желательно "хаб с dhcp"

ПС: "Vivado Hardware Server" гарантировано есть в полном комплекте "Vivado". Наверно возможно достаточно установить "Vivado Lab Solutions" (он тоже входит в "Vivado")

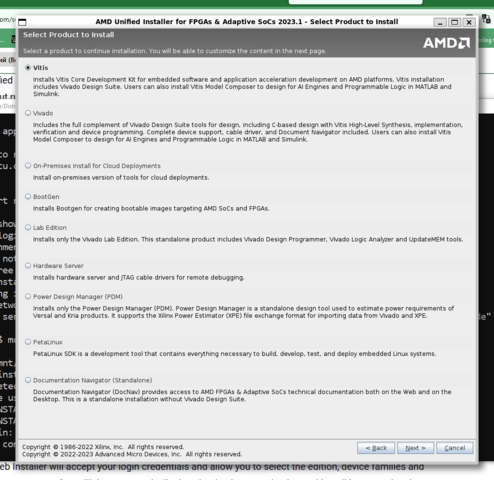

пспс: нынче инсталяшка одна на все случаю жизни...

примерно "запускается через hw_server.bat" (наверно нужны нужные опции).

-

Собственно тема.

-

Vivado ML Edition:

- Average QoR improvement of 8% for Versal™ Adaptive SoCs and 13% for UltraScale+ FPGAs using Intelligent Design Runs.

- Extending multithreading support for bitstream generation for Versal devices.

- Enhancements in Report QoR Assessment(RQA).

- Power Design Manager(PDM) now a part of Unified Installer - Seperate from Vivado tool.

- Added support for Versal HBM devices in PDM.

-

Vitis Unified Software Platform:

- Enhancements for Vitis library functions targeting Versal AIE designs.

-

New features added to assist with Versal™ AIE designs:

- AIE compiler enhancements.

- AIE simulator enhancements.

- AIE reset/reload methodology.

- Support for Vitis™ environment export to the Vivado™ environment.

- Vitis tool features for profile, debug & trace – primarily for the Versal AIE device family.

- Other features – Vitis analyzer GUI update & Vitis platforms.

-

Embedded Software:

-

Updated Software Stack Components & versions.

- Linux kernel v6.1 , U-Boot mainline v2023.01 , PetaLinux updated to new yocto version v4.1 (Langdale) , TF-A v2.8 , Xen Hypervisor v4.17, Yocto Project v4.1 (Langdale) , OpenAMP v1.3.1, Gstreamer v1.20.5 , V4L2 & DRM framework v6.1 , QEMU v7.1.0, FreeRTOS v10.5.1.

-

Device Tree Generator (DTG).

- Enabled sugar syntax for overlays & Custom DTSI flow for DFX/CSOC.

-

AI Engine support.

- Enabled AI Engine support for VEK280 & V70 Devices along with sysfs debugging features in Linux for all devices.

-

VCU features.

- Enabled support for Decoding Intra Only Frames.

-

Updated Software Stack Components & versions.

-

Vivado ML Edition:

-

Опубликовано · Изменено пользователем Alex77 · Пожаловаться

версаль и париж мне не особо актуален

пс осталось 6 часов качать

-

ну да. долго и нудно качать...

а что это за зверь "The Classic SoC Boot flow has been moved to limited access to ensur" ???

-

Вы меня удивлять....

В окне (Package Pins) есть куча столбцов , там можно выбрать сортировку ( клыцая по заголовку), а ещё там есть столбец "Clock" а там значения MRCC и SRCC ....(главная тактовая и вторичная). Столбец "port" выбираем цепь. ДЛя удобства разгруппировать выводы по банкам (4 кнопка слева начина с лупппы).

-

В 29.04.2023 в 08:00, andrew_b сказал:

Вы тему читаете или только сюда пишете? У блочной памяти нет сброса, тем более асихронного.

Ежу понятно... 😉

но если "сброс" сделать синхронным, то это превращается в запись "0" по выбранному адресу.

-

xilinx смог осилить только так (без асинхронного сброса) в блочную память

always @ (posedge clock)

-

опции "синтезатора"? или атрибуты для модуля ?

-

а сколько всего "такой" памяти в проекте ? и фактические параметры одного экземпляра памяти?

-

В "один момент времени" адрес для чтения не совпадает с адресом по записи (по значению). Запись по текущему адресу, а чтение по предыдущему.

-

1

1

-

-

Сиё однозначно двухпортовое ОЗУ получается. Смотрите Eleborated RTL - там в картинках нарисовано.

-

Спросим по другому : Какие UG были прочитаны (или хотя бы просмотрены) на тему загрузки?

-

На всё воля ТС.

Просто на сколь видно из картинок - была попытка установки VirtualBOX (или чегото похожего) с "урезанной" ISE. Так почему "сразу" не поставить виртуалку+ise (в нужной комбинации).

ПС: и не забываем что VirtualBOX и Hyper-V не совместимы патологически.

-

win 10 x86 тоже норм.

-

Опубликовано · Изменено пользователем Alex77 · Пожаловаться

Что то я зануден...

Посмотрел парочку докладов (в начале )

qemu+cocotb/mathwork+simulink

1) нет тезисов о "достоинствах" данного "метода" по сравнению с другими.

2) не раскрыта тема "почему выбран именно это способ", при наличии "штатных" (и простых в использовании).

3) и что именно тестировалось в qemu+cocotb ? Толи линукс с дровами в qemu толи ip корка....

4) чем плох qemu от xilinx если он работает и выполняет свой функционал ?

5) итд итп

Выглядит как "движуха ради движухи"...или я может слышу, но не слушаю?

-

применительно к zynq --- FSBL загружает и запускает программу пользователя и прошивку плисы докучи. По идее это всё прописано в документации...

-

а что по пункту 1 ?

-

1) данный " .xdc файле" не используется при "сборке" проект.

2) "соседние" выводы в этой же "банке" в каком стандарте ?

-

- Петька приборы...

- 33

и далее по тексту.

Аналоги кого/чего/в чём/для чего итд ? Как замеряли потребление DSP48 ?

-

я совсем не в теме - однако "какая связь между Нейронные сети и машинное обучение и вычислением синусов косинусов ?"

-

ничто не запрещает "В каждом проекте создаю отдельную папку с ядрами и правлю их под конкретный проект." и заливать туда конкретную версию корки.

-

вполне достаточно предложенного...

-

Опубликовано · Изменено пользователем Alex77 · Пожаловаться

а с какого перепугу должно быть больше (быстрее) ?

Vivado Hardware Server - где взять и как с ним работать?

в Среды разработки - обсуждаем САПРы

Опубликовано · Изменено пользователем Alex77 · Пожаловаться

Ну да есть отдельно..

Однако зачем нужны гвозди без микроскопа ?

Всё равно придётся качать "полную виваду".

А там есть понятие "установить только Hardware Server" . Только что посмотрел в 2023.1 (предыдущие примерно также - не обращал внимание)