sergun53

Свой-

Постов

70 -

Зарегистрирован

-

Посещение

Весь контент sergun53

-

Работать то можно, если бы не swap.

-

Спасибо за подсказку. Проделал, получил FA и BA Report Никаких изменений между платой и схемой нет. Чего же он просит? Ну хоть теперь спокоен, что с головой все в порядке.

-

Dxd-Exp 7.9 Работал с pcb, схему в DxD не открывал давно, следовательно не редактировал. А тут в Expedition заметил желтый фонарик, сигнализирующий о необходимости Forward Annotation, но схему то я не менял. Собственно вопрос, как сравнить нетлист схемы и платы? Опять же в PCAD было просто, Utils>Compare Netlist и получай все разногласия между схемой и платой. А как здесь? Провести Forward Annotation, а потом смотреть, что изменилось в текстовом отчете по Forward Annotation не хочется, потому как не понятно нужно ли вообще вносить изменения ( схему то не правил). Как не делая Forward Annotation или Back Annotation выявить различия между схемой и платой?

-

Первый вариант работает, только необходимо сразу фиксировать скопированные via и трассы, иначе при любой попытке подвинуть vias на другое место они чудесным образом пропадают А вот здесь хотелось бы поподробней: как в одном cell может быть несколько пинов с одинаковым номером, в PCAD это не возможно, а в Expedition?

-

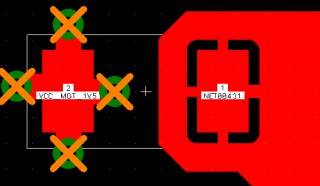

1. Это не очень принципиально, хотя может и не эстетично, на разбежка в пэдах <0.1мм, что для механического разъема не играет никакой роли. 2,3. via в Cell определяют их жесткую привязку и уменьшают возьожности трассировки, особенно при плотной разводке следовательно их придется двигать, удалять и т.п. 4. Согласен, руки не дошли. Принцип понял, спасибо.

-

ASP_1296XX.7z Принимаю разумную критику по поводу библиотечного компонента, может чего лишнее или чего-то важного не хватает. Вставлять via в графику не предлагать.

-

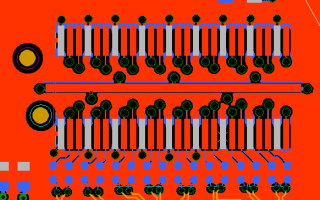

В разъемах располагающихся строго друг под другом к длинным планарным пэдам подводится питание, поэтому их надо "сшить" между собой посредством via. С грехом пополам получилось сделать то, что хотел. Проблема была в том, что провести трассу от pad к via не получалось, можно было провести только одну трассу,остальные удалялись или via не подключалось к трассе (Plow failed). А вот если соединять наооборот,от via к pad то все стало получаться, но пока дошел до этого слегка помучился. По поводу своих мучений записал кино, но кинщик из меня еще тот, не судите строго. One_pad_many__via.7z Спасибо всем откликнувшимся.

-

Согласен с Вами, для этого случая Prevent Loops работает, но если мы имеем длинный pad ( например ножевое питание в разъеме PCI_E) который ружно прошить via ничего хорошего не получается А вводить трассы в режиме рисования как-то нелогично

-

ЕЕ 7.9 Каким образом можно к одному pad подключить несколько via для подключения к внутреннему полигону, примерно так ,как на картинке Фиксация via,трасс и отключение DRC ничего не дает, можно подключить только одну трассу. Городить вокруг pad полигон совсем не хочется, да и не всегда возможно.

-

Трассировка LVDS во внутр слоях

sergun53 ответил Digi тема в Работаем с трассировкой

С таким стэком, который выбран получить 100 Ом для диффпар нельзя максимум 88 Ом и то уже при неприличных зазорах между проводниками. Либо соглашайтесь на то что есть по сопротивлению, либо меняйте стэк. -

Stackup Editor

sergun53 ответил dysan тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

Такую проницаемость имеет в частности высокочастотный стеклотекстолит марки FR-4 High Tg, именуемый как FR408. -

Проблема со слоем board в P-CAD 2006

sergun53 ответил SBB тема в P-CAD 200x howto

В PCAD 2006 автоматически образуется BoardOutlineObj, практически повторяющий контур платы нарисованный линиями в слое Board. Для выделения этого контура небходимо поставить галки на Board Outline для группового или единичного выделения (Options>Selection Mask>Block Selection, Options>Selection Mask>Single Selection) после чего этот контур можно будет удалить. -

Да не надо шину переименовывать. После того как внесены изменения в содержание цепей шины выделяете ее правой кнопкой и в выпадающем меню выбираете Update Bus Signals Должен быть двойной щелчок при нажатой клавише Ctrl, внимательней читайте описание.

-

Про стрелочки я знаю,но получается, что ICT сортирует по идентификационному номеру Id имеющий формат $_номер листа схемы_сам идентификационный номер. Поскольку этот номер присваивается DxD по умолчанию (видимо в зависимости от порядка ввода компонентов) получается что RefDes в ICT сортируются не по порядку R1,R2,R3 а по мере установки в схему, а при копировании однотипных кусков вообще неизвестно как. Кроме того, в схеме имеющей много листов, RefDes формируются в пачки, так как номер листа присутствует в Id. У меня пока получается только вот так Есть ли способ осуществить сквозную сортировку в ICT именно по позиционному обозначению (Ref Designator)? В навигаторе такая сортивка есть, но в пределах только одного листа. Да, это,то что нужно, только я не нашел в Settings>Interconnectivity Table как это можно реализовать. И еще лучше, если бы название пина вообще не отображалось, а был только пин намбер.

-

Sorry, не придал этому значения, видно сработал стереотип: раз есть onsheet и offsheet коннекторы, значит они нужны, чтобы сшивать сигналы на разных листах. То, что это не так только радует. Только зачем они тогда нужны в DxD (про DC\DV просветили), так как через иерархию они не работают, а в одноуровневой схеме не нужны? В схеме у меня были нормальные значения Ref Designator, а в ICT Viewer те же Ref Designator (те которым упаковщик сам присвоил Instance Value) отображались с ?, это-то и смутило. Проделал упаковку еще раз и в схеме и в ICT Viewer все компоненты отобразились одинаково, без знака ? в обозначении. Разница, лишь в том, что в первом случае, я упаковав схему и убедившись, что упаковка прошла нормально вышел из pcb без сохранения, а во втором сохранил pcb. Эта двойственность немного напрягает: допустим в Property на компонент написано Symbol Value R? Block Value R? Instance Value R15 до сих пор не понятно, что-же реально отображается на схеме и в ICT Viewer - Ref Designator или Instance Value? И еще несколько вопросов -Можно ли в ICT Viewer сортировать компоненты по Ref Designator? А то они сортируюся по какому-то непонятному признаку. -Можно ли в ICT Viewer отображать в таблице соединений не названия пинов, а их номера? А то в большой ПЛИС названия мало, что говорят (I/O, VCC да GND, причем из-за уникальности имени к ним добавляется куча цифр I/O1,I/O2 и т.д.). Гораздо привычнее иметь таблицу соединений с цоколевкой микросхем.

-

1. Во всех тренингах по DxD говорится, что соединенными считаются одноименные цепи только на одном листе схемы, а чтобы соединить ту же цепь на другом листе нужно использовать sheet connector или порты. Я же с удивлением обнаружил, что одноименные цепи соединяются на разных листах схемы без всяких конекторов и портов так, как-будто они глобальные цепи. Получается, что schematic считается одним листом, независимо от того сколько в нее вложено sheet ? 2. Нарисовал схему, расставил RefDes как мне было необходимо,упаковал,все нормально. Потом вернулся ICT Viewer и увидел, что часть компонентов не имеют значений рефдеса,а так и остались не определенными (R?,C? и т.д),видимо я их пропустил при именовании вручную и упаковщик присвоил им свои значения,которые отбражались на схеме,но не отбражаются в ICT Viewer. Оказалось, что упаковщик присвоил им значения Instance Value, а не Ref Designftor. Кто-нибудь может обяснить для чего такая путаница ? И как в ICT Viewer увидеть нормальные Ref Designftor после работы упаковщика? Версия DxD 2007.7

-

Посмотрите там же мовики PCAD_PADS9_EXP и PCAD_LIB_TO_EXP_LIB и все станет понятно. Ну и поиск по форуму никто не отменял.

-

Импорт платы из PCAD в Expedition осуществляется по пути PCAD>PADS>Expedition через встроенный транслятор PADS (он там с версии 9.0) или отдельный транслятор той-же 9, который выложен на Мегратек.

-

Расчет импендансов

sergun53 ответил GoodDron тема в Altium Designer, DXP, Protel

Хороший калькулятор Polar Si9000 -

Самые новые трансляторы уже встроены в PADS9.2 и EE7.9

-

А вот у меня все как раз наоборот. С версией 10.1 можно было работать только при установленной английской локали, а с установкой 10.2 все чудесным образом исправилось и прекрасно работает теперь при русском без переключения локальных установок языка. Правда у меня не 7, а XP SP3 RUS.

-

А некоторые производители еще и фрезеруют по контуру, так, что и отламывать ничего не надо.

-

BGA. Переходное или конденсатор?

sergun53 ответил Джин тема в Работаем с трассировкой

В приведенном выше фрагменте платы параметры переходного отверстия 0.5х0.25, шаг естественно 1 мм. Зазор между площадкой 0402 и пятаком переходного отверстия, где-то 0.23 мм. Площадка 0402 0.5 на 0.5 с радиусом скругления 1.25. Это немного не соответствует требованиям IPC-7351, где площадка для 0402 должна быть в среднем 0.6х0.6, но еще раз повторяю, что никаких проблем с пайкой, как вручную, так и в печи не возникало ни у одного из производителей. Также, как и с надежностью.