-

Постов

1 215 -

Зарегистрирован

-

Посещение

-

В разных процессорах по разному.

-

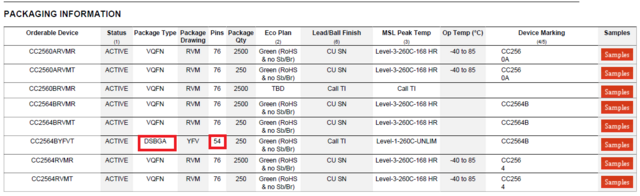

CC2564 BGA-54, что с даташитом?

skripach ответил skripach тема в В помощь начинающему

С покупкой нет проблем, а даташит на BGA дают под NDA. Хотя нужен только пинаут -

CC2564 BGA-54, что с даташитом?

skripach ответил skripach тема в В помощь начинающему

-

CC2564 BGA-54, что с даташитом?

skripach опубликовал тема в В помощь начинающему

https://www.digikey.com/en/products/detail/texas-instruments/CC2564BYFVR/5005114 Чип продается, но в даташите нет распиновки, где? ..или это со мной что-то не так? -

В китайских ширпотребных флешках тоже повсеместно пады замазаны шелкограшией. Помоему они таким образом паяльную пасту экономят.

-

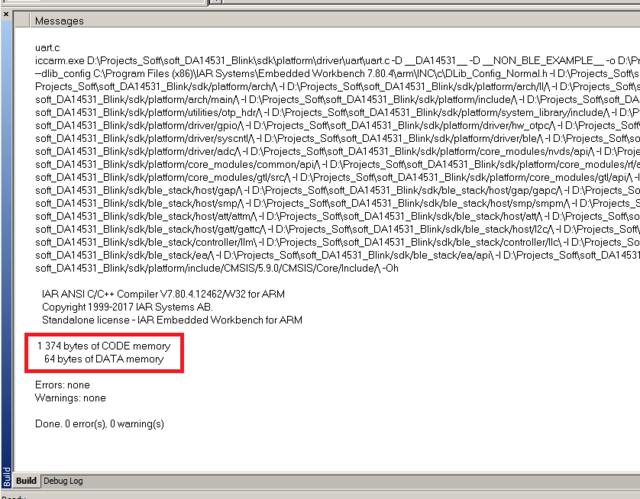

В яре есть 3 кнопки: - Compile - компилирует отдельный файл, аналогично вот этой кнопку в Кайле - Make - Собирает, линкует весь проект, без перекомпиляции уже скомпилированного ранее, аналогично вот этой кнопку в Кайле - Rebuild all - полностью пересобирает весь проект, аналогично вот этой кнопку в Кайле Вот так, после нажатия на Compile. Скомпилился только uart.c Тонкостей работы не знаю, возмоэно оно отслеживает зависимости и "в зачёт" идет только то что реально используется, проверяется синтаксис всего модуля. Но итоговый размер равен сумме по отдельным модулям. Родные примеры собраны под Keil, я собрал проект в IAR (ну ближе он мне и родней ), примеры работают на железке и под Keil и под Iar, но размер выходного кода значительно отличается, хотел понять где именно.

-

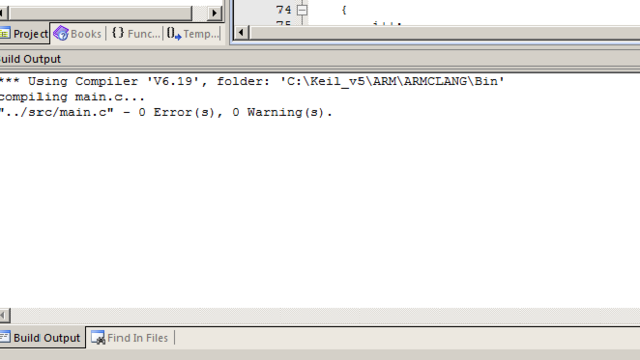

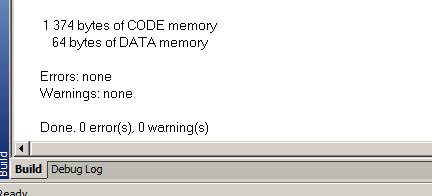

Это у вас похоже весь проект скомпилился и слинковался, такое у меня работает, но это показывает размер всего проекта. Я же хочу компилить один модуль (файл) и видеть сколько и какой памяти этому модулю требуется. Откройте любой *.с файл, нажмите Ctrl + F7. У меня 5.38, токое выдаёт:

-

Где настроить чтобы отбражался размер занимаемых ROM RAM после компиляции отдельного модуля а не только всего проекта?

-

Ещё https://www.silabs.com/documents/public/software/RF-Range-Calculator.zip

-

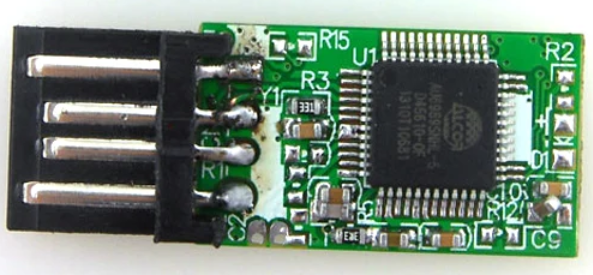

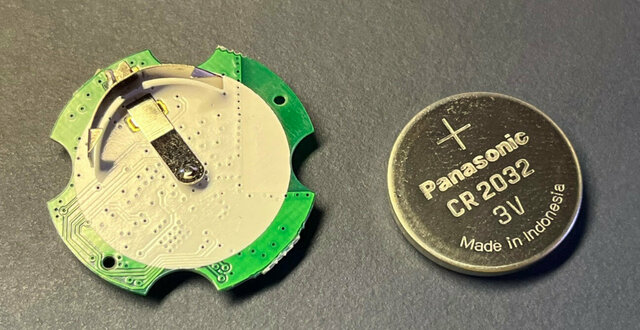

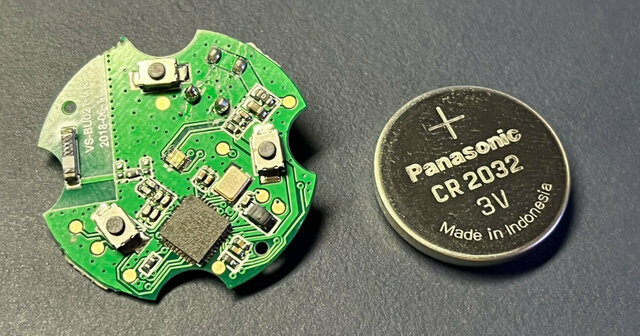

Есть вот такой пультик ДУ для экшн камеры. Внутри вот такая плата с Airoha ab1601, даташит не нашел, но есть какие-то сорцы на гитхабе https://github.com/ouzuming/ab1601_controller но без схемы и полного даташита включая РФ часть проку от этого мало. Цель управлять этим пультиком каким-то своим устройством. Я думаю проще сделать свою начинку для пультика чем разбираться с имеющейся(хотя это было бы здорово). Вопрос на чем проще, быстрее сделать? Хочется сделать быстно и без заморочек, цена не важна, 50м в здании чтобы стойко работало. Что там ставят в брелки для машин кто в теме?

-

Подсветка LCD - опознать компонент

skripach ответил mitya1698 тема в В помощь начинающему

Лучше отдайте в сервис. -

Гуглить "ini parser".

-

China-Link, Вариант отладчика из Китая

skripach ответил krestnick тема в Отладочные платы

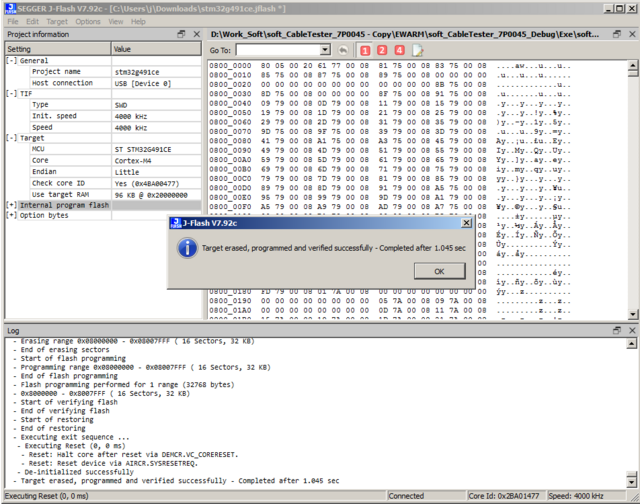

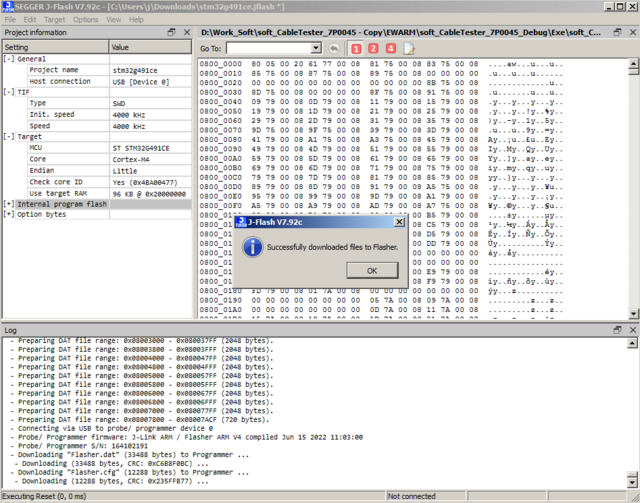

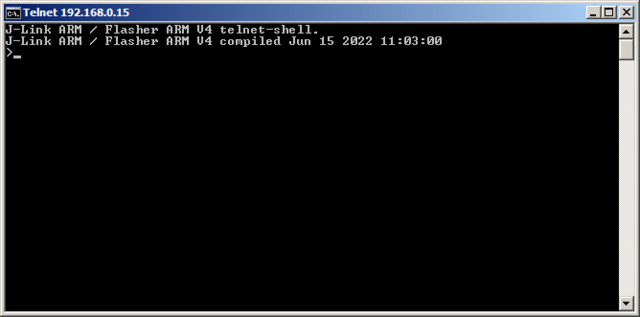

Production Programming прошивает таргет как положено, всё работает: Download config & data to Flasher: При нажатии на кнопку загорается красная лампочка и дальше горит вместе с зелёной пока не переподключишь флешер к USB. Пробовал питать таргер и от флешера и от отдельного источника. Как включить лог? В телнете тишина, хотя к флешеру есть подключение: Собственно делаю как в этом видео,но не работает 😞 И ещё.. при нажатии на кнопку видно что выполнение ранее прошитой программы прерывается (перестает мигать светодиод), но более ничего не происходит, после reset работает старая прошивка дальше. Такое поведение на обоих флешерах. -

China-Link, Вариант отладчика из Китая

skripach ответил krestnick тема в Отладочные платы

У меня есть два Флешера вот таких, через оба можно прекрасно отлаживать и прошивать с компьютера, но хотелось бы с кнопочки. Я пытаюсь использовать J-Flash, я так понял J-Flash это для процессоров, а U-Flash это для памяти и простельньких микроконтроллеров с архитектурой отличной от ARM Cortex. В U-Flash нет девайсов STM32

.thumb.jpeg.395e46aa98f3229892a912569bd2e08b.jpeg)