Поиск

Показаны результаты для тегов 'ddr'.

-

DDR2 память - что значат "банки"?

1891ВМ12Я опубликовал тема в Работаем с ПЛИС, области применения, выбор

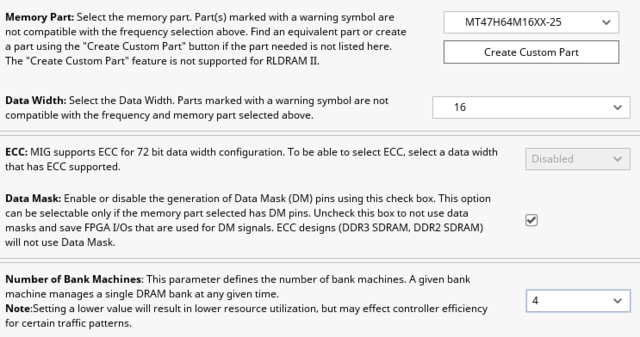

Пытаюсь приклеить DDR2 к Cyclone 4. Память выбрана "MT47H64M16 – 8 Meg x 16 x 8 banks". Ключевое 8 banks. Создал кастомный компонент, указал ему 8 банков, а контроллер говорит "не могу 8, только 2 или 4". Решил проверить, а что скажет контроллер DDR2 например в Xilinx Artix 7. Он позволяет выбрать в точности MT47H64M16, но внизу есть указание что 4 банка можно выбрать, но будет чуть медленнее. Но это не просто банки, а bank machines, это что то возможно иное. Вопрос: если Cyclone 4 контроллер памяти может только 4 банка для DDR2, то значит ли это что память с 8 банками я использовать не могу? А может могу, с некоторыми потерями, например половина емкости, половина скорости, но работать будет? Или шансов нет? Мне казалось любую DDR2 почти можно применить на некоей максимальной частоте для данного контроллера памяти, уж 16 бит шину оно может. А тут вылезли банки... -

Компания Бифорком Тек находится в поисках тополога в свою команду RnD. Пару слов о нас. Мы существуем с 2015 года, занимаемся разработкой и производством продуктовой линейки высокотехнологичных устройств с использованием технологий SDN/IoT/4G/5G/6LoWPAN и решений в области передачи данных. Находимся в в Особой экономической зоне «Технополис «Москва» рядом с метро Текстильщики. Ссылка на наш сайт - https://b4com.tech. Если вас заинтересовала вакансия, пишите или звоните по номеру 89152033710 (Екатерина). Также можно откликнуться на вакансию в hh - https://hh.ru/vacancy/72745516. Инженер-тополог: Обязанности: Разработка ПП в Altium Designer. Формировать и оптимизировать стек МПП (стоимость — производительность) Трассировка сложных многослойных печатных плат; Подготовка GERBER (CAM) файлов для производства печатной платы; Подготовка файлов для расстановщиков (placement) и сборочных чертежей (Assembly); Взаимодействие с разработчиками и конструкторами; Участие в разработке конструкторской документации. Будет плюсом: Моделирование целостности сигналов (SI); Моделирование распределения емкостей и полигонов питания (Power); Тепловое моделирование платы; Знание цифровой, аналоговой, СВЧ схемотехники Разработка топологии сложных печатных плат, желательно с использованием «глухих» и «слепых» переходных отверстий; Требования: Опыт проектирования многослойных печатных плат для цифровых высокоскоростных устройств; Английский достаточный для чтения технической документации; Опыт работы в радиоэлектронной промышленности; Опыт трассировки печатных плат с цифровыми интерфейсами типа PCIe Gen3, DDR3/4; Понимание проблем перекрестных помех, целостности сигнала, электромагнитной совместимости; Опыт проектирования печатных плат с высокой плотностью компоновки, в том числе с применением BGA-компонентов с мелким шагом выводов; Опыт: Трассировка с выравниванием длины линий, расчетом импеданса, моделированием целостности сигнала, использованием теплоотводящих слоев; Приветствуется опыт работы с аппаратными платформами на процессорах архитектур ARM, MIPS и с высокоскоростными интерфейсами Ethernet (до 10GB, SFP), DDR3 и выше, PCIe, SATA, HDMI. Разработка посадочных мест в соответствии с IPC с учетом требований автоматической сборки ПП; Подготовка выходных файлов для производства. Согласование стеков, материалов, выбор технологии используемых в печатных платах. Условия: График 5/2; ЗП определяется по итогу собеседования; Официальное трудоустройство (белая заработная плата, оплачиваемые отпуска, больничные); После прохождения испытательного срока ДМС; 5 минут от м. Текстильщики; Компания внесена в реестр аккредитованных IT-компаний

-

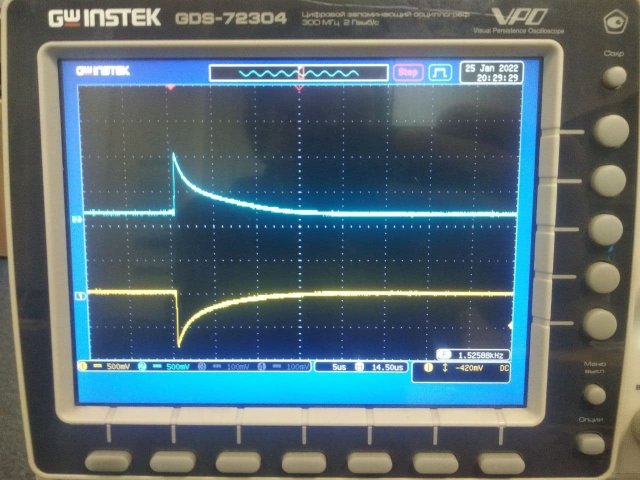

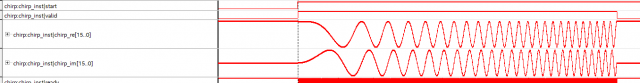

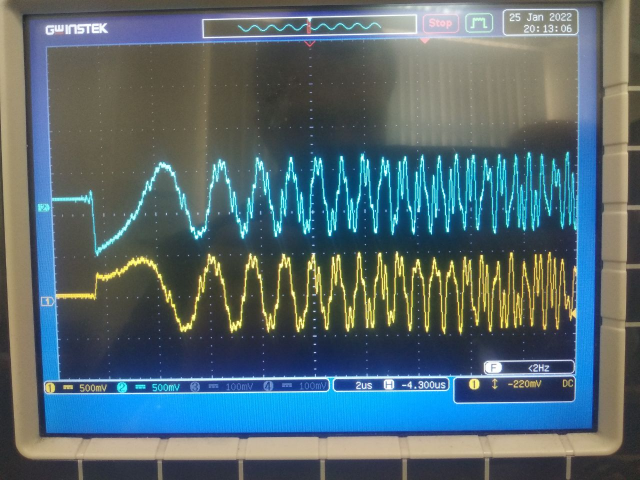

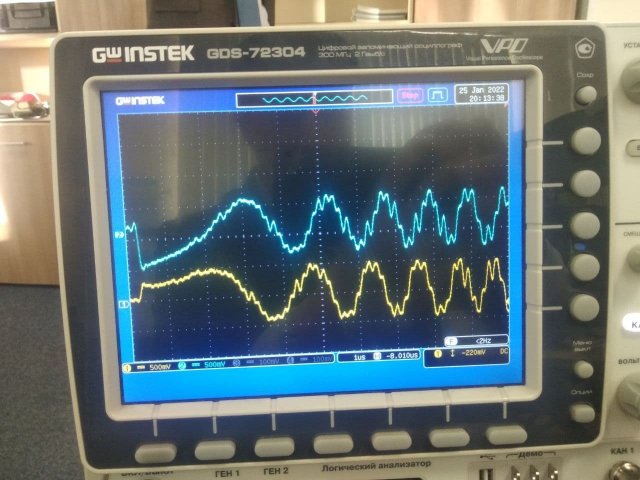

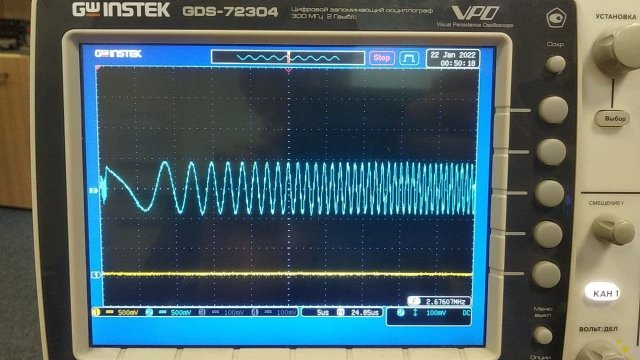

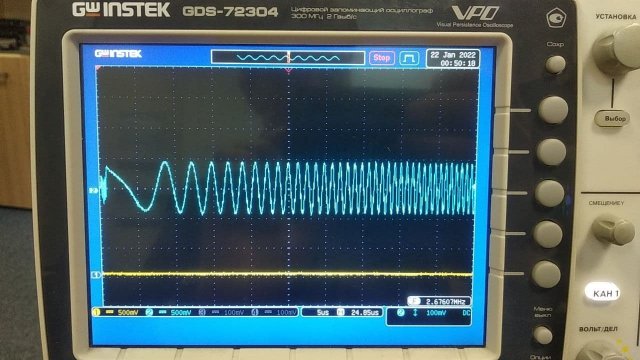

Здравствуйте, уважаемые форумчане необходимо генить синусоиду через ЦАП AD9122 на данный момент написан тестовый модуль, который генерирует ее вот в таком виде: Сделал IP модуль ЦАПа AD9122, который принимает 32х разрядные данные и затем в байтовом режиме выдает данные на ЦАП, причем реализацию сделал 2х модулей : 1. ALTDIO_OUT стоит только на данных, а DCLK и FCLK генятся через логику и выдаются на пинdac_ddr_phy_only_data_ddr.sv 2. ALTDIO_OUT стоит на данных, DCLK и FCLK, все тактируются от одного клокаdac_ddr_phy_all_ddr.sv написал констрейны: #************************************************************** # DAC_DDR #************************************************************** post_message -type info "READ dac_ddr.sdc" set dac_ddr_phy_clk { main_pll_inst|main_pll_inst|altera_pll_i|general[0].gpll~PLL_OUTPUT_COUNTER|divclk } set Tco_max 0.65 set Tco_min -0.05 post_message -type info "CLOCK_FREQ_DCLK_HZ = $dac_ddr_phy_clk" post_message -type info "Output Max Delay = $Tco_max" post_message -type info "Output Min Delay = $Tco_min" # Create the external virtual PHY clock create_generated_clock \ -name dac_ddr_dclk \ -source [get_pins "$dac_ddr_phy_clk"] \ [get_ports {DAC_DIC}] #*********************** OUTPUT ************************* set_output_delay -clock [get_clocks {dac_ddr_dclk}] -max $Tco_max [get_ports {DAC_D*}] set_output_delay -clock [get_clocks {dac_ddr_dclk}] -min $Tco_min [get_ports {DAC_D*}] #*********************** GROUP ************************* set_clock_groups -exclusive -group [get_clocks {dac_ddr_dclk}] все пины определены, как LVDS_E_3R в Quartus на Си реализовал HAL уровень dac_ad9122.rar функция инициализации: - spi_dac_ad9122_setup_nav - без фильтров - spi_dac_ad9122_setup - с фильтрами, пример от AnalogDevices проблема в том, что генится с ЦАП вот такой сигнал: При это я использовал код инициализации ЦАП, который рекомендован AnalogDevices с включенными фильтрами, если просто настроить на байтовый режим с выключенными фильтрами, то картинка вот такая: неясно откуда берется эта пила, скорее всего искажение данных, но в каких битах или порядке байтов не могу понять.... При этом в самой схемотехнике перепутаны диaпары данных и FCLK при подключении к ПЛИС, я это решаю для: - 1го варианта модуля инвертированием данных до ALTDDIO_OUT, FCLK просто инвертирую на выходе - 2го варианта модуля инвертированием данных и FCLK до ALTDDIO_OUT пробовал запускать тест, чтобы проверить принимаемые данные ЦАПом 1. если генить DCLK постоянно, а данные и FCLK подставлять, когда данные валидны, то выдаются ошибки постоянно во всех битах 2. если генить DCLK только в сопровождении валидных данных, то ошибок нет, даже когда посылаю 0x0 в ЦАП и в Im и Qre, а в COMPARE REG записаны допустим 0xaa55aa55, если подать верные данные, то таже тема Пробовал кидать одиночные данные и смотреть их прямо на выходе ЦАПа, то видно что выдаются 2а импульса, хотя данные посылаю 1 раз, при этом со времянкой все верно сделано Пробовал выдавать счетчик, который считает от 0 до 0хFFFF, потом сбрасывается и опять считает, на каждый канал Im и Qre, при этом вижу следующее на осциле: Без фильтров: c фильтрами: синий луч Im, желтый луч Qre Не понятно, почему вообще выдает не нарастание линейное, а резкий всплеск по амплитуде и угасание по экспоненте Бьюсь уже 2ю неделю, пока мыслей нет, в каком направлении двигаться Может есть у кого пример реализации.... Буду рад любой помощи, спасибо

-

Микросхемы памяти HyperRAM от Winbond

МакроГрупп опубликовал тема в Объявления пользователей

-

Всем привет! Artix7 Vivado 2019.1 Debian10 Собрал систему Axi Memory Mapped to Pci Express, CDMA, DDR3. Задача в том что бы посылать данные через PCIe в DDR с помощью DMA. В данный момент с ПК данные записываются в DDR ПЛИСа со скоростью 500Мб/с, что для заданных целей проекта мало. В ip PCIe у меня выделено 3 бара: DDR,BRAM, регистры CDMA. Всё прекрасно пишется и читается, но как я сказал выше, медленно. Так же в этой коре выделен один AXI BAR с адресом 0x40000000, который транслируется в адресное пространство CDMA как BAR0 PCIe'са и имеет адрес 0x60000000. Написал простенький дравер на линикс под данные цели, где заполняю регистры DMA. Адрес назначения = 0x80000000 (это адрес ddr в адресном пространстве cdma) и адрес источника который возвращает драйвер как выделенную память под dma, затем устанавливаю количество байт, что активирует трансфер из сорса в адрес назначение и в идеи данные из буфера выделенного драйвером в ПК должны появиться в ddr ПЛИС, но их там нет. Если сорс адрес ставить bram, то по той же схеме через драйвер, данные передаются из brem в ddr. Не могу понять что упускаю... pdf блок диаграммы, настройки и драйвей под линукс прикрепил. Можно попросить посмотреть файлы? Может кто нибудь подскажет что я не правильно делаю. PS не нашел ответов в и в Xilinx Answer 65062 AXI Memory Mapped for PCI Express Address Mapping design_1.pdf test_pci.c настройки и адреса.pdf

-

address_span_extender

Drakonof опубликовал тема в Работаем с ПЛИС, области применения, выбор

Всем привет, пожалуйста, уточните как работать с address_span_extender? Скажу сразу, я новичок. Есть DDR 1ГБ, у которой адресная шина 15 бит. Я полагаю что 2^15 = 32Кб = 8КБ. Окей, есть еще три бита выбора банка => 2^18 = 262Кб = 32КБ. Как мне адресовать весь гиг байт? Беру адрес_спан пишу что со стороны мастера мы можем адресовать 32б (это ширина авалона), а со стороны слэйва 15 + 3 = 18б (ширина шины адреса DDR + три бита выбора банков). Теперь вопрос, как мне двигаться по окнам памяти с помощью данного адрес_спан что бы адресовать всё пространство? PS. Читал даташит, смотрел видос, но как управлять этим ip я так и не понял. Может кто объяснит по человечески. Заранее спасибо!

.thumb.jpg.d0ede0a2f08d2628b97a8335de59a919.jpg)