Поиск

Показаны результаты для тегов 'vhdl'.

-

1. Главной проблемой была некорректная работа Hierarchy Updater’а: пока он не может корректно построить дерево проекта в тех местах, где в VHDL используются внешние модули (Verilog / IP-Core), но об этом я уже писал. 2. Для некоторых может быть непривычно и неочевидно, что (в строгом соответствии с VHDL’93) при использовании entity из библиотеки Work, необходимо указывать: library work; use work.all; 3. Несколько напрягает, что все справочные материалы на китайском. 4. Немного изменилась работа с атрибутами: для VHDL необходимо использовать Syn_* атрибуты (на 2023.1 достаточно было использовать PAP_* атрибуты – тогда было меньше warning/info о преобразовании Syn_* атрибутов в PAP_*). С другой стороны в ADS_Synthesis_User_Guide.pdf добавлено очень подробное описание правил применения Syn_* атрибутов с примерами на каждый случай. Но главной проблемой был п.1, т.к. приводил к падению Compile с «internal error» без объяснения причин падения. Отмечу, что Pango Micro старается сделать PDS/ADS лучше, с каждым шагом (2022.2-SP4->2023.1->2023.2-SP1) я отмечаю существенные сдвиги в лучшую сторону.

-

файловый ввод/вывод

hdus опубликовал тема в Языки проектирования на ПЛИС (FPGA)

library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity lab6 is generic(DATA_WIDTH : natural := 9); port ( side : in std_logic; step : in std_logic_vector(DATA_WIDTH-1 downto 0); vector : in std_logic_vector(DATA_WIDTH-1 downto 0); res_p, res_f : out std_logic_vector(DATA_WIDTH-1 downto 0) ); end entity; architecture rtl of lab6 is procedure inc_d_p( vector : in std_logic_vector; side : in std_logic; step : in std_logic_vector; signal result : out std_logic_vector ) is begin if (side = '0') then result <= std_logic_vector(signed(vector) - signed(step)); else result <= std_logic_vector(signed(vector) + signed(step)); end if; end procedure inc_d_p; function inc_d_f( vector : in std_logic_vector; side : in std_logic; step : in std_logic_vector ) return std_logic_vector is variable result : std_logic_vector(vector' range); begin if (side = '0') then result := std_logic_vector(signed(vector) - signed(step)); else result := std_logic_vector(signed(vector) + signed(step)); end if; return result; end function inc_d_f; begin inc_d_p(vector, side, step, res_p); res_f <= inc_d_f(vector, side, step); end architecture rtl; library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity lab6_tb is end entity; architecture rtl of lab6_tb is component lab6 is generic(DATA_WIDTH : natural := 9); port ( side : in std_logic; step : in std_logic_vector(DATA_WIDTH-1 downto 0); vector : in std_logic_vector(DATA_WIDTH-1 downto 0); res_p, res_f : out std_logic_vector(DATA_WIDTH-1 downto 0) ); end component; signal vector, step : std_logic_vector(9-1 downto 0); signal side : std_logic; signal p, f : std_logic_vector(9-1 downto 0); begin inst1: component lab6 generic map( DATA_WIDTH => 9 ) port map( side => side, step => step, vector => vector, res_p => p, res_f => f ); process is begin vector <= "110110001"; side <= '1'; step <= "000110101"; wait for 100 ps; vector <= "110111101"; side <= '1'; step <= "000110000"; wait for 100 ps; vector <= "101001001"; side <= '0'; step <= "000000110"; wait for 100 ps; vector <= "000001100"; side <= '1'; step <= "000001111"; wait for 100 ps; vector <= "001010101"; side <= '0'; step <= "000100001"; wait for 100 ps; vector <= "001110111"; side <= '1'; step <= "000000011"; wait for 100 ps; end process; end rtl; Первый раз работаю с файлами и не знаю как правильно это реализовать. Нужно при помощи Текстового редактора (Text Editor) инструментальной среды разработки ModelSim-Altera реализовать файловый ввод/вывод. Работа с файлами должна осуществляться в тестирующем модуле (TestBench) -

Москва (Московский), ищем в команду программиста ПЛИС

petrova_a опубликовал тема в Предлагаю работу

Компания, занимающаяся разработкой комплексных систем безопасности ищет в команду программиста ПЛИС. Конструкторское бюро расположено в Москва (г. Московский). Удаленный формат работы не рассматриваем. Основной функционал: Разработка и реализация на ПЛИС алгоритмов цифровой обработки сигналов в системах радиосвязи, радиолокации. Написание тестовых сценариев для верификации кода (моделирование и верификация). Организация внешних интерфейсов ПЛИС. Интеграция IP блоков сторонних разработчиков. Участие в разработке архитектуры и протоколов взаимодействия устройств. Разработка технических заданий для смежных разработчиков. Условия: Работа в технической компании. Оформление по ТК РФ. Обучение 100 % за счет компании. Возможность карьерного роста, смены вектора задач внутри направлений компании. Развитую корпоративную жизнь – проводим мероприятия обучающего, развивающего, спортивного, экстремального, творческого характера (приглашаем удаленных сотрудников погостить в головной офис г.Ставрополь). Соц.пакет для КБ разрабатывается. Узнать подробнее можно в личных сообщениях.- 2 ответа

-

- плис

- verilog hdl

- (и ещё 3 )

-

Поддержка VHDL в PDS/ADS от PangoMicro

makc опубликовал тема в Среды разработки - обсуждаем САПРы

Приветствую уважаемых участников форума! Внезапно выяснилось, что синтезатор ADS из комплекта PDS_2021.1 не поддерживает синтез VHDL от слова совсем. Проблема в том, что есть ряд старых отлаженных модулей, которые хотелось бы использовать без переписывания на Verilog/SystemVerilog и повторной отладки всего этого хозяйства. Как вы выходите из этого положения? Может быть есть хорошие (проверенные) конвертеры для маршрута VHDL=>Verilog? Пока нашёл маршрут конвертации с помощью ghdl и yosys, но ещё не пробовал. @Gas Wilson, обещают ли разработчики поддержку VHDL в будущих версиях ADS? Или может быть уже есть бета с такой поддержкой? PS: Проект собирается для Logos2 и поэтому, на сколько я понимаю, вариант откатиться на PDS с Synplify не подходит. Проверить пока не могу, т.к. работа идёт под Linux. -

Странное поведение Cyclone 4

AlexSailor опубликовал тема в Работаем с ПЛИС, области применения, выбор

Доброго времени суток. На днях приобрел отладочную плату RZ-easyFPGA A2.2 с кристаллом Cyclone 4 (ep4ce6e22c8n). Начав тестировать вводы-выводы элементарными программами, столкнулся с тем, что плата воспринимает элемент И как ИЛИ и наоборот. С чем это может быть связано? Спасибо. -

Есть желающие позаниматьтся с новичком?

Drakonof опубликовал тема в Предлагаю работу

Есть разработчики которым не лень позаниматься с новичком?Много уже чего прошел и изучил, но есть достаточное количество дырок в базе. В основном, больше нужно менторство и кодревью + подсказывать куда и как двигаться)По деньгам договоримся. -

VHDL счёт сбрасывается раньше времени

Sv37 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Здравствуйте! Проблема такая: есть код, смысл которого - поднять в единицу выходной сигнал и удерживать его в течение заданного времени(0.1, 1, 10 и 85 секунд, в зависимости от входящего сигнала). Всё запускается и правильно работает в симуляторе, но в железе выходной сигнал сбрасывается до того, как достигается заданное время(0.1с = 0.1с, 1с = 0.77с, 10с = 9.9с, 45с = 32с, 85с = 65.5с). Тестировалась на Cyclone IV и II - результат одинаков. Я новичок в этом деле, подскажите, что я упускаю из виду? --**Модуль обеспечивает заданное время исследования. --С компьютера приходит команда, задающая необходимую продолжительность --исследования, данный модуль обеспечивает это время.** library ieee; use ieee.std_logic_1164.all; entity Int_former is port (clk_1kHz : in std_logic; res_enable : in std_logic; --запуск отсчёта времени измерения time_set : in std_logic_vector(1 downto 0); --заданное время измерения cnt_enable : out std_logic); --сигнал разрешения исследования end Int_former; architecture Count of Int_former is begin Counting: process (clk_1kHz, res_enable, time_set) is variable res_time : integer range 0 to 100000 := 0; --время исследования variable msec : integer range 0 to 100001 := 0; --отсчёт времени исследования в милисекундах variable r_enable : integer range 0 to 1 := 0; --дублирование res_enable, которым можно управлять variable sync : integer range 0 to 1 := 0; --синхронизация счёта с clk begin --установка времени исследования в секундах if time_set = "01" then res_time := 100; end if; --0.1 секунды if time_set = "10" then res_time := 1000; end if; --1 секунда if time_set = "00" then res_time := 10000; end if; --10 секунд if time_set = "11" then res_time := 85000; end if; --85 секунд if rising_edge(res_enable) then r_enable := 1; end if; if rising_edge(clk_1kHz) then if r_enable = 1 then msec := msec + 1; sync := 1; end if; --счёт времени исследования по фронту тактовой частоты end if; if (msec < (res_time + 1) and sync = 1) then cnt_enable <= '1'; else cnt_enable <= '0';end if; --если время меньше заданного, то выходной сигнал в высоком уровне if msec > res_time then msec := 0; sync := 0; r_enable := 0; end if; --сброс всего по достижении заданного времени end process Counting; end Count; -

На сайте компании Xilinx размещена для скачивания версия среды разработки для ПЛИС и СнК Vivado под номером 2021.1. Подробнее

-

- vhdl

- fpga xilinx

-

(и ещё 2 )

C тегом:

-

В данном вебинаре вы познакомитесь с основными особенностями нового поколения адаптивных систем Versal, с тем, какие среди них существуют вариации и в каких сферах их применение принесёт максимальную пользу. Подробнее

-

- плис

- fpga xilinx

- (и ещё 7 )

-

Всем привет. Мы проводим стримы по FPGA/ПЛИС тематике на твиче по адресу twitch.tv/fpgasystems Обычно, это среда и суббота в 20:00. Записи прошедших стримов лежат на youtube: youtube.com/c/fpgasystems Ждём Вас на стриме. Анонсы предстоящих эфиров в группе в телеграм @fpgasystems (https://t.me/fpgasystems) и VK и FB

-

Добрый день всем. Создаю один проект на больших скоростях и мне там необходимо складывать и накапливать большие значения (разрядность вектора более 50). Естественно проседает быстродействие и необходимо ввести латентность на сумматоре (хотя бы 2). На вход сумматора подаётся значения, которые изменяют по линейному закону с каким-то произвольным коэффициентом. Например входные данные могут быть 1,2,3,4,5 и т.д. А на выходе соответственно получаем 1,3,6,10,15. Схема классическая: выход сумматора падает на вход регистра, а его выход на второй вход сумматора. Регистр может инициировать любым значением перед началом работы. Классический аккумулятор! Есть варианты по добавлению второго сумматора для параллельного счета, но пока не удается засунуть его так, чтобы все работало. У кого-нибудь есть мысли, как увеличить быстродействие??

-

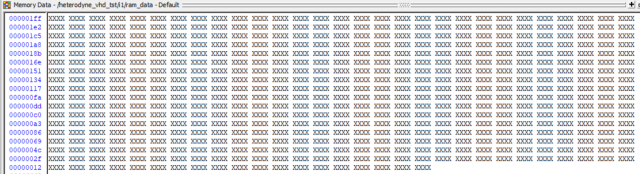

Всем привет! Следующая проблема, я пытаюсь инициализировать память с помощью атрибутов: type memory is array (511 downto 0) of std_logic_vector (15 downto 0); signal ram_data: memory; attribute ram_init_file : string; attribute ram_init_file of ram_data : signal is "mem.mif"; Он синтезирует память со следующими параметрами: Info (12133): Instantiated megafunction "altsyncram:ram_data_rtl_0" with the following parameter: Info (12134): Parameter "OPERATION_MODE" = "ROM" Info (12134): Parameter "WIDTH_A" = "16" Info (12134): Parameter "WIDTHAD_A" = "9" Info (12134): Parameter "NUMWORDS_A" = "512" Info (12134): Parameter "OUTDATA_REG_A" = "UNREGISTERED" Info (12134): Parameter "ADDRESS_ACLR_A" = "NONE" Info (12134): Parameter "OUTDATA_ACLR_A" = "NONE" Info (12134): Parameter "INDATA_ACLR_A" = "NONE" Info (12134): Parameter "WRCONTROL_ACLR_A" = "NONE" Info (12134): Parameter "INIT_FILE" = "mem.mif" И все было было бы хорошо, но в ModelSim вижу следующее: Если задать память через мегафункции и там прописать файл инициализации, то все хорошо, но мне надо научиться через атрибуты. В чем проблемы? Вот все библиотеки: library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; use ieee.math_real.all; LIBRARY altera_mf; USE altera_mf.altera_mf_components.all; library altera; use altera.altera_syn_attributes.all;

-

Здравствуйте, подскажите, как в проекте сделать так, чтобы тестбенч для верхнего уровня читал данные из файла в модуль нижнего уровня. Не делая выводы в модeле top? Либо можно как-то пометить выводы верхнего уровня, чтоб при имплементации не выдавало ошибок об отсутствии пинов для данных выводов?

-

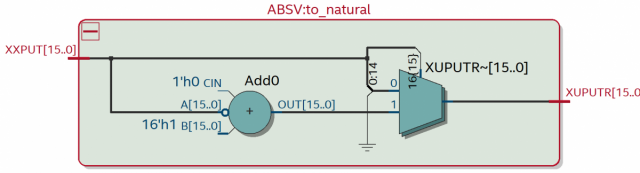

В своей деятельности частенько сталкивался со странными ситуациями, когда привычные приёмы не срабатывали. Особенно когда сущности разрастались до размеров больше страницы. Погоня за результатом и инженерный азарт давал энергию на отработку локальных частностей. Перебор вариантов описания одного и того-же в конце срабатывал и не было особо времени разобраться досконально. Вот и теперь, казалось простая задача, но... все стало на свои места, когда выделил отдельной сущностью, которую прицепил к основному тексту и все стало так как хотел! Этот фрагмент имеет отношение к теме --взятие абсолютного значения знакового числа library IEEE; use IEEE.STD_LOGIC_1164.all; use IEEE.numeric_std.all; entity ABSV is generic(bit_num: integer:=16); port( CLK : in STD_LOGIC; XXPUT :in STD_LOGIC_VECTOR(bit_num-1 downto 0); clken : in STD_LOGIC; XUPUTR :out STD_LOGIC_VECTOR(bit_num-1 downto 0)); end entity ABSV; architecture beh of ABSV is begin process (CLK) begin if CLK='1' and CLK'event then if clken = '1' then if XXPUT(bit_num-1) = '1' then XUPUTR<= std_logic_vector(to_unsigned(to_integer(unsigned(not XXPUT )) + 1, bit_num)); else XUPUTR<= XXPUT; end if; end if; end if; end process; end architecture beh; Конфликт IEEE.STD_LOGIC_ARITH.all; с IEEE.numeric_std.all; ставил преграды! И тут вспомнились ВСЕ подобные ситуации... Отсюда вывод,- крошите ваше написание VHDL на более мелкие сущности! Будет больше экономии времени..

-

vhdl Помогите проредить входной сигнал нулями

venik опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Нужно проредить входной сигнал нулями. Вот что первое пришло в голову. library ieee; use ieee.std_logic_1164.all; entity maper is port ( din : in std_logic; clk : in std_logic; res : in std_logic; en : in std_logic; en_out : out std_logic; dout : out std_logic_vector (15 downto 0) ); end maper; architecture behavioral of maper is signal dout_tmp : std_logic_vector(15 downto 0); signal cnt : std_logic := '0'; begin process (clk) begin if clk='1' and clk'event then if res='1' then dout_tmp <= (others => '0'); cnt <= '0'; elsif en='1' then cnt <= not cnt; if cnt = '0' then dout_tmp <= din; else dout_tmp <= (others => '0'); end if; end if; end if; end process; en_out <= en; dout <= dout_tmp; end behavioral; Как правильно это сделать? -

Реализация счетчика нажатия клавиш ps2

Olena03 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Помогите найти ошибку в реализации кода. Был создан драйвер клавиатуры(ps2), который, помимо нажатия клавиши, фиксирует "динамику присоединения", то есть к каждой клавише должно дополнительно указываться время, когда она была нажата, и как долго длилось нажатие, пока следующая клавиша не была нажата, и помещена в память. В качестве идентификатора клавиш сохраняется ASCII-код каждой кнопки. Весь реализованный код с таймером находится в приложении. --значение таймера сохранить в array if(zeile=0 and spalte <19) then --ряд = 0, столбец <19 matrix(zeile, spalte) <=x"01"; --ряд, столбец zeile<= zeile+1; --идентифицирует, что значение таймера было в Array сохранено timer1<='1'; timer2<='0'; in_array_gespeichert<='0'; matrix(1,0)<=ascii; -- zeile2<=zeile; -- spalte2<=spalte; ar_ps2 <= matrix(0,0); ar_ps2 <= matrix(1,0); ar_ps2 <= matrix(2,0); zeile<= zeile+1; --ряд +1 else spalte <= 0; matrix(zeile, spalte)<=x"02";-- X"02" -держатель места; ряд, столбец end if; state <= output; array_test<='0'; ELSE if(spalte <19 and zeile=2) then matrix(zeile, spalte)<=x"11"; -- 2-е значение таймера. X"11" -тут как держатель места; timer2<='1'; timer1<='0'; in_array_gespeichert<='1'; --сохранено в Array zeile <=0; spalte<=spalte+1; end if; array_test<='1'; state <= ready; END IF; debounce.vhdl -

Покрытие кода для FPGA

MaratZuev опубликовал тема в Среды разработки - обсуждаем САПРы

Добра всем! Поискал в форуме в разных ветках, но сразу не нашёл ответа на такой вопрос: поставлена задача для наших проектов доказать соответствие оных директивам DO-254 и иже с ними. Проекты написаны как на VHDL и Verilog (SV), так и в схематике. Причём ПЛИС Actel и Altera. Вопрос: откуда нам, первый раз столкнувшимся со словами Code Coverage, начать сей нелёгкий и тернистый путь? Всё комментарии, а тем паче, ссылки, книги и прочее, приветствуются. Оптимально Mentor (ModelSim и QuestaSim), но и Aldec пойдёт, если он умеет это лучше.- 16 ответов

-

- mentor grapics

- modelsim

-

(и ещё 3 )

C тегом:

-

-

Синтаксис vhdl

grafng опубликовал тема в Языки проектирования на ПЛИС (FPGA)

https://github.com/MadLittleMods/FP-V-GA-Text/blob/master/vgaText/vgaText_top.vhd (справочник по vhdl есть) помогите , растолкуйте что значит точка в drawElementArray(i).pixelOn что оно вообще такое , как работает (если это важно разрабатываю vga контролер для древней spartan3e kit , гитхаб не мой , пытаюсь разобраться с выводом текста) -- Text Draw Stack ----------------- for i in drawElementArray'range loop if drawElementArray(i).pixelOn then rgbDrawColor := drawElementArray(i).rgb; end if; end loop; -

VHDL alias

alexadmin опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Вопрос традиционно для тех, кто полностью скурил стандарт. Есть, к примеру, порт : CTRL : inout STD_LOGIC_VECTOR(31 downto 0); Далее я могу написать alias MY_CTRL : std_logic_vector(2 downto 1) is CTRL(23 downto 22); А хочется написать что-то типа alias MY_CTRL : std_logic_vector(2 downto 1) is (CTRL(23), CTRL(19)); Но аггрегация здесь, похоже, не поддерживается (да наверное и не должна, если подумать о том, что такое массив). Но тем не менее хочется. Понятное дело, можно разбить MY_CTRL на отдельные скалярные элементы MY_CTRL_1 и MY_CTRL_2, но некрасиво. Можно MY_CTRL сделать сигналом. Но тогда про двунаправленность придется забыть и при назначении всякий раз думать вход это или выход. Еще идеи?