_LD

Участник-

Постов

54 -

Зарегистрирован

-

Посещение

Весь контент _LD

-

Подскажите контрактное производство

_LD опубликовал тема в Пайка и монтаж

Коллеги, добрый день. Подскажите, существуют ли такие контрактные производства, которые смогут сами закупить комплектующие, спаять платы и осуществить запуск/регулировку? Платы разные, цифра/аналог, довольно сложные. Нужна обязательно отечественная контора. Заранее спасибо! -

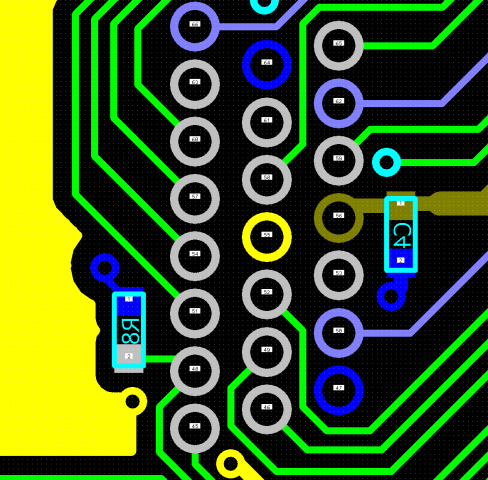

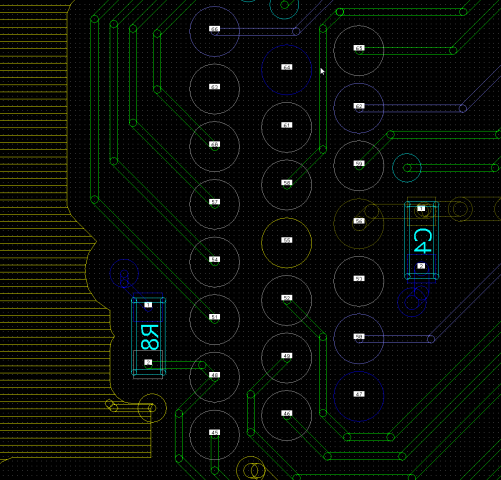

Коллеги, добрый день. Два вопроса по Allegro PCB Editor (17.2, если это имеет значение): 1. Можно ли настроить режим выделения объектов мышью таким образом, чтобы выделялось только то, что _полностью_ попадает в окно выделения? Сейчас выделяются также и все объекты, которые помещаются в область выделения лишь частично. 2. Есть ли аналог P-CAD-овскому режиму отрисовки "DRAFT MODE" - когда рисуются лишь контуры объектов. Встроенные режимы прозрачности в силу разных обстоятельств не очень радуют. Заранее спасибо за ответы!

-

SD карта to МК или ПЛИС

_LD ответил Freibier тема в В помощь начинающему

Посмотрите на MAX13035EETE+ -

СПб - ищем схемотехников и программистов

_LD опубликовал тема в Предлагаю работу

Здравствуйте, уважаемые форумчане! В команду требуются разработчики, ищем специалистов в следующих областях (разработка спецтехники): - разработка схемотехники цифровых устройств – FPGA, DSP, PCIE, SRIO, Ethernet, JESD204; - разработка ПО для FPGA (Xilinx, стык с АЦП/ЦАП, ЦОС, интерфейсы); - разработка ПО для DSP; - разработка ПО для ARM (в т.ч. Embedded Linux); - разработка схемотехники аналоговых СВЧ-устройств (частотно-избирательные цепи на распределенных эл-тах, усилители мощности AB-класса, ЭМС). Зарплаты определяются по результатам собеседования (ориентировочно для первых двух категорий 110 – 170 т.р. на руки). Условия работы – полная занятость, оформление по ТК РФ. http://www.nppntt.ru/ Территориально – СПб, ст. м. Академическая Контакты: Веженков Денис +7 911 294 16 64, звонить с 10 до 17 часов. [email protected] -

Было такое в версии AHDL 8.3. Руками поправил файл .adf в папке проекта. Подробностей не помню.

-

http://www.masterkit.ru/main/set.php?code_id=221247

-

Схема в OrCAD => Плата в PCAD (forward annotate)

_LD ответил minimumlaw тема в Cadence

использую Orcad 9.1 и PCAD2006. При экспорте указываю tango.dll Только танго в оркаде какое-то не такое, поэтому в получившемся удаляю оркадовские строчки с заголовком и дублирую одну из строк в описаниях компонента. было [ C1 C_0402 1.0 ] стало [ C1 C_0402 C_0402 1.0 ] При импорте полученной танги в Pcad {Value} проставляется правильно. -

Чудеса технологии

_LD ответил des00 тема в Среды разработки - обсуждаем САПРы

Я там уже был, правда, достаточно давно :) Тут с тех пор, наверное, ничего и не поменялось... -

Кто работал с AD9957?

_LD ответил _sda тема в Цифровые схемы, высокоскоростные ЦС

Своя плата, четыре слоя, управляю от FPGA. Сначала сделал отдельные LDO для каждого из питаний, но не предусмотрел управление включением этих стабилизаторов. Во второй версии платы завел сигналы управления каждым стабилизатором. Занчит, проблемы были и с использованием BFI-интерфейса. Я хотел попробовать использовать его, да руки не дошли. А что было сделано, чтобы палки ушли? Просто поставлены LDO и сделана другая разводка? Пришел ответ от саппорта, очень короткий. "Hello, do you see the same bahavior with an other AD9957? Please verify this with a second part. best regards Bernhard" вот так :) Сегодня заменил микросхему, и это действительно помогло. Изначально были сделаны две платы, обе глючили. Потом были сделаны еще две платы с управлением питанием, которые глючили, пока я не подобрал "правильную" последовательность включения питания. Далее изготовили еще 12 плат, две из которых глючили несмотря ни на что; в одной из них я сегодня заменил микросхему, и это помогло. Переписка с саппортом, возможно, продолжится. О результатах напишу здесь. -

Кто работал с AD9957?

_LD ответил _sda тема в Цифровые схемы, высокоскоростные ЦС

Возобновлю тему. Наткнулся на проблему, описанную в предыдущем посте. Режим микросхемы - QDUC, на спектраче лишние палки, на осциллографе сигнал с АМ, которой не должно быть. Ощущение, что микросхема "теряет" одну квадратуру. Происходит это не всегда, иногда включишь - все хорошо; иногда - плохо. Если глюк проявился, то никакие манипуляции (все виды сбросов, перезапись конфигурации) не помогают, может помочь лишь полное снятие всех питаний. От порядка включения питаний все это зависит, но мне не удалось подобрать истинную последовательность. Как бы не сделал, все равно - хоть с 20-го включения, но заглючит. Коллеги, у меня просьба - отпишитесь, если имели с ней дело, даже если она у вас работает исправно. Мне нужно понять - это только у меня так, или через это прошел кто-то еще. Может, есть какой рецепт? В поддержку написал, жду ответа. Заранее благодарен за содействие. -

Интерфейс Е2

_LD ответил kuzis тема в ISDN/G.703/E1

Какое-то время назад использовали XR-T5683A. -

Схемотехника и алгоритм работы видеоэкрана

_LD ответил picman тема в В помощь начинающему

Китайские товарищи вовсю используют гигабитный ethernet, а я не захотел:) В небольших поделках - манчестер 8 мбит по витой паре, в больших - 100 мбит ethernet. Уже сменил род деятельности. Задолбало лампочками управлять :) Но несколько лет просидел на этом. Если быстродействие памяти и требуемые параметры позволяют - делаю "в лоб", вычитывая каждый раз значение яркости. Если поджимает - делаю смешанный вариант (младшие разряды стробом, остальные вычитыванием). Асинхронную статику Samsung. Именно так. Конеюно, двухпортовая. Если два полных кадра в ПЛИС не лезут, идет прием во внешнюю память с перебросом ее во внутреннюю при смене кадров. -

Схемотехника и алгоритм работы видеоэкрана

_LD ответил picman тема в В помощь начинающему

Да. Все зависит от размерности управляемого объекта. Если два полных кадра лезут в память ПЛИС - нафига внешняя память? А вот если не лезут, то приходится ее ставить. Память ПЛИС может быть организована не байтами. Можно хоть 13 бит без потерь сделать :) 12 бит в Альтере - три блока памяти разрядностью 4 бита. А если память внешняя, то ее обычно дофига, и не проблема потерять четверть 16-ти битного слова. -

Схемотехника и алгоритм работы видеоэкрана

_LD ответил picman тема в В помощь начинающему

Главное - изначально продумать иерархичную наращиваемую систему. Все остальное приложится :) Синхронизация модулей не нужна, правда, у меня она всегда получалась автоматически. Минимальная частота кадров - порядка 75 герц, но нелишним будет задрать ее до нескольких сотен герц. У китайских товарищей в основном 200-300 герц. Лично я использую драйверы MBI5026 и ПЛИС Альтера (Циклон1/2), которая тянет модули размерностью порядка 64 на 32 полноцветные точки. Обычно хватает внутренней памяти, но иногда приходится ставить внешнюю. Да, глубина цвета (разрядность ШИМ), что выбрана Вами (8 бит - 256 значений), абсолютно неприемлема (проблемы с воспроизведением "темных" полутонов). Минимум - 10 бит; опять-таки, у китайцев от 12 до 14 бит. Я делал не менее 12 бит для статической индикации. Будут вопросы - милости просим. -

CF глючит - запарился уже

_LD ответил Foxx тема в IDE/ATA/SATA/SAS/SCSI/CF

Были глюки чуть другого характера, но тоже проявлялись лишь на Transcend 80x. У меня, правда, с ней работала ПЛИСина, но не важно. Я формировал срез сигналов CE и OE одновременно, поскольку в спецификации указано, что сетап одного относительно другого 0 нс. Все это работало на разных карточках, пока не попалась Transcend 80x - ей такое обращение не понравилось. Были очень "хитрые" глюки, сейчас не вспомню, какие именно. Пришлось чуть подвинуть срез ОЕ, сделать его попозже. Может, мой опыт пригодится. -

Моя переписка с Альтерой по этому поводу ************************************************* Request No: 10563516 Status: Closed Date Opened (PDT): 10/9/2006 05:48 PM Date Closed (PDT): 10/20/2006 02:11 AM Device Family: CYCLONE II Device: EP2C5Q208I8N Request Title: Quartus II Synthesizer ignores carry chains for Cyclone II family Steps to Reproduce / Description: My software is Quartus II build 202 SP1 I have written the simple AHDL module (the 8-bit comparator) (AHDL text placed at the end of the letter). When I try to implement this module into Cyclone II device (e.g. EP2C5), the Quartus II Synthesizer reports me that "Ignored 8 CARRY buffer(s)", and the fitter builds the logic without carry-chain. When I try to implement this module into Cyclone or Acex1K device, the synthesizer accepts my logic "as is", i.e. builds the carry-chain logic. In the project option/assignments I change ONLY target device. If I try to implement a simple LPM_COUNTER instead of my module with the same options in the same project, the synthesizer and fitter implement the carry-chain independently of device family. How can I force the Quartus II software to build the carry-chain logic in my module? Thank you in advance. subdesign cmp_8 ( A[7..0] : input; B[7..0] : input; EQ : output; ) variable cry[7..0] : carry; begin cry[].in = ( A[] !$ B[] ) & (Cry[6..0].out, vcc); EQ = cry[7].out; end; ****************************************************** 10/10/2006 01:27 AM To Customer Hi, This is a software bug. It will be corrected in the future release. You could implement a comparator in Verilog/VHDL, but whether the comparator use carry chain or not dependent on the comparator writing style. Please refer to a comparator example in attachment. Best regards, Harold module carrychain(input [7:0] a,input [7:0] b, output eq); wire [8:0] c; assign c = {1'b0,a} - {1'b0,b}; assign eq = c[8]; //assign eq = (a==B); //this kind of style is not using carry chain,but implemented in more less LEs. endmodule ************************************************************ 2/18/2007 09:58 PM To Customer Hi Dmitry, Thanks for using MySupport. I have searched the related database. It is a regret that this issue is not in top priority since Verilog and VHDL have supported carry chain implementation. If the carry chain block is just a sub-module in your whole design, you could use Verilog/VHDL for this sub-module, and Quartus II can support mixed language. Thank you and have a nice day. Best Regards, Amanda ************************************************************ 2/19/2007 03:14 PM From Customer You wrote: > It is a regret that this issue is not in top priority since Verilog and > VHDL have supported carry chain implementation Not quite :( The new example (verilog) is placed at the end of the letter. When I fit this module into Cyclone device, Quartus II builds carry-chain; when I change the target device to Cyclone II, Quartus II ignores carry-chain. This module is the fast multiplexer. I want that this module work AS FAST AS POSSIBLE (i.e. with carry!!!). AS I WROTE on Verilog and AHDL! No pipeline is possible. No additional LCELLs are possible. This is offensive that your device (Cyclone II) can give me that I want (according to datasheet), but your software can't properly implement my simple construction into Cyclone II chip. How can I get WHAT I WANT, by means of ANY language? module mx_4_1 ( input [3:0] D, input [3:0] Sel, output O ); wire [3:0] Si; wire [3:0] Ci; wire [3:0] Co; wire [3:0] So; carry_sum Cry0 (.sin(Si[0]),.cin(Ci[0]),.sout(So[0]),.cout(Co[0])); carry_sum Cry1 (.sin(Si[1]),.cin(Ci[1]),.sout(So[1]),.cout(Co[1])); carry_sum Cry2 (.sin(Si[2]),.cin(Ci[2]),.sout(So[2]),.cout(Co[2])); carry_sum Cry3 (.sin(Si[3]),.cin(Ci[3]),.sout(So[3]),.cout(Co[3])); assign Si[2:0] = 0; assign Ci[3] = 0; assign Ci[0] = D[0] & Sel[0]; assign Ci[1] = (D[1] & Sel[1]) | Co[0]; assign Ci[2] = (D[2] & Sel[2]) | Co[1]; assign Si[3] = (D[3] & Sel[3]) | Co[2]; assign O = So[3]; endmodule ************************************************************ ****** 2/20/2007 11:54 PM To Customer Hi Dmitry, I am sorry for the last confused reply. With the codes you sent, I can reproduce the issue you mentioned. After discussing with related people. This issue is caused by two reasons. One is software reason, and a new bug report has been issued. It is planed to fix in Quartus II 7.2. Another is the hardware reason ---- the different structures between Cyclone and Cyclone II. In fact, Cyclone’s carry chain has better performance than Cyclone II’s. This is a known issue of Cyclone II. For more information about the carry chain, you could refer to the following links: Page 6~7 of http://www.altera.com/literature/hb/cyc2/cyc2_cii51002.pdf page 8~10 of http://www.altera.com/literature/hb/cyc/cyc_c51002.pdf You can see that the carry chain in Cyclone II is shorter than the one in Cyclone device. It makes software difficult to implementing carry chain in Cyclone II. If carry chain is a very important feature of your design, we suggest you to use Cyclone device. Sorry about this confusion, and thanks a lot for notifying us about this. Currently, there is no workaround in Cyclone II. If you encounter difficulty to meet performance of your deisgn, we can help you from other aspects. For doing this, we need the project file and the performance requirement. Best Regards, Amanda ************************************************************ ****** 2/21/2007 03:24 PM From Customer Hi Amanda, Thank you for elucidation. Now I know that this problem can't be solved using current version of Quartus II, independently of language I write... >You can see that the carry chain in Cyclone II is shorter than the one in >Cyclone device. The length of carry-chain is not so important, I seldom use >16. Possibility of use the carry-chains where I want - that is just the point. I'll be waiting for new release of Quartus II software. Best Regards, Dmitry ************************************************************ ****** 2/21/2007 07:01 PM To Customer Hi Dmitry, You are right that the length of carry chain is not the excuse of the software issue. But it is the cause of the bug. Related people are working on it. The fix is planned in Quartus II 7.2. I will set close-pending for this SR, and it will be closed in couple of days if without update. If you have other questions regarding our products, please issue a new one, and a right people will work with you. Thank you and have a nice day! Best Regards, Amanda

-

У тебя будет нечто худшее, чем наклон - будет излом букв на границах модулей. Это в случае вертикальной развертки (одновременно светится горизонтальный ряд). В случае горизонтальной - не знаю, не делал, но, возможно, будет еще хуже, опять же на границах модулей. Все эти эффекты можно попробовать забороть задиранием частоты развертки до ~килогерц, и, соответственно, многократным повторением одной и той же информации перед очередным сдвигом, чтобы "бег" строки не был слишком быстрым. здравая мысль. Такой способ обновления (с повтором одинаковых кадров несколько раз на частоте развертки ) приводит к "двоению-троению" букв и не очень хорошо смотрится. Никаких глюков - все работает :) Для динамической индикации наклон не считается глюком, он даже добавляет некий шарм. Тут говорили про тени - это строковые ключи не успевают закрываться, нужен dead-time при выводе. Для статической индикации и так все хорошо. Делал разные строки, как статику, так и динамику, везде рефреш 75 Гц, скорость обновления всегда такая же, т.е. текст всегда едет со скоростью 75 точек в секунду или кратно выше, везде дабл-буфферинг. Простыми строчками (типа 8x128 без градаций яркости) рулит Мега128, сложными (с градациями яркости и показом мультиков) рулит та же мега в соавторстве с двумя или более плисинами.

-

Вопрос по 485 интерфейсу

_LD ответил ups тема в RS232/LPT/USB/PCMCIA/FireWire

Кто мешает проверить? Приемник, передатчик, бухта кабеля, осциллограф :) Думаю, оно будет работать. Согласовать только не забудь. UTP 5 категории (обычный, тот, чем локалки крутят) имеет волновое 100 ом. Если передача в одну сторону, то терминатор (100 ом) только на приеме, если двунаправленная, то с каждой стороны по 100 ом. RJ45, разумеется, подойдет. ЗЫ. У меня работало на 4 МГц на 10 метров. Микросхемы - ADM3485EAR. -

Синхронизация большого количества микросхем

_LD ответил ups тема в В помощь начинающему

Мне почему-то думается, что в этом случае вовсе не нужно данные по 4 каналам гнать - достаточно одного. Будет 57600 Гц :) Я гоняю 20 МГц. При плохой разводке (плохая земля, множественные разветвления тактового сигнала) можно огрести "звон" на любой частоте передачи - хоть на 1 Гц. Возможность получить проблемы зависит от длины проводника и от быстродействия микросхемы, а не от скорости передачи. Микросхемы рассчитаны на десятки МГц. -

Синхронизация большого количества микросхем

_LD ответил ups тема в В помощь начинающему

Тактовые сигналы (clock, latch) - иерархично. Я делаю так: clock от контроллера проходит через всю плату по прямой, попутно подаваясь на триггеры Шмитта 74AC14 (равномерно расставленные по плате) отводами минимальной длины (количество элементов на всю линию 8..16), выход каждого из этих элементов идет через всю плату поперек, проходя через ножки clock драйверов (количеством до 8). Про линии данных разговор особый. Конкретная реализация зависит от... Вы не указали конфигурацию табло и иерархию подключения микросхем по линиям данных (длина цепочки обратно пропорциональна скорости обновления информации). Между платами я стараюсь использовать симметричные интерфейсы (RS485), дабы не умереть на помехах и звонах, которых в таких системах предостаточно. Если количество сигналов большое - получается попадалово по стоимости, поэтому я стараюсь ставить контроллер либо на саму плату индикации, либо вторым этажом на нее же, тогда идут обычные LVCMOS сигналы, "прочищенные" теми же AC14 на приеме. Однако мне доводилось видеть дисплеи, в которых между платами тянется обычная "цифрА" посредством плоского кабеля. Я опасаюсь таких решений, ибо лицезрел, что творится межу землями двух плат индикации, даже если они стоят рядом. -

Дополню своим опытом. Манчестер, 4 Мбит в сек, ADM3485E, все замечательно работает на ~5 метров по проводу, которым обычно бытовые приборы в сеть включаются :) Соответственно, не витой, терминаторы с обеих сторон по 100 ом (от фонаря). На бОльшие расстояния применяем витуху 5-ой категории. Максимум, что проверяли - 15 метров на 4 Мбит. Оно работает и на 8 Мбит, длину более 1 метра не проверял пока. RS485 рулит :)

-

Модерирование сумматора

_LD ответил Ketzer тема в Среды разработки - обсуждаем САПРы

но сам-то сумматор на AHDL? parameters ( width= 15 ); Subdesign adder ( A[Width-1..0]:input; B[Width-1..0]:input; C[Width-1..0]:input; ) begin C = A + B; end; создаем символ, вставляем его в .gdf и видим квадратик с параметром width. Я на тот вопрос ответил? :) -

ГОСТЫ и OrCad :angry2:

_LD ответил yrbis тема в Вопросы системного уровня проектирования

Может, Вы раскроете эту страшную тайну, тщательно скрываемую разработчиками пакета оркад? :))) разработчики ни при чем. так получилось :) http://electronix.ru/forum/index.php?showt...5403entry5403 -

ГОСТЫ и OrCad :angry2:

_LD ответил yrbis тема в Вопросы системного уровня проектирования

Неправда ваша. Можно сделать автомат по ГОСТу, но метод не совсем "прозрачен". Процесс занимает около минуты :) -

Информация об основах телефонии.

_LD ответил zheka тема в Вопросы аналоговой техники

нафига тебе развязка, если ты это собираешься от линии питать? :) Забудь. Мощности того, что дает станция в режиме разговора, не хватит. Запитать контроллер - пожалуйста. Подключенных к этой же линии? Не получится однозначно. Даже если применишь источник питания для вызова, спалишь станцию :) Да, и вопрос. Зачем тебе ГЕНЕРИТЬ DTMF? Тебе его анализировать нужно.